笔者在多通道无源雷达信号处理机的设计中,采用了DSP芯片TMS320VC5409控制4片DDC芯片HSP50214B的接口电路,研究了同步控制多片HSP50214B等关键技术。

DDC芯片HSP50214B

数字下变频器HSP 50214B是一个非常灵活的数字调谐器,是INTERSIL公司为了满足一个宽范围的通信商业标准要求而设计的,主要用于软件无线电中A/D后的处理。HSP50214B 的下变频处理功能是将被抽样的中频信号转变成基带数字抽样信号,完成该功能的模块包括本振产生器(NCO),积分梳状滤波器(CIC),多级半带滤波器(HB)以及可编程有限脉冲响应滤波器(FIR),具有重复抽取,自动增益控制,频率鉴别,以及多片同步检测等功能。如果将HSP50214B和一个DSP处理芯片直接连接就可以传递和处理数字基带信号和状态数据。可编程下变频器HSP50214B能够将数字化的中频数据转变成能够被标准的DSP微处理器处理的基带数据。

多片DDC与DSP接口电路

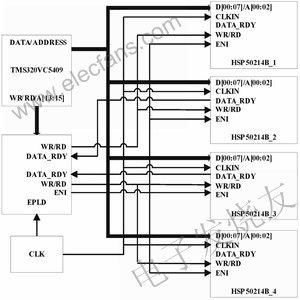

HSP50214B的配置通过DSP对其内部控制字操作来实现,共有255个32bit的控制字可以分别控制HSP50214B的输入、抽取、滤波、输出格式等环节。通过地址线A0-A2和数据线 D0-D7,可以实现对其内部控制字的读写操作,如图1所示。

图1 HSP50214B和DSP接口电路

四片HSP50214B的8位数据线同时占用DSP数据线的低8位,3位地址线同时占用DSP地址线的低3位。由于HSP50214B没有读写寄存器片选信号,因此需要利用DSP的读写信号RD/WR和高位地址线A15-A14位,并由EPLD对其进行译码分别控制四片HSP50214B器件的写信号WR,该写信号负责把数据总线上的数据写入到HSP50214B控制寄存器中,这样就实现了片选不同HSP50214B的目的。

HSP50214B的写操作过程采用间接寻址方式, 32bit的控制字首先通过8bit数据线分4次写入主寄存器,该4次写操作过程中地址线A2-0应依次为[000:011],之后DSP将该控制字对应的8bit目标寄存器地址写入HSP50214B内部专有寄存器,此时地址线应为[100],该操作触发一个脉冲,将主寄存器中的32bit控制字加载入目标寄存器。控制字在WR信号的上升沿锁存入主寄存器。需要格外注意的是,在相邻控制字加载过程之间需等待4个时钟周期,由HSP50214B进行内部加载配置。

由于DSP的数据总线和地址总线需要同时与EPLD和四片HSP50214B相连接,为了提高总线的驱动能力,DSP输出的总线需要通过TI公司的SN74LVTH162245芯片进行驱动后才能与这些异步接口的器件相连接。但是,这样直接加上驱动的数据和地址总线被四片HSP50214B分时复用会带来传输阻抗不匹配的问题,系统采用的方法是使被复用的DSP总线上的每一路信号首先驱动SN74LVTH162245上的四个输入端,这样就可以从它的输出端得到四个被相互隔离的四路相同信号,然后再各自加端接匹配电阻,对每路信号进行匹配后再接到各自的终端。这样不仅解决了信号隔离问题,还很好地解决了一路信号线因驱动多路终端所引起的传输阻抗不匹配的问题。

此外,DSP的控制信号通过EPLD译码产生DDC的输入使能信号ENI,决定DDC芯片开启工作时刻。在DSP加载DDC芯片控制字,HSP50214B芯片开始工作后产生输出数据有效信号DATA_RDY,通过EPLD对此信号进行计数监控,可以实时计算DDC输出的数据量,并进而向后级DSP发出读数据请求中断,实现合理的时序分配。

多片DDC同步工作的关键技术

为了实现多路中频信号同步处理,要求DDC同步工作。DSP通过EPLD译码控制着四片DDC的输入使能信号ENI,在DSP写DDC控制字期间,ENI处于无效状态,DSP写操作结束后向EPLD发出控制信号,将四片DDC芯片的输入端同时使能,从而实现了多DDC同步启动工作。

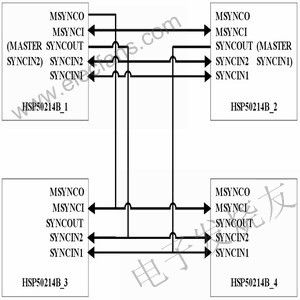

图2 多片HSP50214B同步工作电路

多片DDC的同步还需要内部工作时钟的同步,这是通过主从配置实现的,芯片的前端工作电路由输入时钟(CLKIN)实现同步,而后端电路由工作时钟(PROCLK)实现同步, 为了使四片DDC和EPLD之间系统时钟同步,系统要求用一个时钟信号源产生四路相干时钟分别分配给EPLD和四片HSP50214B,这给保证时钟信号的驱动能力和信号完整性带来了难度。系统的解决办法是将温补晶振产生的40MHz时钟信号首先传送到一个零延迟时钟驱动芯片CY2305的输入端,再由该芯片输出五路同步时钟信号,其中一路时钟直接供给EPLD,其它四路时钟分别输入HSP50214B的输入时钟CLKIN和工作时钟PROCLK。

DDC之间由SYNCOUT,SYNCIN1,SYNCIN2,MSYNCO和MSYNCI来控制同步时序, 如图2所示。MSYNCO是多芯片同步输出引脚,系统中HSP50214B_1配置为主芯片,它的MSYNCO输出连接至四片HSP50214B的MSYNIN引脚;SYNCOUT引脚由前端时钟CLKIN或工作时钟PROCLK产生,用以同步芯片内部工作,其中HSP50214B_1的SYNCOUT引脚连接至四片HSP50214B芯片的SYNCIN2引脚,用以同步DDC芯片内部的FIR滤波以及自动控制增益(AGC)部分;HSP50214B_2的SYNCOUT引脚连接至四片HSP50214B芯片的SYNCIN1引脚,用以同步DDC芯片内部的CIC抽取滤波以及数控振荡器部分。

结 语

在“基于电视信号的无源雷达信号处理”项目中,笔者设计的中频采集板卡对接收机输出的4路伴音和图像中频信号进行高速采集与数字下变频。笔者在电路设计中采用了本文提出的DSP控制多片DDC芯片的接口设计方案,对于4路A/D转换后的高速信号,分别通过DDC进行下变频和多级抽取滤波。该无源雷达信号处理机已经通过了外场试验验证,其中的中频采集板卡经测试可以精确实现数字下变频功能,精确度为0.01Hz;抽取模块实现信号速率400倍降低;滤波环节有效地增大了采集卡的动态范围31dB,很好地满足了无源雷达信号处理机的指标要求。