本文主要介绍一款基于复杂可编程逻辑器件的压电生物传感器检测电路。该检测电路核心为高性能CPLD,主要实现对压电生物传感器10MHz高频信号的测量与采集以及所采集的频率数据动态、实时显示以及频率数据串行通信等功能。此外详细阐明了系统整体结构设计以及系统硬件部分的实现,并给出了CPLD内核仿真结果和数据采集软件实测频率曲线。该系统还可以通过RS-232串行接口与计算机连接进行数据传输和数据存储及分析。与此同时,本电路优点还有很多,例如体积小、集成度高,具有可靠性高、实时性高等。

国内外基于压电石英晶体微天平技术的检测仪器大多数使用自行设计的振荡电路盒,使用高分辨的频率计数器测量频率输出,然后进行定时人工记数,仪器复杂,自动化程度低.微型压电生物传感器检测电路采用当前最有发展前景的复杂可编程逻辑器件(CPLD)为核心器件设计而成.目前,CPLD集成度可达25万等效门,工作速度可达180MHz.它借助自动化程度高的内核程序开发工具,可以大大缩短系统的计周期,而且数据采集可以由一块CPLD芯片完成,整个系统的硬件规模明显减小.在系统的研制阶段,由于CPLD器件引脚比较灵活,又有可擦除可编程的能力,因此对原设计进行修改时,只需要修改原设计文件再对CPLD芯片重新编程即可,而不需要修改电路布局,更不需要重新加工印刷线路板,这就大大提高了系统的灵活性.结合压电生物传感器特性,研制一种微型化的压电传感器检测电路有十分重要的意义.

1 压电生物传感器原理

压电石英晶体频移ΔF与在晶体表面均匀吸附的极薄层刚性物质量Δm之间存在正比关系,由Sauerbrey方程描述,并且对于AT切割的石英晶体,可得到Sauerbrey方程式:

式中,ΔF、Fq(晶体基频)、Δm、A单位分别为Hz、Hz、g.cm-2、cm2.石英晶片在气相中振荡时,Δf与Δm呈简单的线性关系,因此石英晶片可用来做非常敏感的质量检测器,其检测限可以达到ng级(10-9g.cm-2),甚至pg(10-12g.cm2)级水平.

根据压电石英晶体传感器的原理设计了一种微型化的压电传感器检测电路,其检测原理为在传感器上预先固定与待测物能发生亲和反应的“探针”,检测待测物时,随着亲和反应的进行,检测电路实时跟踪反应过程,记录传感器上质量变化引起频率变化,再通过上述定量关系式计算待测物的量,其灵敏度可以达到纳克级水平,结合纳米金技术可将传感器的灵敏度提高3~5倍.

2 电路硬件设计

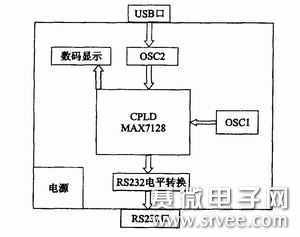

微型压电传感器检测电路是经过前几代仪器的开发经验总结和改进基础上完成的。它摒弃以往TTL集成电路或MCS51单片机为核心电路波动大,稳定性差,电路板绘制复杂,不利于升级换代的缺点,选择使用ALTERA公司生产的复杂可编程逻辑器件(CPLD)MAX7128为核心,基于RS232通信方式的串行接口数据采集分析平台.该系统分为7个模块:电源供电模块,RS-232电平转换模块,振荡电路模块,时钟模块,数码显示模块,MAX7128内核模块.其电路线路板布局如图1所示.

图1硬件结构图

图1中,USB口为压电生物传感器与检测电路相连接的接口;RS-232口为与计算机相连接的接口,将数字化的传感器信号(频率值)上传到计算机,由计算机(PC机)实现传感器信号的实时采集和显示,采集数据程序由VC++6.0编写;OSC1为提供系统工作时钟振荡电路,由TTL芯片和12MHz标准晶振组成,产生1s脉冲信号,作为CPLD工作时钟输入、RS-232通信时序脉冲以及数码管动态显示时序脉冲,准确度高、且精确;OSC2为传感器振荡电路,经过几代反复改良,在气相、液相均能够正常振荡且波形正常,将传感器表面生物反应信号转化成脉冲信号,输入CPLD进行信号数据采集;数码显示采用共阴极8×8段数码管,动态扫描显示当前传感器信号值和简单数据分析判断结果;电源给系统提供直流5V工作电压,含有直流6~15V变成5V稳压电路;RS-232电平转换电路将从CPLD输出的CMOS电平转化为计算机所接受的TTL电平,而且可增加数据传输距离.

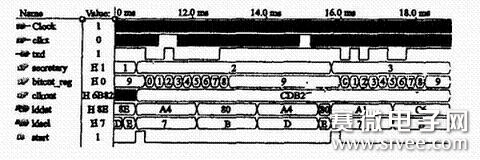

作为系统内核的CPLD,采用VerilogHDL硬件设计语言、MAX+plusII10.1编译系统编写基于Altera公司CPLD(MAX7128)器件的内核程序,设计实现了秒时钟定时、10MHz频率测量、RS-232通信时序发生器、RS-232协议数据通信、频率数据判断简单分析以及数码管动态扫描显示控制等综合功能,其原理如图2所示.

图2 CPLD内核原理图

3 系统仿真及实测结果

系统仿真结果:为了便于观察,将秒时钟计数判断设置为66C0,得到内核模块的仿真图,如图3所示.仿真图给出了频率采集细节,数码管显示控制以及串行通信控制.

图3 CPLD内核仿真图

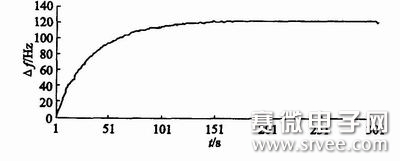

仿真结果吻合了设计思路,把内核程序下载到CPLD(MAX7128)器件中,实际测试过程中,数码管可以正确显示当前传感器的响应信号,使用自己开发的采集程序通过计算机串行通信采集数据数据曲线如图4所示.所采集的数据与仿真情况一致,更进一步验证了设计思路的成功.

图4 采集程序实测频率数据曲线

4结语

通过扩展,压电生物传感器检测电路能够升级为单通道微型压电生物分析一起。基于核酸杂交的特异性,其不仅可以用于生物样品分析,在医学临床研究领域用于疾病诊断或者基于抗原/抗体之间的特异性结合反应,还具有灵敏度高、特异性强等优点。如果采用CPLD升级为大容量FPGA后,本检测电路能够十分简便的升级为多通道生物分析系统,可以在生物分析检测各个领域应用。