过去十年中,高速数字总线已经获得了令人瞩目的发展,它们不仅比以往更快,而且还正在改变系统定时数据的方式。为提高数据吞吐量,新兴的同步数字总线可以通过一套定时机制在每个时钟周期内多次发送数据。本文将对源同步定时如何优化高速接口时序裕量进行讨论。

时序预算是对系统正常工作所需时序参数或时序要求的计算。为了使同步系统正常工作,其时序需求必须在一个时钟周期内满足。对时序的预算涉及到许多因素,包括对保持时间和最大工作频率的要求。通过时序预算,可以发现传统定时方法的局限性。

图1显示了一个标准定时系统。在该图中,一个存储器控 制器与一个SRAM连接。SRAM和存储器控制器都从同一个时钟源接收时钟信号。假设这里有意使时钟信号电路与电路延迟相匹配,相关时序参数如下(图 2):存储器控制器tSU(建立时间)、存储器控制器tH(保持时间)、主板电路tPD(传输延迟)、SRAM tCO(时钟到输出的延迟)、SRAM tDOH(输出数据的保持时间)、时钟发生器tSKEW(时钟偏移)、时钟发生器tJIT(周期抖动)以及时钟发生器tCYC(周期时间)。

如果考虑最坏情况下的输入建立时间、时钟到输出的延迟、传输延迟、时钟偏移和时钟抖动,通过计算最高频率就可以得到系统的最小周期时间。最高频率计算如下:

tCO(max, SRAM) + tPD(max) + tSU(max, CTRL) + tSKEW(max, CLK) + tJIT(max, CLK) < tCYC

通过计算保持时间可发现系统输出数据太快,影响了系统接收器件的输入保持时间。这样,最坏情况将发生在数据最早输出的时候。计算公式如下:

tCO(min, SRAM) + tPD(min) - tSKEW(min, CLK) - tJIT(min, CLK) > tH(max, CTRL)

现 在让我们假设SRAM和存储器控制器的时序参数值 为:tSU=0.5ns;tH=0.4ns;tCO=0.45ns;tDOH*=-0.45ns;tSKEW=±0.2ns;tJIT=±0.2ns。在 这种情况下,我们将使用带有双倍数据速率(DDR)接口的高速SRAM,SRAM在每个时钟的上升沿和下降沿驱动数据。

*tDOH < 0意味着在下一个时钟上升沿/下降沿前数据已变得无效。所需的最小保持时间计算如下:

tDOH + tPD - tSKEW - tJIT > tH

-0.45 ns + tPD - 0.2 ns - 0.2 ns > 0.4 ns

-0.85ns + tPD > 0.4 ns

tPD > 1.25 ns

假设FR4电路板上走线的传输延迟为160ps/英寸。SRAM到存储器控制器的走线长度至少有7.82 in。tPD取1.2ns,最大工作频率可计算如下。因为SRAM有一个DDR接口,所以时序预算是基于半个时钟周期:

tCO + tPD + tSU + tSKEW + tJIT < tCYC/2

0.45ns+1.25ns+0.5ns+0.2ns+0.2ns

2.6ns

5.2ns

192MHz>fCYC

在FR4电路板上走线的长度为7.82英寸和典型时序参数的前提下,可满足工作频率可高达192MHz时的时序预算要求。对于那些板空间有限的系统,7.82英寸的最小走向长度约束就成了系统难以满足的一个要求。

如 果无法增加走线延迟,那么通过使用延迟锁定环/锁相环(DLL/PLL)对时钟信号进行移相以更早地捕获数据,存储器控制器可以满足保持时间的要求(图 3)。存储器控制器将必须用系统时钟信号来重新同步捕获的数据。使用这个方法将会引入额外的PLL/DLL抖动,这会降低系统的最大工作频率。有了这个附 加的PLL延迟后,所需的最小保持时间就变为:

tDOH + tPD(trace) + tPLL/DLL_DELAY - tSKEW - tJIT > tH

tCO + tPD + tSU + tSKEW + tJIT + tJIT_PLL/DLL < tCYC/2

其中,tJIT_PLL/DLL是由PLL引入的延迟。即使使用最快的SRAM和ASIC/FPGA,时钟偏移、时钟抖动和电路传输延迟也会很明显地限制系统性能。

如 前所述,如果使用FR4电路板,走线延迟约为160ps/英寸。鉴于很高频率下数据有效窗口已变为2ns(例如对250MHz的DDR器件而言)甚至更 小,这个数字是非常重要的。时钟信号之间的偏移也会显著减小时序裕量。我们将会看到源同步时钟可以明显减少传输延迟、偏移和抖动,使时序收敛更容易达到。

源同步定时的优点

在 典型的源同步处理中,与每个数据字相关联的时钟上升沿被发送出来(DDR存储器每个时钟周期可能有多个数据),接收器件使用这个时钟上升沿来锁存数据,然 后再将数据与主时钟或公用时钟同步。由同一个器件对时钟信号和数据/控制信号进行同步后传送,实际上就消除了主板电路信号相对时钟信号的传输延迟。

但是采用源同步定时就需要考虑不同的主板布线。在一个带有独立时钟发生器的系统中,该时钟发生器为多个器件提供时钟信号,首要的问题是电路长度的设计应使所有的时钟沿同时到达器件,这可能需要延长连接时钟发生器旁边器件的走线长度。

采用源同步的方法,主要的问题是通过匹配输出时钟和数据信号的走线长度来保持时钟和数据之间的相位对准。如果走线正确匹配,相对时钟信号的数据传输延迟就不复存在了。

有很多种方法可以实现源同步定时:

1)源同步时钟信号的上升沿对准到数据有效窗口的起始点。诸如QDR-II/DDR-II SRAM这样的大多数DDR存储器采用了这种方法,存储器将时钟信号和数据都发送到接收器。本文中将以它们作为例子进行讨论。

2)QDR-II产生一对输出时钟信号CQ和/CQ,理想情况下它们之间的相位差为180°,接收器利用这两个时钟信号的上升沿来锁存数据。

在两个存储器中,接收器都必须将此时钟信号延迟以满足其捕获数据所需要的建立和保持时间。此延迟可以通过片上延迟模块来实现,具体可以在接收端使用PLL或DLL,或采用板上走线延迟的方法。

这两种方法因具有频率转移能力而在FPGA设计中受到青睐。为在更高频率上使用同样的设计,可以修改FPGA代码以改变由PLL/DLL引入的延迟。另外,ASIC总是运行在一个特定的频率,ASIC通常会选用板上走线延迟的方法。

也有一些源同步时钟实现方案,在源端将其源同步时钟信号延迟,在数据有效窗口的中心对齐。在这种情况下,用户可以直接实现源同步时钟信号来锁存接收器的数据(假设时钟和数据之间的走线匹配)。

抖动的影响

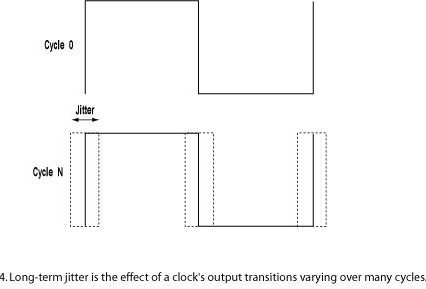

抖 动可以被定义为时钟位转换与理想时序偏离,时钟位转换可能超前或滞后,这里有多种不同类型的抖动。周期间抖动是时钟输出位转换中与前一个周期相应位置的偏 离(参见图2)。周期抖动用来衡量时钟输出位转换与理想时序的最大偏离。长期抖动用来衡量在多个周期的时钟输出位转换中与理想时序的最大偏离,这里的“多 个周期”的具体数目取决于具体的应用和工作频率(图4)。

根据具体的应用,在时序预算中应考虑其中一种或所有三种类型的抖动。在同步定时环境中,产生输入时钟的时钟源或PLL/DLL一般会引起抖动变化。在时序预算中考虑了抖动因素后,抖动(tJIT)就会显著地缩小时序裕量,特别在高频率下。

但是,如果在接收端时钟和数据存在相同的抖动,就可以从时序预算中除去抖动成分(tJIT)。采用源同步时钟的情况下也是如此,这是时钟信号和数据由同一个 发射器件驱动并一直保持对准。将时钟设计得像其中一个输出时,通常就会产生这样的效果。虽然仍必须考虑时钟和数据管脚之间时钟到输出的时间变化,但这个参 数一般都在±100ps左右。

在某些应用中,源同步时钟被延迟1个周期以上以锁存数据。这种情况下,时序预算中要考虑长期抖动,这将使时序裕量减小。这种抖动也被称为N周期抖动,N是相对于数据信号,源同步时钟信号被延迟的周期数。当然,一般不建议将源同步时钟信号延迟一个周期以上。

时序预算的计算

从下面的例子中可以看出,从时序预算中消除传输延迟可以大大改善系统时序裕量。图5给出了采用源同步时钟的SRAM的例子。

让我们按下面步聚计算时序预算。按照设计,SRAM输出时钟信号的上升沿与数据有效窗口的起始边对准。我们假设存储器控制器通过PLL/DLL片上延迟时钟延迟以满足建立和保持时间。SRAM和存储器控制器采用相同的时序参数。

假设时钟和数据走线长度匹配,计算时序预算时就可以忽略电路传输延迟tPD。另外,时钟与数据具有同样的偏移和抖动(不包括管脚之间±100 ps的偏移),因此无需再考虑时钟发生器抖动和偏移(tSKEW, tJIT)。

在这个系统中,需要考虑的另外一个参数是SRAM的tJIT:相对于数据的SRAM输出源同步时钟抖动。这可能是由管脚间时钟到输出的时间变化而引起的。

在 这个例子中,我们假设时钟和数据走线匹配地很好。如果由于电路设计而导致走线长度出现差异,就必须考虑时钟和数据信号走线长度的差异。如果时钟信号的走线 是有意延长以延迟时钟信号(将时钟信号与数据有效窗口中心对准),就不用考虑此参数。假设SRAM源同步时钟抖动为tJIT=±0.2ns,我们可以像表 中列出的那样逐步计算最小周期时间(参见表)。要获得非负值裕量,应满足如下条件:

tM>0

tCYC/2-2.2ns>0

tCYC/2>2.2ns

tCYC>4.4ns

fCYC<227MHz

本例采用源同步时钟信号,满足建立和保持时间要求,对数据信号走线长度也没有什么约束。计算得到的最大工作频率是277MHz,比传统时钟同步方法提高了35MHz。注意本例中主要的频率限制因素是控制器的建立和保持时间。

使用源同步时钟的最优方法

为最好地利用源同步时钟,设计工程师应注意以下要点:

不 要使源同步时钟的延迟时间超过一个周期。源同步时钟的上升沿与其所驱动的数据信号是严格匹配的,所以时钟和数据信号应具有同样的抖动并互相抵消。如果将源 同步时钟信号的上升沿延迟到下一个周期以锁存数据,那么就必须考虑另外一个抖动成分,即N周期抖动,N是相对于数据信号,时钟信号被延迟的周期数。图6和 图7中给出了使用源同步时钟的推荐方法和不推荐方法。这些例子采用QDR-II源同步时钟(CQ和/CQ)。

注意:如果有两个源同步时钟,最好两个都用到。