虽然工程师都熟谙MOSFET数据手册上的品质因数,但为了选择出合适的MOSFET,工程师必需利用自己的专业知识对各个具体应用的不同规格进行全面仔细的考虑。例如,对于服务器电源中的负载开关这类应用,由于MOSFET基本上一直都是处于导通状态,故MOSFET的开关特性无关紧要,而导通阻抗(RDS(ON))却可能是这种应用的关键品质因数。然而,仍然有一些应用,比如开关电源,把MOSFET用作有源开关,因此工程师必须评估其它的MOSFET性能参数。下面让我们考虑一些应用及其MOSFET规格参数的优先顺序。

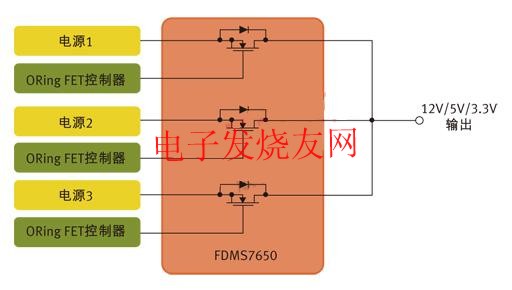

MOSFET最常见的应用可能是电源中的开关元件,此外,它们对电源输出也大有裨益。服务器和通信设备等应用一般都配置有多个并行电源,以支持N+1 冗余与持续工作 (图 1)。各并行电源平均分担负载,确保系统即使在一个电源出现故障的情况下仍然能够继续工作。不过,这种架构还需要一种方法把并行电源的输出连接在一起,并保证某个电源的故障不会影响到其它的电源。在每个电源的输出端,有一个功率MOSFET可以让众电源分担负载,同时各电源又彼此隔离 。起这种作用的MOSFET 被称为"ORing"FET,因为它们本质上是以 "OR" 逻辑来连接多个电源的输出。

图1:用于针对N+1冗余拓扑的并行电源控制的MOSFET。

在ORing FET应用中,MOSFET的作用是开关器件,但是由于服务器类应用中电源不间断工作,这个开关实际上始终处于导通状态。其开关功能只发挥在启动和关断,以及电源出现故障之时 。

相比从事以开关为核心应用的设计人员,ORing FET应用设计人员显然必需关注MOSFET的不同特性。以服务器为例,在正常工作期间,MOSFET只相当于一个导体。因此,ORing FET应用设计人员最关心的是最小传导损耗。

低RDS(ON) 可把BOM及PCB尺寸降至最小

一般而言,MOSFET 制造商采用RDS(ON) 参数来定义导通阻抗;对ORing FET应用来说,RDS(ON) 也是最重要的器件特性。数据手册定义RDS(ON) 与栅极 (或驱动) 电压 VGS 以及流经开关的电流有关,但对于充分的栅极驱动,RDS(ON) 是一个相对静态参数。例如,飞兆半导体 FDMS7650 的数据手册规定,对于10V 的栅极驱动,最大RDS(ON) 为0.99 mΩ。

若设计人员试图开发尺寸最小、成本最低的电源,低导通阻抗更是加倍的重要。在电源设计中,每个电源常常需要多个ORing MOSFET并行工作,需要多个器件来把电流传送给负载。在许多情况下,设计人员必须并联MOSFET,以有效降低RDS(ON)。

需谨记,在 DC 电路中,并联电阻性负载的等效阻抗小于每个负载单独的阻抗值。比如,两个并联的2Ω 电阻相当于一个1Ω的电阻 。因此,一般来说,一个低RDS(ON) 值的MOSFET,具备大额定电流,就可以让设计人员把电源中所用MOSFET的数目减至最少。

除了RDS(ON)之外,在MOSFET的选择过程中还有几个MOSFET参数也对电源设计人员非常重要。许多情况下,设计人员应该密切关注数据手册上的安全工作区(SOA)曲线,该曲线同时描述了漏极电流和漏源电压的关系。基本上,SOA定义了MOSFET能够安全工作的电源电压和电流。在ORing FET应用中,首要问题是:在"完全导通状态"下FET的电流传送能力。实际上无需SOA曲线也可以获得漏极电流值。再以FDMS7650为例,该器件的额定电流为36A,故非常适用于服务器应用中所采用的典型DC-DC电源。

若设计是实现热插拔功能,SOA曲线也许更能发挥作用。在这种情况下,MOSFET需要部分导通工作。SOA曲线定义了不同脉冲期间的电流和电压限值。

注意刚刚提到的额定电流,这也是值得考虑的热参数,因为始终导通的MOSFET很容易发热。另外,日渐升高的结温也会导致RDS(ON)的增加。MOSFET数据手册规定了热阻抗参数,其定义为MOSFET封装的半导体结散热能力。RθJC的最简单的定义是结到管壳的热阻抗。细言之,在实际测量中其代表从器件结(对于一个垂直MOSFET,即裸片的上表面附近)到封装外表面的热阻抗,在数据手册中有描述。若采用PowerQFN封装,管壳定义为这个大漏极片的中心。因此,RθJC 定义了裸片与封装系统的热效应。RθJA 定义了从裸片表面到周围环境的热阻抗,而且一般通过一个脚注来标明与PCB设计的关系,包括镀铜的层数和厚度。

总而言之,RθJC在电源设计团队的控制范围以外,因为它是由所采用的器件封装技术决定。先进的热性能增强型封装,比如飞兆半导体的Power 56,其RθJC 规格在1 和 2 oC/W之间,FDMS7650 的规格为 1.2 oC/W。设计团队可以通过PCB设计来改变 RθJA 。最终,一个稳健的热设计有助于提高系统可靠性, 延长系统平均无故障时间(MTBF)。

开关电源中的MOSFET

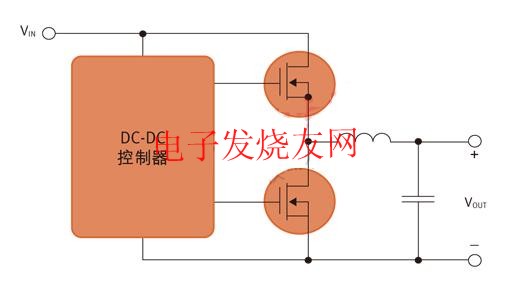

现在让我们考虑开关电源应用,以及这种应用如何需要从一个不同的角度来审视数据手册。从定义上而言,这种应用需要MOSFET定期导通和关断。同时,有数十种拓扑可用于开关电源,这里考虑一个简单的例子。DC-DC电源中常用的基本降压转换器依赖两个MOSFET来执行开关功能(图 2),这些开关交替在电感里存储能量,然后把能量释放给负载。目前,设计人员常常选择数百kHz乃至1 MHz以上的频率,因为频率越高,磁性元件可以更小更轻。

图2:用于开关电源应用的MOSFET对。(DC-DC控制器)

显然,电源设计相当复杂,而且也没有一个简单的公式可用于MOSFET的评估。但我们不妨考虑一些关键的参数,以及这些参数为什么至关重要。传统上,许多电源设计人员都采用一个综合品质因数(栅极电荷QG ×导通阻抗RDS(ON))来评估MOSFET或对之进行等级划分。

栅极电荷和导通阻抗之所以重要,是因为二者都对电源的效率有直接的影响。对效率有影响的损耗主要分为两种形式--传导损耗和开关损耗。

栅极电荷是产生开关损耗的主要原因。栅极电荷单位为纳库仑(nc),是MOSFET栅极充电放电所需的能量。栅极电荷和导通阻抗RDS(ON) 在半导体设计和制造工艺中相互关联,一般来说,器件的栅极电荷值较低,其导通阻抗参数就稍高。

开关电源中第二重要的MOSFET参数包括输出电容、阈值电压、栅极阻抗和雪崩能量。

某些特殊的拓扑也会改变不同MOSFET参数的相关品质,例如,可以把传统的同步降压转换器与谐振转换器做比较。谐振转换器只在VDS (漏源电压)或ID (漏极电流)过零时才进行MOSFET开关,从而可把开关损耗降至最低。这些技术被成为软开关或零电压开关(ZVS)或零电流开关(ZCS)技术。由于开关损耗被最小化,RDS(ON) 在这类拓扑中显得更加重要。

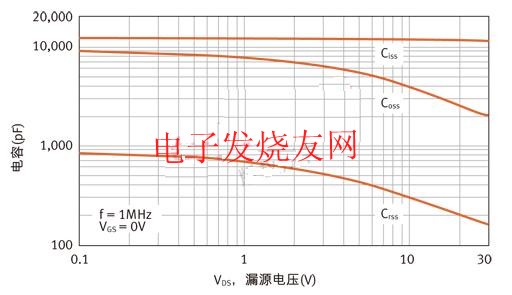

低输出电容(COSS)值对这两类转换器都大有好处。谐振转换器中的谐振电路主要由变压器的漏电感与COSS决定。此外,在两个MOSFET关断的死区时间内,谐振电路必须让COSS完全放电。因此,谐振拓扑很看重较低的COSS。考虑图3所示的飞兆半导体FDMS7650的COSS与VDS的关系图。

图3:FDMS7650的COSS与VDS的关系图。

低输出电容也有利于传统的降压转换器(有时又称为硬开关转换器),不过原因不同。因为每个硬开关周期存储在输出电容中的能量会丢失,反之在谐振转换器中能量反复循环。因此,低输出电容对于同步降压调节器的低边开关尤其重要。

马达控制应用的MOSFET

马达控制应用是功率MOSFET大有用武之地的另一个应用领域,这时最重要的选择基准可能又与其它大不相同。不同于现代开关电源,马达控制电路不在高频下开关。典型的半桥式控制电路采用2个MOSFET (全桥式则采用4个),但这两个MOSFET的关断时间(死区时间)相等。对于这类应用,反向恢复时间(trr) 非常重要。在控制电感式负载(比如马达绕组)时,控制电路把桥式电路中的MOSFET切换到关断状态,此时桥式电路中的另一个开关经由MOSFET中的体二极管临时反向传导电流。于是,电流重新循环,继续为马达供电。当第一个MOSFET再次导通时,另一个MOSFET二极管中存储的电荷必须被移除,通过第一个MOSFET放电,而这是一种能量的损耗,故trr 越短,这种损耗越小。

所以,若设计团队需要在电源电路采用MOSFET,在评估过程开始之前,需对手中的应用进行仔细全面的考虑。应根据自己的需求而非制造商吹嘘的特定规格来对各项参数进行优先级划分。

补充:利用IC和封装设计获得最小的 RDS(ON) 规格

在MOSFET的选择过程中,评估参数的设计人员一般通过仔细分析相关规格来了解自己到底需要什么。但有时深入了解IC制造商如何提供工作特性是很有必要的。以RDS(ON)为例,你也许通常期望该规格只与器件的设计及半导体制造工艺有关。但实际上,封装设计对导通阻抗RDS(ON) 的最小化有着巨大的影响。

封装对RDS(ON)的作用巨大是因为该参数主要取决于传导损耗,而封装无疑可以影响传导损耗。考虑本文正文提及的飞兆半导体FDMS7650 和1mΩ导通阻抗。该器件能获得较低RDS(ON) 值,大约一半原因可归结于封装设计。其封装采用一种坚固的铜夹技术取代常用的铝或金键合引线来连接源极和引线框架。这种方案把封装阻抗降至最小,并降低了源极电感,源极电感是开关器件产生振铃的主要原因。