摘 要: 为了使JPEG2000" title="JPEG2000">JPEG2000能应用到便携产品中,采用了高效存储结构的硬件实现方案,并设计了相应的寄存器组和控制逻辑。仿真结果表明所设计的块编码器能够在0.256s内完成对一幅512×512的灰度图像的编码。

关键词: 基于最优截断的嵌入式块编码 JPEG2000 交错存储

随着多媒体市场的迅猛发展,百万像素的数码相机、各种功能强大的彩屏手机等数字消费产品逐渐普及。这些多媒体应用均需要处理高质量、高分辨率的大图像,这对存储介质的容量和传输信道的带宽都提出了新要求。图像压缩的国际标准JPEG已不能满足这些新的要求,而且它在低码率时还存在着方块效应。因此,从1997年开始,JPEG委员会就致力于开发新的静态图像压缩标准JPEG2000[1],并在2000年8月形成了最终草案,在2000年12月使其成为了国际标准。

JPEG2000相比JPEG有着更大的灵活性,不仅能对原始图像高效地压缩,而且可以对压缩后的数据进行处理。这意味着可以从压缩码流中提取一部分数据来重建低分辨率或低码率的图像,或者是提取图像的感兴趣区域。这样就允许将原始图像压缩为单一的码流以适应不同的传输信道、存储或显示设备,而不必考虑该图像的大小、分量多少以及样本的精度。

JPEG2000的一个主要特性就是基于图像质量和分辨率的累进传输,为了支持这种可分级的压缩编码,JPEG2000采用了离散小波变换(DWT)替代JPEG中的离散余弦变换(DCT),并采用了Taubman提出的具有优化截断点的嵌入式块编码[2](EBCOT)算法。

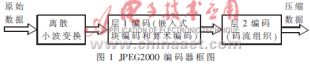

JPEG2000编码器的框图如图1所示。

首先将原始图像划分为图像片,通过DWT将图像片分解为不同的分辨率级别,获得多个子带的频域系数,将各个子带划分为码块(典型大小是32×32或64×64),对每个码块进行嵌入式的块编码,生成上下文和待编码的数据位;然后由算术编码" title="算术编码">算术编码部分根据每个数据位的上下文自适应编码,产生每个码块的子码流;最后将各个码块的子码流组织成代表码流质量层的分组,并添加相应的头结构信息,帮助解码器识别如何解码。

EBCOT[2]作为JPEG2000的核心部分,包含了层1和层2两部分,其中嵌入式块编码的逻辑比较复杂,是影响编码速度的瓶颈之一,使用通用处理器很难提高其效率。传统的编码方式采用软件实现,但速度和效率不高,且占用较大的存储资源;而采用硬件实现方式则会有更大的灵活性。事实上采用硬件芯片实现,不但可以提高编码的速度和效率,而且也能根据算法本身的特点,采用特定的、高效的硬件结构来实现算法的关键部分,可以较大幅度地提高编码效率。另外,随着多媒体的应用和网络应用逐步便携化,以前多数可以在PC机上处理的工作必须转移到便携产品上,这对便携产品有限的资源提出了挑战。因此有必要研究硬件编码芯片完成编码过程,本文旨在研究JPEG2000编码中的关键技术——嵌入式块编码。

1 算法分析及设计

嵌入式块编码其实是基于位平面的编码[2],而每个位平面又被划分为三个编码通道,即显著通道、细化通道和清除通道。编码采用固定的扫描方式,每个比特位仅在其中的一个编码通道中完成编码。编码过程可以分为两个步骤,即判别编码通道的归属和编码原操作。在显著通道中,当比特位本身不显著,且周围8个近邻至少有一个是显著时被编码;在细化通道中,当比特位在上一个位平面就变显著时被编码;在清除通道,所有在上面两个通道中略过的比特位被编码。编码原操作共4个,即零值编码、符号编码、细化编码和游程编码。

根据算法要求,编码时必须用到一些编码信息。假设码块的大小是32×32的,则编码信息位包括1024个显著信息位(表示当前系数位是否显著)、1024个细化信息位(表示当前系数位是否第一次细化)、1024个访问信息位(表示当前系数位是否在前面的编码通道中编过)。当然,除此之外,还需要有1024个符号位和幅度位,因此编码过程中需要存储的信息为5Kbit。由于FPGA片内RAM资源十分有限,因此将码块量化后的小波系数存在外部RAM中(对于32×32的码块,16bit的系数,需要存储16Kbit),而在片内只存储5Kbit的信息。

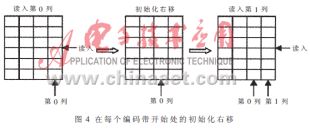

块编码过程是以一列的4个比特位为单位进行编码,且在判别编码通道的归属和编码操作时,都需要用到当前比特位的8个近邻的显著信息和符号信息。因此,事实上在编码每一列数据时,必须访问18bit的显著信息和符号信息,以及当前列的幅度位、访问信息和细化信息各4bit。对于幅度位、访问信息和细化信息,可以将每列的数据作为一个字存储,但这种存储方式对显著信息和符号信息却效率较低。如图2所示,如果采用右边的方案,则对于编码带中的每一列,必须读取12bit的显著和符号信息,其中有6bit是冗余的;如果采用左边的交错存储" title="交错存储">交错存储[3]的方案,即对于32×32的码块,在其首行之前和末行之后各添加一行,形成34×32的块,然后将每两行作为一组,并采取交错方式存储(a, b,c,b,a,b,c,…,b,c,b,a),则读取信息时不会有冗余。

显然,交错存储方案更有效,只是它需要在硬件电路上付出一些代价。首先,在预处理小波数据时,必须将符号位按照上述交错方式写入内部RAM,这比处理幅度位复杂一些。其次,在编码过程中,需要读取数据至内部6×4显著或符号寄存器,而对于奇、偶数编码带,其读入顺序也是交错的,对于前者是a、b、c,对于后者则是c、b、a;而且读取三块内存区域的地址信号也是不同步的,如表1所示,读取存储器b的地址信号始终增长,而读取存储器a和b的地址信号则符合以下规律:前者在从奇编码带过渡到偶编码带时地址增加,而在从偶编码带过渡到奇编码带时地址保持不变;后者正好相反。

因此,必须设计相应的控制电路满足上述要求,尽管这样做付出了额外的代价,但却大大提高了存储器的读写效率(提高了50%),这对于需要频繁访问存储器的位平面编码来说是很宝贵的;另外,采用了交错存储方式,可以对三块存储区域独立地产生地址信号,一次性读取6bit,而在常规的存储方式下,为了读取12bit信息,必须对同一块存储区域访问3次,可见采用交错存储的方案同时也提高了读写速度。

在JPEG2000的标准中,块编码器采用两种编码模式,即NORMAL和VCAUSAL。在VCAUSAL模式下,考虑当前编码位的周围显著信息时,将下一编码带的显著信息看作是不显著的,而在NORMAL模式下则看作是显著的。在文献[4]中,采用VCAUSAL模式,尽管这样简化了对存储器访问的逻辑控制,节省了一些存储空间,但却降低了块编码器的编码效率。因此,本文结合文献[3]和[4],设计了图3所示的寄存器组来配合上面介绍的交错存储的方案,这些内部寄存器包括6×4bit的显著和符号信息寄存器,8bit的细化和访问信息寄存器,4bit的幅度寄存器,如图3所示。

图3中表示出了各个寄存器读入数据和写回更新数据的位置、当前的编码位置和当前编码位。这些寄存器都能完成右移一位的功能。特别值得注意的是:由于编码过程中必须用到18bit的显著和符号信息,因此在每个编码带开始处,必须对显著和符号信息寄存器做初始化右移一次,确保在编码第0列数据时已经有18bit的信息,见图4的示例。

2 硬件设计

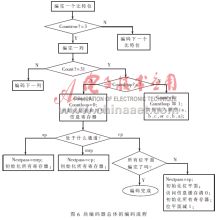

根据本文设计的编码算法,可用如图5所示的硬件结构实现嵌入式块编码器。

上述结构中,状态机用于控制总体的编码流程,外部信号START使状态机进入初始的预处理状态,表示此时外部RAM的数据已经准备好,然后在编码过程中根据计数器的数值进行状态切换。

设计中用到的计数器共3个,即Countrow(位计数器)、Count(列计数器)、Countloop(编码带计数器)。图6中示出了块编码器的总体流程,从中可以看出编码器的状态随计数器的数值变化的情况。

预处理单元分为两个部分:码块预处理和位平面预处理。其中码块预处理包括计算需要编码的位平面数,提取各个系数的符号位填充相应的符号缓存,初始化显著信息缓存和细化缓存(全部清0);位平面预处理则提取当前位平面的幅度位填充相应的幅度缓存,初始化访问信息缓存(全部清0)。

读写控制逻辑单元负责产生合适的控制信号与外部RAM和内部缓存接口;在预处理时负责外部RAM和内部缓存的读写控制,在编码过程中则负责内部缓存和寄存器组的读写控制。

编码单元分为两部分(见图7),判断逻辑和编码操作单元。判断逻辑负责决策当前系数位是否属于当前的编码通道,编码操作单元包括零值编码、细化编码和符号编码,而游程编码则采用硬连线编码,不使用独立的单元。这几个编码操作单元直接采用组合逻辑实现,而不是采用查表方式。多路选择器则根据当前执行的编码操作选择输出合适的CX和D。

FIFO单元用于解决块编码和算术编码逻辑之间的异步问题(因为前者产生数据具有间歇性,且算术编码处理数据也会有一定的延迟)。

3 结论与展望

本文通过对嵌入式块编码的算法分析,结合文献[3]和[4]的方案,采用了比较合理的存储结构来存储编码信息,并设计了相应的寄存器组和地址产生控制逻辑,本设计能够做到读写操作无冗余信息。

本编码器算法采用MODELSIM进行功能仿真,图8是在MODELSIM中截取的部分仿真波形。仿真所采用的时钟频率是50MHz,从图8中可以看出编码过程在1074090ns完成,大约1ms左右完成32×32码块的编码。因此,对于一幅512×512的灰度图像,估计能够在0.256s内完成编码。本设计选用的FPGA芯片最高时钟频率可达到275MHz,估计通过一定的优化,可使工作频率进一步提高;另外,块编码的算法本身就蕴含着并行的特性,可以在FPGA中实现多个块编码器单元同时处理多个码块的数据,这样编码一幅图像的速度可以进一步提高。

参考文献

1 M.Boliek,C.Christopoulos,E.Majani (Editors). JPEG 2000 Part 1 Final Publication Draft.ISO/IEC JTC1/SC29/WG1 N2678, July 2002

2 D.Taubman.High Performance Scalable Image Compression with EBCOT. IEEE Transactions on Image Processing,2000;9(7):1158~1170

3 K.-F. Chen, C.-J. Lian, H.-H. Chen, L.-G. Chen. Analysis and Architecture Design of EBCOT for JPEG2000. IEEE ISCAS 2001,2001;2(3):765~768

4 K.Andra, T. Acharya,C. Chakrabarti. Efficient VLSI Imple- mentation of Bit Plane Coder of JPEG2000. Proc. of SPIE Applications of Digital Image Processing, 2001