MOSFET能够将导通电阻再降低一点那就棒了。电阻导致发热,换而言之就是浪费电能。为何你们不能环保一点呢? – 潮州怒汉上

亲爱的FAE博士:

我将飞兆半导体的FET置于高频下工作,而开关损耗成为耗电的罪魁祸首。我不理解,为何你们不能再努力一点,使器件开关所需的栅极电荷再减低一些,从而减少耗电。为何你们不能环保一点,老是要浪费这么多电能?- 深圳心烦人上

亲爱的潮州怒汉和深圳心烦人:

今天你们真幸运。咖啡师给我弄了杯非常棒的拿铁浓咖啡,还在那层厚薄恰到好处的牛奶泡沫上画上一个心型点缀。因此,我发誓今天不会因任何事情坏了我的心情。今天可是我的好日子哦。上下班堵车?这不是问题。行人慢腾腾过街?我不会烦躁。烦人的问题?我会笑脸相迎。

我们经常接到这样的问题。难道还有谁比我们这群在实验室和生产车间拼命工作,年复一年提供更好的MOSFET 的天才更不受人赏识的吗?我们最近推出了首款采用Power56 封装,电阻低于1 mOhm的30V N沟道MOSFET器件(FDMS7650)。你大概可以想象到在产品发布时,我们整个工程部都沉浸在狂欢之中。

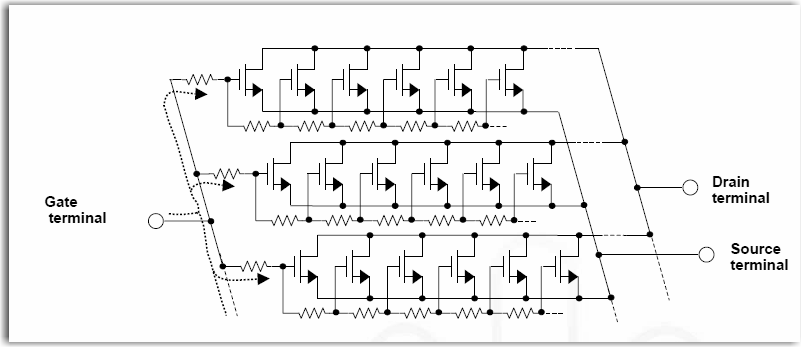

好了,让我回答这两位朋友的问题。你认为你买的是一个MOSFET器件,但实际上,你购买的是很多个MOSFET器件(可能数百万,甚至数千万),我们降低导通电阻的方法是:在裸片上填充更多的并联晶体管。我们的品质因数是每平方厘米面积裸片的电阻值,而且我们每年都在降低这个数值。

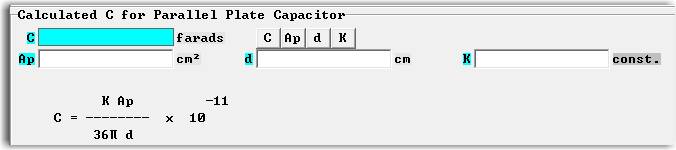

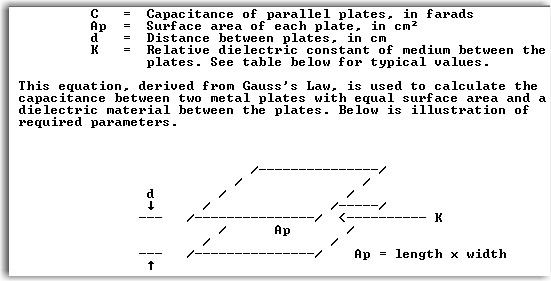

我知道你在想什么…要利用沟槽技术来构建所有这些晶体管,最大限度地增加漏极和源极表面积,同时保持低电容,从而最大限度地降低栅极电荷需求,一定是件非常困难的事情。的确是个挑战。下面是电容的基本计算公式:

图2:基本的电容计算方法

这个计算公式提醒我们电容随“平板”面积增加,以及平板间距离减少而增大。这意味着,当我们通过增加并联晶体管来降低电阻的同时,电容一般也会增加。当然,我们会尽其所能…注意介电常数K值… 如果能够减小K值,就会对我们有利。当然如果pi值提高,对我们也有利,因此,我们在呼吁国际标准化组织将pi值提高,比如是5这一类容易记忆的数值 (这就是所谓仔细无遗的工程师幽默啊)。

我们以两种方式在市场体现产品价值;要么使用较小的裸片,以较低的成本,实现同样的导通电阻;要么以相同的价格实现更低的导通电阻。可是可曾有人为此来电感谢我们吗?对,很少有人会这么样做。

我们认识到客户对栅极电荷的需求,并通过电荷均衡来全力控制它,使其变得更小。不过从前述两封读者来信所见,让所有客户都满意是很难的事情,但我们在继续尝试。

至于环保的问题,我的回应是:我小时候曾养过一头土耳其安哥拉猫,它后来死于环境污染。你想,我会不关注环保吗?好吧,如果不介意的话,我还是回去品尝可口芬芳的拿铁咖啡了。