128Mb以上的串行闪存被认为是电子产品满足市场需求、增加更多功能的一个主要障碍。针对需要128Mb以上串行闪存的应用要求,美光科技推出一个简单的独一无二的扩容解决方案。这个解决方案可以把存储容量轻松地扩大到4G或更大,完全兼容现有的串行外设接口(SPI)协议,无需重新设计主芯片的硬件。该解决方案优于市场上现有的要求创建一个新的32位寻址模式的解决方案,因为创建新的寻址模式可能强迫设计人员修改软硬件。

SPI协议的优点与局限

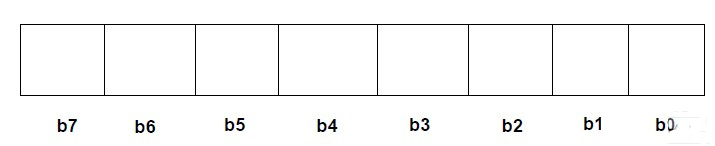

凡是在今天市场上销售的独立串行闪存都采用基于3个地址字节的SPI协议。SPI协议的数据祯由多个字节(8位)组成,主要包括:1)一个指示闪存操作的操作码(8位);2) 24位读写操作地址(3个字节) ,用于对所选存储区进行寻址;3) 如果写操作,在所选地址写入N x 8位数据(N = 1 … 256) 。SPI协议在嵌入式市场取得巨大成功,被所有的嵌入式串行闪存接受。升级应用无需修改硬件是在闪存内采用SPI协议的一个主要好处,因为不同闪存容量可以共用同一种封装和引脚排列方式(8引脚)。

不过,如果这个协议不能用于存储密度超过128Mb应用时,那么其优点就会荡然无存。因为SPI协议使用3个地址字节的祯通信,所以系统最大寻址空间被限制在128Mb。存储密度在256Mb或更高的闪存要求SPI协议增加额外的字节。协议的修改可能迫使所有的设计人员(特别是需要使用128Mb存储器的芯片组厂商)重新设计硬件。此外,若想把存储密度提高到256Mb或更高,他们无法升级现有的代码存储器为128Mb(3个地址字节)的应用。

增加存储密度的解决方案

因为这个原因,设计人员一直在寻找一个有效的解决办法,只需对软硬件稍加修改,即可把存储器密度提高到128Mb。有一个提议是开发一个支持更高寻址密度的32寻址模式,增加2种命令以解决24位与32位之间的转换问题。然而,这种方法需要在24寻址机制的基础上修改现有的软件,协议变化可能迫使设计人员重新设计主芯片的硬件。

美光科技的串口闪存产品阵容,存储密度从1/2Mb一直延伸到128Mb,现在该公司提出一个简单的解决方案,可以帮助设计人员解决存储密度提升问题。这个解决方案基于美光最新推出的N25Q256闪存,该方案的最大亮点是在采用相同的SPI协议情况下,不仅能够满足256Mb应用的需求,还能满足512Mb到32Gb的需求。

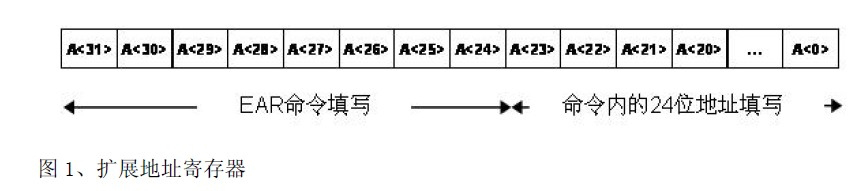

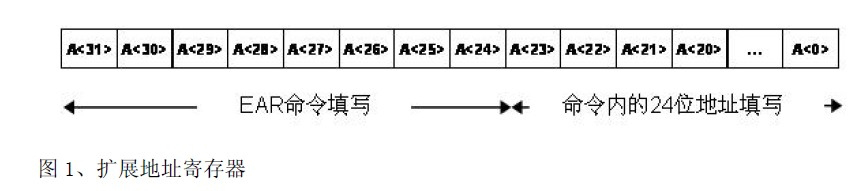

这个解决方案采用一个叫做扩展地址寄存器(EAR)的n-位寄存器,可以把寻址空间扩展到传统的3个字节(24位)以上。主机可以使用一个专用指令写寄存器(上电后寄存器进入00……0b默认状态)。这样,存储器被外部视为n个以128Mb为单位的存储段,该寄存器的内容可以对每个段进行寻址。

扩展地址寄存器

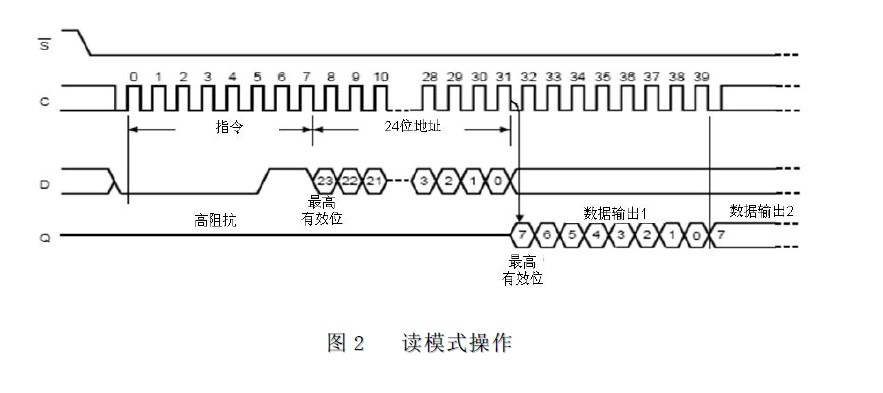

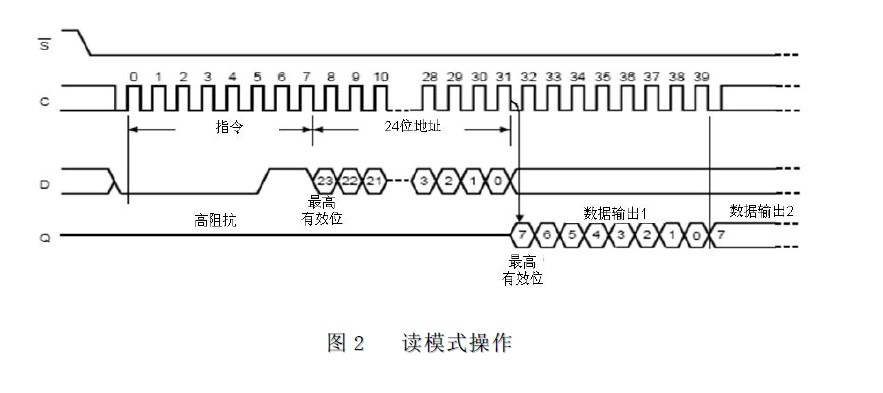

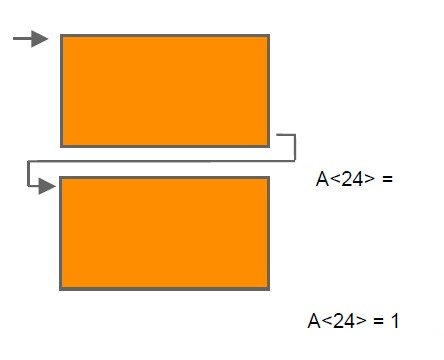

· 以传统方式写前3个地址字节(A[23:0]) (图2给出一个读存储器模式操作示例)。

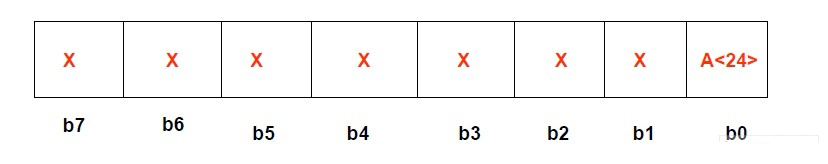

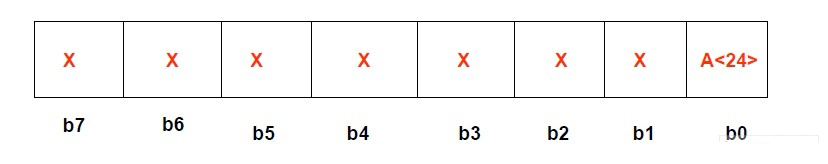

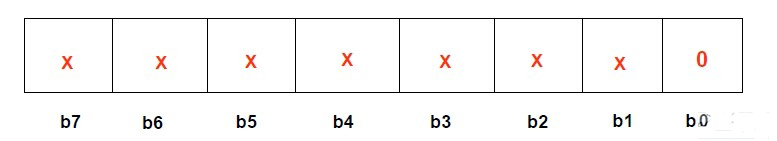

·第4个地址字节被预存在一个n位寄存器内。该寄存器具有以下特点:支持一条专用的写指令(C5h);以协议速度通信,是一个逻辑寄存器(触发器);默认条件(在上电后)是00h;在执行一条专用读存储器命令(C8h)后,可以查看寄存器内容;8位寄存器的最大寻址空间是32Gb,但是还可以扩展。

扩展地址寄存器的控制命令如图所示3 。

实例分析

1、以一个闪存为例:

· 256Mb可以视为2个128Mb闪存模块;

·所有默认操作都从最低有效位开始,除非EAR的0位被预置1。

2 、以一个闪存为例:

· 512Mb可以视为4个128Mb闪存模块;

·所有默认操作都从最低有效位开始,除非EAR的1位和0位被预置01或10或11。

128Mb以上的串行闪存被认为是电子产品满足市场需求、增加更多功能的一个主要障碍。针对需要128Mb以上串行闪存的应用要求,美光科技推出一个简单的独一无二的扩容解决方案。这个解决方案可以把存储容量轻松地扩大到4G或更大,完全兼容现有的串行外设接口(SPI)协议,无需重新设计主芯片的硬件。该解决方案优于市场上现有的要求创建一个新的32位寻址模式的解决方案,因为创建新的寻址模式可能强迫设计人员修改软硬件。

SPI协议的优点与局限

凡是在今天市场上销售的独立串行闪存都采用基于3个地址字节的SPI协议。SPI协议的数据祯由多个字节(8位)组成,主要包括:1)一个指示闪存操作的操作码(8位);2) 24位读写操作地址(3个字节) ,用于对所选存储区进行寻址;3) 如果写操作,在所选地址写入N x 8位数据(N = 1 … 256) 。SPI协议在嵌入式市场取得巨大成功,被所有的嵌入式串行闪存接受。升级应用无需修改硬件是在闪存内采用SPI协议的一个主要好处,因为不同闪存容量可以共用同一种封装和引脚排列方式(8引脚)。

不过,如果这个协议不能用于存储密度超过128Mb应用时,那么其优点就会荡然无存。因为SPI协议使用3个地址字节的祯通信,所以系统最大寻址空间被限制在128Mb。存储密度在256Mb或更高的闪存要求SPI协议增加额外的字节。协议的修改可能迫使所有的设计人员(特别是需要使用128Mb存储器的芯片组厂商)重新设计硬件。此外,若想把存储密度提高到256Mb或更高,他们无法升级现有的代码存储器为128Mb(3个地址字节)的应用。

增加存储密度的解决方案

因为这个原因,设计人员一直在寻找一个有效的解决办法,只需对软硬件稍加修改,即可把存储器密度提高到128Mb。有一个提议是开发一个支持更高寻址密度的32寻址模式,增加2种命令以解决24位与32位之间的转换问题。然而,这种方法需要在24寻址机制的基础上修改现有的软件,协议变化可能迫使设计人员重新设计主芯片的硬件。

美光科技的串口闪存产品阵容,存储密度从1/2Mb一直延伸到128Mb,现在该公司提出一个简单的解决方案,可以帮助设计人员解决存储密度提升问题。这个解决方案基于美光最新推出的N25Q256闪存,该方案的最大亮点是在采用相同的SPI协议情况下,不仅能够满足256Mb应用的需求,还能满足512Mb到32Gb的需求。

这个解决方案采用一个叫做扩展地址寄存器(EAR)的n-位寄存器,可以把寻址空间扩展到传统的3个字节(24位)以上。主机可以使用一个专用指令写寄存器(上电后寄存器进入00……0b默认状态)。这样,存储器被外部视为n个以128Mb为单位的存储段,该寄存器的内容可以对每个段进行寻址。

扩展地址寄存器

· 以传统方式写前3个地址字节(A[23:0]) (图2给出一个读存储器模式操作示例)。

·第4个地址字节被预存在一个n位寄存器内。该寄存器具有以下特点:支持一条专用的写指令(C5h);以协议速度通信,是一个逻辑寄存器(触发器);默认条件(在上电后)是00h;在执行一条专用读存储器命令(C8h)后,可以查看寄存器内容;8位寄存器的最大寻址空间是32Gb,但是还可以扩展。

扩展地址寄存器的控制命令如图所示3 。

实例分析

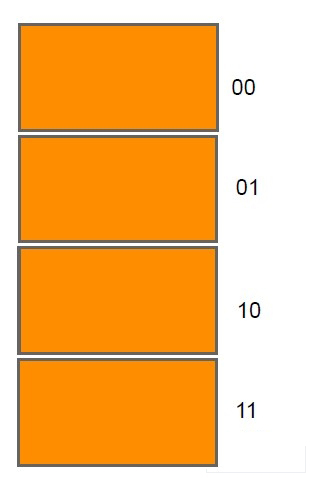

1、以一个闪存为例:

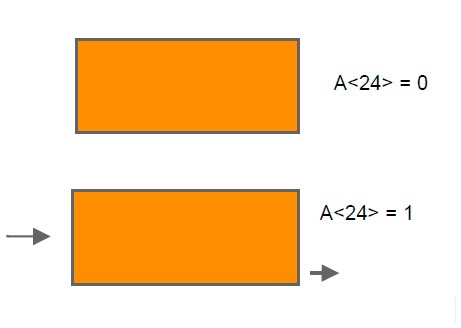

· 256Mb可以视为2个128Mb闪存模块;

·所有默认操作都从最低有效位开始,除非EAR的0位被预置1。

2 、以一个闪存为例:

· 512Mb可以视为4个128Mb闪存模块;

·所有默认操作都从最低有效位开始,除非EAR的1位和0位被预置01或10或11。

3、在闪存内的快速读操作示例

第1种情况从第1个存储块开始寻址:

· 开始串行输入:0Bhex + 3个地址字节 + 1个假时钟周期字节;

· 输出端将收到128Mb以下闪存的从所发送的3个地址开始的数据;

·如果芯片保持选择状态,地址数值在内部自动加1,输出数据还能与超过128Mb的存储空间关联 (用同一个指令可以把整个 256Mb内容下载)。

第2种情况从第2个存储块开始寻址:

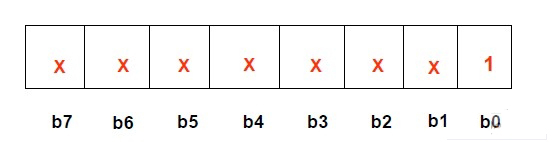

· 开始第1个串行输入:WEAR指令(C5h) + 1个数据字节(xxxxxxx1b);

·开始第2个串行输入:0Bhex + 3个地址字节 + 1个假时钟周期字节;

· 输出端将收到128Mb以上闪存的从所发送的3个地址开始的数据;

·如果芯片保持选择状态,地址数值在内部自动加1,输出数据还能与小于128Mb的存储空间关联 (存储器地址反转机制在整个 256Mb内有效);

·从现在起,发送的所有指令都与128Mb以上的空间关联,直到发送一条新的WEAR指令(数据字节 = xxxxxxx0b)为止。

本文小结

从设计角度看,扩展地址寄存器是一个简单的解决方案。它完全兼容现有的SPI协议,支持128Mb以上的寻址空间(存储单元更小的闪存与超过128Mb的闪存可以共存在一条总线上,而且一个控制器可以访问两个存储器);软件修改量很小,硬件无需修改;存储容量直接扩大到4G或更高。