摘要:随着数字化生活的到来,数据采集系统在日常生活中的应用越来越显著。模拟信号和数字信号之间的转换已成为计算机控制系统中不可缺少的环节。较传统数据采集系统,以可编程逻辑器件实现的数据采集系统具有时钟频率高,内部延时小,速度快,效率高,组成形式灵活等特点。

关键词:CPLD;数据采集;VHDL;状态机

数据采集系统具有极强的通用性,可广泛应用于军事、工业生产、科学研究和日常生活中。随着计算机的普及,数据采集系统在日常生活中的应用越来越显著。由于基于DSP芯片的高速电子器件成本和制作工艺,以及高密集的技术含量,使得高速数据采集卡的价格昂贵。而复杂可编程逻辑器件(CPLD)能够将大量的逻辑功能集成于一个单片集成电路中,以其时钟频率高,内部延时小,速度快,效率高,组成形式灵活等特点在高速数据采集方面有着单片机和DSP无法比拟的优势。

1 设计思路

该系统由数据输入单元、数据处理单元、数据输出单元三大部分组成。其中数据输入单元是由状态机控制ADC0809实现。输入信号可以是各种形式,它可以是语音信号、调制后的电话信号、编码的数字信号、压缩的图像信号,也可以是各种传感器输出的信号。A/D能将模拟信号变换成数字信号,但必须满足香农采样定理,也就是为了保证不丢失信息的所有信息,采样频率必须高于输入信号最高频率的2倍。A/D变换后得到的数字信号输人到CPLD芯片;再由CPLD芯片对该数字信号进行各种数字信号算法的处理。经过处理后的数字信号再经过数/模转换器ADC0832将其输出。

2 系统各部分的功能及实现

2.1 数据输入电路

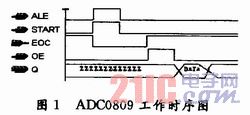

数据输入电路主要是由状态机控制ADC0809实现。其中START为转换控制信号,高电平有效;ALE是3位通道选择地址(ADDC,ADDB,ADDA)信号的锁存信号,高电平有效;EOC是转换情况状态信号(类似于AD574的STATUS),当启动转换约100 μs后,EOC产生一个高电平,以示转换结束,转换期间一直处于低电平。一旦START有效后,状态信号EOC即变为低电平,表示进入转化状态。转换结束后,EOC将变为高电平。OE为数据输出允许信号,当OE为高电平时,则控制打开三态缓冲器,把转换好的8位数据结果输至数据总线。其工作时序如图1所示。

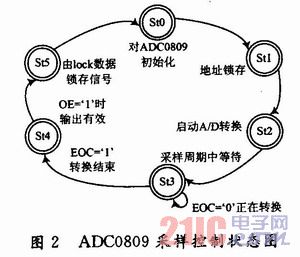

对ADC0809的工作过程分析可知:其工作处于6个状态。在状态St1中,ALE高电平将ADC0809的8路采样输入通道地址存入ADC0809地址锁存器中。在状态St3中需要对ADC0809工作状态信号EOC进行循环检测,如果为低电平,表示转换没有结束,仍需要停留在St3状态中等待,直到EOC变成高电平后才说明转换结束,在下一时钟脉冲到来时转向状态St4。在状态St4,由状态机向ADC0809发出转换好的8位数据输出命令,这一状态周期同时可作为数据输出稳定周期,以便能在下一状态中向锁存器中锁入可靠的数据。在状态St5,由状态机向CPLD中的锁存信号(LO-CK的上升沿),将ADC-0809输出的数据进行锁存。其采样控制状态图如图2所示。

2.2 数据处理电路

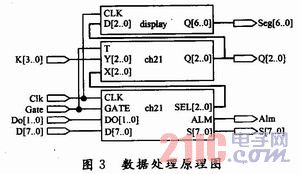

数据处理电路通过VHDL程序实现,该电路的主要功能是对外部输入信号进行循环检测,当k1为1时,该器件处于数据采集和处理模式。这里的数据处理就是对其输入的数字信号进行扩大2倍或缩小到原来的1/2,其中fun用来选择输入方式。在采集数据的时候还可以选择所采数据是ADC0809中的哪一路,并完成在七段数码器上显示。其原理如图3所示。

2.3 数据输出电路

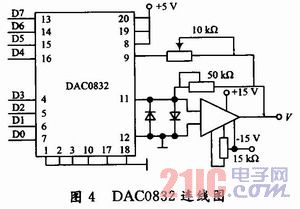

数据输出电路由数/模转换器DAC0832实现,ADC0832为8位分辨率A/D转换芯片,其内部电源输入与参考电压的复用,使得芯片的模拟电压输入在0~5 V之间。D/A转换结果采用电流形式输出。应得到相应的模拟电压信号,所以通过一个高输入阻抗的线性运算放大器实现。其连线如图4所示。

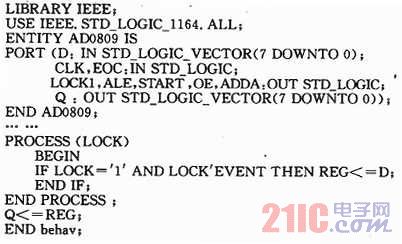

3 电路的VHDL描述

数据采集控制电路、数据处理电路均是使用硬件描述语言VHDL(Very High Speed Integrated Circuit Hatdware Description Langu-age)设计而成。例如:数据采集控制模块设计如下:

VHDL语言具有多层次的电路设计描述功能,既可描述系统级电路,也可以描述门级电路;描述方式既可以采用行为描述、寄存器传输描述或者结构描述,也可以采用三者的混合描述方式。VHDL语言的强大描述能力还体现在它具有丰富的数据类型,采用VHDL语言描述硬件电路时,设计人员并不需要首先考虑选择进行设计的器件。这样做的好处是可以使设计人员集中精力进行电路设计的优化,而不需要考虑其他的问题。当硬件电路的设计描述完成以后,VHDL语言允许采用多种不同的器件结构来实现。

4 系统的波形仿真

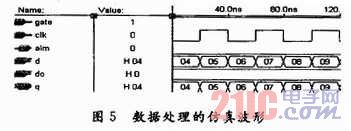

在数据处理电路中,当gate=‘1’,整个器件处于数据采集及处理模式,选择不同的工作方式,即fun值,可实现不同的数据处理,当do为O时,其波形仿真如图5所示。从仿真波形中可以看出输入数据等于输出数据,在通过输出运放,使输出值增大2倍,从而使输出数据为输入数据的2倍。

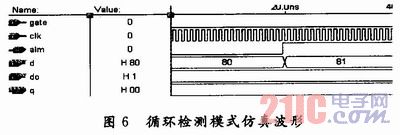

在数据处理电路中,当gate=‘0’,整个器件处于循环检测的模式,当输入数据超出预设值时就进行报警,即alm=‘1’,当无输入值大于预设值时,就进行循环检测。其波形仿真如图6所示。

5 结语

设计了基于CPLD的多路异步数据采集系统,系统中使用状态机控制数据的采集,使用ADC0832进行数/模转换。同时利用CPLD强大的数字处理功能和高密集成的特点,降低了硬件的成本,简化了电路设计,并配合软件增加了系统的灵活性和可扩充性,具有很好的经济效益和社会效益。