数字正交上变频器AD9856的原理及其应用

2008-12-22

作者:陈国庆 吴恩德 高文焕 王志华

摘 要: 介绍了数字正交上变频器AD9856的工作原理及使用方法,并给出了其在数字音频广播(DAB)发射系统中的具体应用。

关键词: 数字正交调制" title="正交调制">正交调制 上变频 DAB

正交调制是一种常用的调制技术。在以往的通信系统中,一般都由模拟电路实现,由于很难保证两路载波的正交性,调制的效果往往不太理想,因而逐渐被数字调制所取代。AD9856是AD公司生产的一种通用、高性能的数字正交上变频器件,具有集成度高、性能好、体积小、功耗低等特点,使用该器件很容易实现信号的数字正交调制。

1 AD9856的结构和工作原理

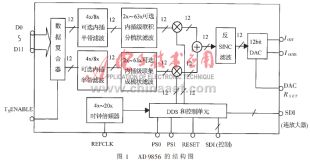

AD9856内部电路结构如图1所示。主要分为数据复合、过采样" title="过采样">过采样滤波、正交调制、数模转换和控制电路等单元。

1.1 数据复合

AD9856内部的数据格式是12bit" title="12bit">12bit的二进制补码。但数据输入接口能支持3种字长:12bit(D11~D0),6bit(D11~D6),3bit(D11~D9)。因此需要一个数据复合器将输入的数据进行复合,形成12bit的统一格式。另外,基带信号的I、Q分量是交替输入的,所以数据复合器还需对输入数据进行识别,将其转换成I、Q两路并行数据流,送往下一级电路。

1.2 过采样滤波

由数据复合器输出的并行I/Q数据流需经过滤波器进行过采样。AD9856的过采样滤波器分为两级:半带滤波器(HBF)和级联积分梳状(CIC)滤波器,它们都具有低通的频响特性。而HBF又分为三级:HBF1、HBF2、HBF3,其中HBF3是可选的。

每一级HBF可使数据的采样率提高一倍。为了使信号频带处于滤波器通带的平坦部分,就要提高HBF的截止频率。也就是说数据在输入AD9856之前要进行过采样。一般情况下,两倍的过采样率已经足够。

AD9856中的CIC实际上是一个可编程的过采样滤波器,过采样率的范围是:2≤R≤63。随着R的改变,CIC会引入不同的插入损耗。为了补偿这一损耗,用户可以设置CIC增益位,使得CIC的输出增大一倍。但在这种工作模式下,必须确保输出信号不会溢出。

1.3 正交调制

AD9856的正交调制就是将基带信号的频谱频移到所需要的载波频率上(即通常所说的上变频)。正交调制所需要的余弦、正弦两路数字载波由一个高速的直接数字综合器(DDS)产生,其频率可通过设置相应的寄存器来控制。这两路数字载波分别与CIC输出的I、Q两路数据相乘,然后再相加或相减,即得到调制后的数字中频信号。

CIC输出的I/Q数据的采样率与DDS数字载波的采样率是相同的,也就是AD9856的系统时钟频率(SYSCLK)。所以调制后的信号实际上是一组采样率为SYSCLK的数据流。

1.4 数模转换

调制后的数字信号要经过一个12位的DAC,转换成模拟信号。DAC通过零阶保持实现数模转换。由于零阶保持效应,其输出信号的频谱实际上是被SINC包络加权过的。因此需要在DAC前面加上一个反SINC型滤波器(ISF),对输入数据流进行预处理,以校正SINC包络造成的失真。

数模转换过程会在n×SYSCLK±FCARRIER(n=1、2、3)处产生干扰信号,这些干扰信号可以通过一个外接RLC滤波器滤除。一般情况下,使用一个7阶椭圆低通滤波器即可。AD9856提供两路互补的两个电流输出,输出电流的满额值IOUT范围是5~20mA,可通过电阻RSET来设置,关系为:

RSET=39.936/IOUT

1.5 控制单元

AD9856提供了一个灵活的同步串行通信端口,该串口" title="串口">串口与绝大多数同步传输格式(例如Motorola 6905/11 SPI 和Intel 8051 SSR协议)相兼容。所以很容易实现与微控制器或微处理器的接口。这个接口可以读写AD9856的所有寄存器。

控制单元根据各个寄存器的内容,设置AD9856的工作模式。AD9856还提供了一个与AD8320(可编程电缆驱动放大器)进行通信的串口。控制单元可以通过这个串口直接设置AD8320的增益。

2 AD9856的使用方法

2.1 时钟设置

AD9856内部时钟都是由基准时钟(REFCLK)倍频或分频产生的,输入数据的采样时钟也必须与基准时钟同步,所以整个系统的各个时钟频率之间都有严格的整倍数关系,以保证系统正常工作。定义fW为K-bit字(K=3、6、12)的输入频率。则fW与REFCLK、SYSCLK之间的关系为:

SYSCLK=REFCLK×M=(2HNfW)/I (1)

其中H、N、I、M为整数并定义如下:

H=1为HBF3旁路

H=2为HBF3选通

M=1为REFCLK倍频旁路

4≤M≤20为REFCLK倍频选通

I=1为12bit字输入

I=2为6bit字输入

I=4为3bit字输入

N=CIC内插率(2≤N≤63)

DDS产生的载波频率不能超过SYSCLK的40%。SYSCLK最高可达200MHz,因此载波频率不能超过80MHz。用户应根据输入数据的采样率,选择一精确的REFCLK。并根据要求的载波频率选定时钟倍频系数M,使SYSCLK足够高。而其他系数的确定则需满足(1)式。

2.2 输入数据格式

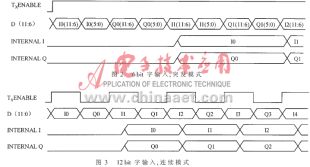

AD9856提供了两种输入数据的时序模式:突发模式" title="突发模式">突发模式和连续模式。在突发模式下,AD9856通过TXENABLE的上升沿来保持与输入数据的同步。突发模式支持全部三种字长(12bit,6bit,3bit)。对于连续模式,TXENABLE可以看成数据输入时钟。该信号除了用来同步外,还可以指示输入数据是I路还是Q路(1表示I路,0表示Q路)。连续模式只支持12bit字长。图2、3描述了两种输入格式的时序关系,其中INTERNAL I和INTERNAL Q为数据复合器所产生的并行的I和Q数据流。

在选择输入模式时,有以下几点需要注意:

①在3bit字输入的突发模式下,HBF3一定要选通。

② 在突发模式下,当TXENABLE为低的时间超过1个采样周期时,数据复合器的I和Q两路都输出0。

③ 在连续模式下,当TXENABLE为低或高的时间超过1个采样周期时,会分别造成I路或Q路数据的丢失。

2.3 控制串口操作

AD9856的一个串口通信周期可分为两部分:指令周期和数据传输周期。在指令周期,外部控制器向AD9856写入一个指令字节。指令字节给出了将要进行的数据操作所需的信息,如表1所示。在数据传输周期,控制器根据指令字节所给的信息对AD9856进行相应的数据操作。

: 定义数据操作类型,1为读,0为写。

: 定义数据操作类型,1为读,0为写。

N1、N0: 要传输的数据的字节数(00b=1字节,01b=2字节,10b=3字节,11b=4字节)。

A4~A0:被访问寄存器的地址,多字节传输时,该地址为起始地址,其余地址由AD9856的控制器产生。

AD9856的串口管脚包括SCLK、 、SDIO、SDO和SYNC I/O。AD9856在SCLK的上升沿锁存SDIO上的输入数据,在SCLK的下降沿给出输出数据。输出数据既可出现在SDIO上,也可出现在SDO上。在每一个通信周期内,最初的8个SCLK上升沿用来写指令字节,剩下的SCLK沿用于数据传输。图4给出了SDIO设置成双向时的串口读写时序。

、SDIO、SDO和SYNC I/O。AD9856在SCLK的上升沿锁存SDIO上的输入数据,在SCLK的下降沿给出输出数据。输出数据既可出现在SDIO上,也可出现在SDO上。在每一个通信周期内,最初的8个SCLK上升沿用来写指令字节,剩下的SCLK沿用于数据传输。图4给出了SDIO设置成双向时的串口读写时序。

在进行串口操作时需要注意以下几点:

(1) 串口支持MSB在前和LSB在前两种格式,通过寄存器0的第6位设置。对该位的设置是立即有效的。即如果当前操作对该位进行修改,则下一个字节的传输就会采用新格式。

(2) 对多字节传输的通信周期,如果MSB在前,寄存器地址递减;如果LSB在前,寄存器地址递增。

(3) 外部控制器必须保持与AD9856同步,如果失去同步,可由SYNC I/O来重新产生同步,而不必对整个芯片复位。

2.4 寄存器功能

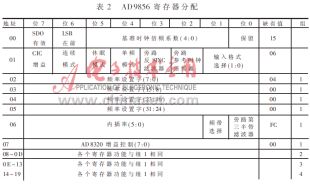

AD9856内部的寄存器如表2所示。

下面说明具体的功能:

(1)SDO有效:1表示串行数据由SDIO输出;0表示串行数据由SDO输出。

(2)LSB在前:1表示串行数据是LSB在前;0表示串行数据是MSB在前。

(3)基准时钟倍频系数:有效值范围为4~20。

(4)保留位:该位总为1。

(5)CIC增益:1表示级联积分梳状滤波器输出加倍。

(6)连续模式:1表示连续模式;0表示突发模式。

(7)休眠模式:1表示AD9856处于休眠模式,此时电流小于2mA。

(8)单频模式:置成1,则输出单频信号,频率由频率设置字确定。此时数据输入脚接固定高电平或低电平。

(9)旁路反SINC滤波器:1表示反SINC滤波器被旁路。

(10)旁路参考时钟倍频器:1表示参考时钟倍频器被旁路。

(11)输入格式选择(1:0):10b=12bit模式;01b=6bit模式;00b=3bit模式。

(12)频率设置字(31:0)FTW:其与载波频率fOUT及SYSCLK之间的关系为:

fOUT=(FTW×SYSCLK)/232

(13)内插率(5:0):确定级联积分梳状滤波器的内插率,允许范围为2~63。

(14)频带选择:为1时输出I×cos(ωt)+Q×sin(ωt),为0时输出I×cos(ωt)-Q×sin(ωt)。

(15)旁路HBF#3:1表示HBF#3被旁路。

(16)AD8320增益控制(7:0)Code:其与AD8320放大倍数AV的关系为AV=0.316+0.077×Code。

(17)组2,3,4:其功能与组1中各寄存器相同。通过管脚PS1、PS0来选择那一组寄存器有效。

2.5 AD9856对AD8320的增益控制

AD9856提供了一个与AD8320串口相连的接口。通过这个接口,AD9856可以直接控制放大器的增益。这一功能使得外部控制系统大大简化。AD9856只有在检测到以下三种情况时,才与AD8320进行通信。

(1)上电复位:在上电复位时,AD9856清除所有组的增益控制寄存器,并且往AD8320串口写全零,此时定义了放大器的最小增益。

(2)PS1和PS0改变:AD9856对PS1和PS0进行取样,当发现它们改变时,则将当前组内的增益控制寄存器内容写入到AD8320中。

(3)增益控制寄存器内容改变:当AD9856任一组中的增益控制寄存器被更新时,它都将当前组的增益控制寄存器的数据写入AD8320。

3 AD9856在DAB发射系统中的应用

DAB是继调幅、调频广播之后的第三代广播方式,具有音质好、抗干扰能力强等优点。我国于1996年将其列为重大科技产业项目,并决定采用欧洲的Eureka147标准。该标准采用编码正交频分复用(COFDM)传输方式。节目源的音频数据经复接器复接成ETI(Ensemble Transport Interface)帧,然后送入COFDM符号发生器,产生采样率为2.048MHz的I、Q两路数字基带信号,每一路的信号带宽为0.768MHz。基带信号一般先要正交调制到中频,然后再上变频到所需要的射频,经发射机发射出去。

图5给出了用AD9856实现的DAB中频正交调制器的框图。其中的AT89C2051为系统控制器,AD8320为放大器。

DAB标准中规定,I/Q数据的采样值为8bit二进制补码。因此在设计方案中,输入模式采用12bit字的突发模式。AD9856的高8位数据线(D11~D4)接输入数据,而低4位数据线(D3~D0)接地。因为输入信号的每路带宽仅为0.768MHz,基本上全部落在AD9856内部过采样滤波器通带的平坦区域内,所以输入数据在送往AD9856之前不需要过采样。

输入数据采样率为2.048MHz,为保障AD9856内部时钟关系,REFCLK取采样时钟的4倍频,即8.192MHz。SYSCLK为REFCLK的20倍频,即163.84MHz。中频载波设为36MHz,在SYSCLK的40%范围内。选通HBF3,CIC内插率设成10,以满足(1)式。

单片机AT89C2051的P1.0、P1.1接AD9856的PS0和PS1,选择AD9856的当前有效寄存器组。P1.2~P1.6接AD9856控制串口的各个管脚,按照图4给出的时序,即可对AD9856 内部寄存器进行读写操作。输出负载为简单的接地电阻。滤波器为5阶椭圆低通滤波器,截止频率为38MHz。

该中频正交调制器结构简单,易于调试,且调制参数可根据需要进行设置,在实际应用中效果良好。

参考文献

1 AD9856 Data Sheet. Analog Devices Inc.、1999

2 AD8320 Data Sheet. Analog Devices Inc.、1998

3 曹志刚,钱亚生. 现代通信原理. 北京:清华大学出版社,1992