一、硬件电路设计

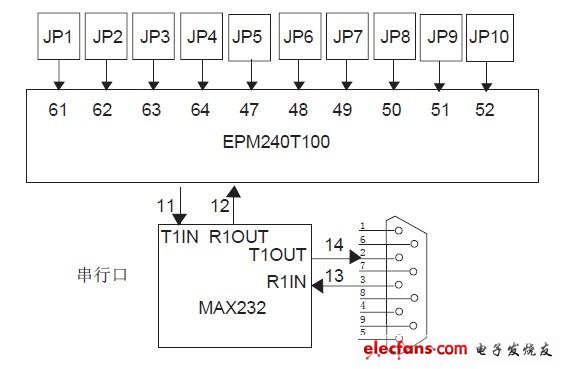

本文选用CPLD 是ALTERA 公司的EPM240T100,结合MAX232 接口芯片进行串口通信设计,框图如下图1 所示。

图1 CPLD串口通信模块硬件设计

二、VHDL程序模块设计及描述

使用VHDL 对CPLD 进行编程,设计3 个模块,波特率发生模块,接收器,发送器。

1. 波特率发生模块

波特率发生器实际是一个分频器,如前所述,本文设计的波特率为19.2kb/ 秒,设计使用的时钟频率为10MHz,所以计数器进行计数时计数到260进行翻转。

程序如下(关键部分保留,非必要部分用……代替):

……

ENTITY uart IS

GENERIC(d_len:INTEGER:=8);

PORT (

f10MHz:IN STD_LOGIC;-- 系统时钟

reset:IN STD_LOGIC;-- 复位信号

rxd:IN STD_LOGIC; -- 串行接收

txd:OUT STD_LOGIC;-- 串行发送

);

END uart;

ARCHITECTURE behav of uart IS

……

BEGIN

rxds<=rxd;

PROCESS(f10MHz,reset)

-- 设置波特率发生器 19200kb/s

VARIABLE clk19200hz: STD_LOGIC;

VARIABLE count:INTEGER RANGE 0 TO 260;

BEGIN

IF reset='0' THEN

count:=0;

clk19200hz:='0';

ELSIF f10MHz'EVENT AND f10MHz='1' THEN

IF count=260 THEN

count:=0;clk19200hz:= NOT clk19200hz;

ELSE

count:=count+1;

END IF;

END IF;

baud_rate<=clk19200hz;

END PROCESS;发送模块e#2. 发送模块

发送部分采用状态机t_state 进行编程,共设两个值:t-start 和t_shift,分别表示发送开始以及发送保持状态。复位键按下时设置到t-start 状态,并将发送数据位设为“1”, 发送的数据位数计数为0,在t-start 状态,状态机将处于这一个状态并等待波特率计数信号的电平上升沿到来。上升沿到来时,依据t_state 状态的不同值做不同处理,如果是t-start 开始状态则先读待发送的数据,并发送开始位“0”,然后将状态转到发送保持t_shift 状态,在发送保持t_shift 状态,不断判断发送的数据位数是否满8 位,如果满了则回归t-start 状态,否则继续发送,保持在t_shift 状态,为避免干扰将其余情况下的状态自动跳转到t-start 状态。程序如下:

PROCESS(baud_rate,reset,data)

-- 数据发送部分

VARIABLE t_no:INTEGER RANGE 0 TO 8;

-- 发送的数据各位的位序号

VARIABLE txds:STD_LOGIC;

VARIABLE dtmp:STD_LOGIC_VECTOR(7

DOWNTO 0);

BEGIN

IF reset='0' THEN

t_state<=t_start;

txds:='1';

t_no:=0;

ELSIF baud_rate'event AND baud_rate='1' THEN

CASE t_state IS

WHEN t_start=>

dtmp:=data;

txds:='0'; -- 发送开始

t_state<=t_shift;

WHEN t_shift=> IF t_no=d_len THEN

txds:='1'; -- 发送结束

t_no:=0;

t_state<=t_start;

ELSE

txds:=dtmp(t_no); -- 发送一字节数据

t_no:=t_no+1;

END IF;

WHEN thers=>t_state<=t_start;

END CASE;

END IF;

txd<=txds;

END PROCESS;

3. 数据接收模块

接收部分采用状态机进行编程,共设两个状态:

r-start 和r_shift 分别表示接收开始以及接收保持状态;复位键按下时设置到r-start 状态,并将待接收存放数据的data 赋值为“00000000”, 在r-start状态,接收状态机将处于这一个状态并等待波特率计数信号的电平上升沿到来。波特率发生模块的计数上升沿到来,依据状态的不同值做不同处理,如果是r-start 接收开始状态则等待开始位信号,检测到rxds=‘0’的开始位信号好转到r_shift 接收保持状态,r_shift 接收保持状态会不断判断接收的数据位数是否满8 位,如果满了则回归r-start 状态,否则继续接收,保持在r_shift 接收保持状态,为避免干扰将其余情况下的状态自动跳转到r-start 接收开始状态,程序与发送部分类似,此处省略。

三、串口通信的VHDL程序仿真结果

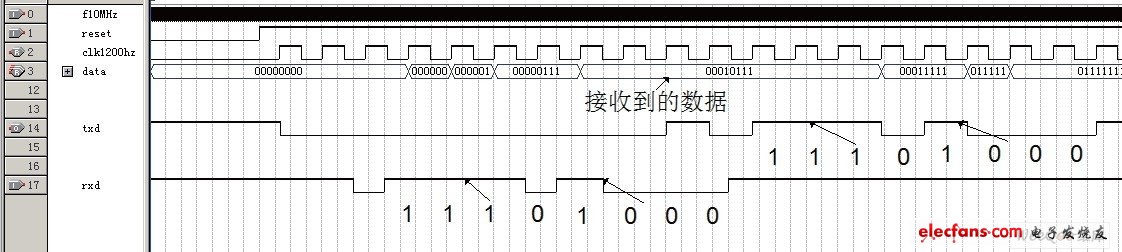

串行口通信的仿真结果如图2 所示。从图中可以看出,每发送完一个字节,即8 位数据后,线路上将输出一个高电平,之后又开始传送下一个字节。

同样,仿真波形显示,有效数据到达接收管脚rxd之前,线路上保持为高电平,直到收到一个低电平起始位,将该起始位后的8 位数据串行接收后依次送到保存接收结果的信号data 的各位。

图2 串行口通信仿真波形图

串口通信的硬件验证

将程序通过在系统编程下载入配套的CPLD 电路板进行硬件验证,按照以下步骤进行。

(1)确定管脚对应关系:

串行接收管脚rxd 与max232 的12 脚R1OUT对应; 串行发送管脚txd 与max232 的11 脚T1IN对应;复位信号reset 与按键S1 对应。

(2)由QUARTUS II 进行管脚分配:

f10MHz 在MAXII 芯片上对应的管脚号为12 ;S1 在MAXII 芯片上对应的管脚号为21 ; rxd 在MAXII 芯片上对应的管脚号为89; txd 在MAXII 芯片上对应的管脚号为90。

(3)电平定义:

按键S1 按下时表示输入信号为低电平。

应用“ 串口调试助手” 进行验证, 在发送窗口随机输入需要发送的字符,可以发现由PC 机发给CPLD 的字符被CPLD 传送回来并在接收窗口显示出来。在批量随机数据发送后分析:在传输时19.2kb/s 传输速率下,误码率达10-8。