在PAL→VGA的实时视频采集系统中,由于视频数据流的数据量大、实时性要求高。需要高速大容量的存储器作为图像数据的缓存。SDRAM作数据缓存不仅具有大容量和高速度的特点,而且在价格和功耗方面也占有很大的优势。但是SDRAM控制较复杂,需要处理预充、刷新、换行等操作,因此有必要设计SDRAM控制器来完成和SDRAM的接口。并且为了保证数据流的连续性,实时视频采集系统通常采用通过对两片SDRAM的乒乓操作来完成图像数据的缓存。针对SDRAM是高速设备,工作频率上限最高可以达到166 MHz,而该系统中前端图像采集模块的像素时钟为27 MHz,后端VGA显示的像素时钟为31.5 MHz。在此介绍了一种使用1片SDRAM的不同BANK进行乒乓操作,且相对容易实现的SDRAM控制器设计方法。

1 SDRAM基本操作原理

SDRAM的主要操作包括初始化、读写访问、刷新、激活、预充电等。以MICRON公司的MT48LC4M3282(1M×32 b×4 BANKS)为例,简要介绍一下SDRAM的操作。

如图1所示,SDRAM的初始化操作过程如下:

(1)在电源管脚上电(电压不得超过标称值的0.3 V)并且时钟稳定后经过200μs延迟,执行一次空操作命令(该命令在延迟周期的后期发出)且保持时钟使能信号为高;

(2)对所有的BANK进行预充电,所有的BANK都进入空闲状态;

(3)预充电后执行两个自动刷新命令,等待八个刷新周期完毕;

(4)发出模式设置命令来设置模式寄存器。由于上电后模式寄存器的状态是不确定的,所以在进行SDRAM操作之前一定要先设置模式寄存器。模式寄存器设置值如图2所示。

对SDRAM的读写访问先要以激活命令选择具体的BANK和行,地址线BA1/BA0用来选择BANK,A0~A11用来选择所要访问的行;然后发出读或写命令,地址线A0~A7用来选择所要访问的起始列。在读命令发出后,要等待一个CAS延迟时间,有效数据才会出现在数据总线上,CAS延迟时间可以设置为2或3个时钟。在写命令发出后,不需要等待CAS延迟时间有效数据会立即出现在数据总线上。对SDRAM的读写操作一般以突发模式进行,突发长度可以设置成1,2,4,8以及全页,常用的长度为8个。该系统的CAS延迟时间设置为2,突发长度为1。

SDRAM的存储单元可以理解为一个电容,总是倾向于放电,必须有定时的刷新周期以避免数据丢失。只要保证在64 ms时间内所有有效数据行都完成刷新就可以保证数据不丢。SDRAM提供两种类型的刷新模式:自动刷新和自刷新。在该系统中,前端PAL制式信号一帧的时间为40 ms,因此SDRAM的同一地址读写操作的时间相隔为40 ms。又由于系统为实时视频采集系统,前端采集的视频数据是连续不断的,所以该系统不需要进行刷新操作即可保证数据不丢。

2 SDRAM控制器的设计实现

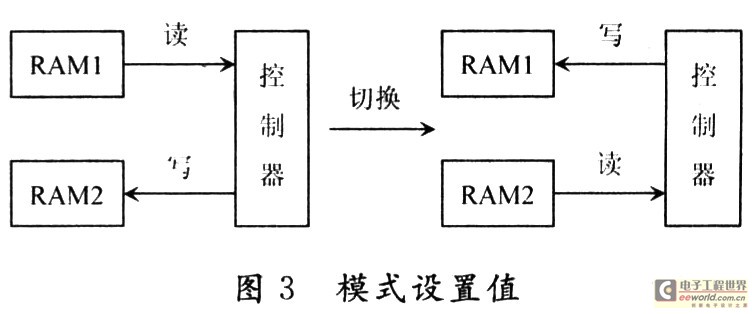

在实时视频采集系统中,为了保证数据的稳定和连续性,通常采用的方法是对存储器进行乒乓操作。一般所指的乒乓操作针对两片存储器芯片,如图3所示,其原理是通过控制模块对两片存储器分别做读写操作,写存储器满时控制模块发出交换命令,切换两片存储器的操作状态。

该系统采用的是一片SDRAM实现乒乓操作。设计时是利用SDRAM的不同BANK间的存取操作来实现乒乓操作。由于SDRAM总共有4个BANK,所以读取第一帧图像时使用SDRAM的1,2 BANK为读缓存,3,4 BANK为写缓存。第二帧图像时SDRAM的3,4 BANK切换为读缓存,1,2 BANK切换为写缓存。采用一帧图像读写完毕作为切换标志反复切换读写缓存,就充分利用SDRAM的不同BANK来实现乒乓操作。另一方面由于SDRAM的数据线和地址线只有1组,所以实际控制的时候读写操作是不能同时进行的。设计中考虑到SDRAM的工作频率与前端图像采集的像素频率以及后端VGA显示的像素频率相比要高得多,因此将读写操作利用时分的方式分开控制。所以在控制器中设计了一个指令计数器(Countcmd),通过计数的方式来切换读写操作。只要选取适当的SDRAM工作频率以及指令计数器的规定值就可以完成SDRAM读写操作的连续切换。实际设计中采用的SDRAM工作频率为100 MHz,指令计数器的规定值为240。SDRAM控制器状态转换概图如图4所示。

SDRAM控制器的具体状态转换流程如下:首先初始化SDRAM,然后向SDRAM的1,2 BANK写入第一帧图像,当第一帧图像写入完毕后进入乒乓操作阶段。此时SDRAM的1,2 BANK为读缓存,3,4 BANK为写缓存。

首先进入读缓存激活行,开始读操作,读操作开始的同时启动指令计数器。此时每执行一条指令(包括读指令,空操作指令,不包括预充电指令和行激活指令),指令计数器自加1,当指令计数器到达规定值时将指令计数器清0并切换到写状态。进入写状态前先判断写缓存的行激活标志,如果没有激活,先执行行激活,然后开始写操作,如果已经激活则直接开始写操作。写操作开始的同时启动指令计数器。此时和读状态时一样,每执行一条指令,指令计数器自加1,当指令计数器到达规定值时同样将指令计数器清0后切换到读状态。如此反复切换操作,直至读完一帧或者写满一帧。如果是读完一帧,则判断写缓存中一帧写满没有。如果已经写满,则进入读写BANK切换状态。如果没有,则进入写状态并不再切换读写状态,一直保持写状态直至写满一帧为止,然后进入读写BANK切换状态。如果是写满一帧,则同理于读完一帧的情况,首先判断读缓存中读完一帧没有,然后根据判断结果进行操作,最后进入读写BANK切换状态。在读写BANK切换状态中,读缓存切换为3,4 BANK,写缓存切换为1,2 BANK。反复上述操作步骤,就可以完成使用一片SDRAM不同BANK的乒乓操作。整个SDRAM控制器在Altera的QuartusⅡ7.2环境下采用Verilog设计完成,然后在ModelSim SE 6.0环境下仿真通过。随后通过Altera的QuartusⅡ7.2进行综合和布局布线,并最终在Al-teraCyclone系列FPGA芯片EP1C6Q240C8上完成。所设计的SDRAM控制器在PAL→VGA的实时视频采集系统中调试通过,能够实现图像数据的存储和读取,完全满足系统的要求。

3 结 语

介绍在PAL→VGA的实时视频采集系统中使用SDRAM作为图像缓存的基本操作,设计一种使用1片SDRAM的不同BANK进行乒乓操作的相对容易实现的SDRAM控制器设计方法。在PAL→VGA的实时视频采集系统中,使用了所设计的SDRAM控制器,并通过硬件验证,采集得到的图像质量较好。另外,这里设计的SDRAM控制器稍加改动就可以应用到其他实时视频采集系统中去,具有很强的通用性。