关键字:数字射频技术" title="数字射频技术">数字射频技术

消费者已经开始将手机作为便携式娱乐终端,集成越来越多的功能与减小手机尺寸、增长电池寿命形成矛盾。解决这个问题的最好办法是从射频部分入手,本文介绍的数字射频技术能有效地降低射频部分的功耗和尺寸。

手机设计工程师希望在不影响电路板面积、耗电量和成本的前提下增加更多消费者想要的功能,最有可能实现此目标的方法是从手机射频电路着手。射频电路大都是模拟器件,不但可能占用高达五成的电路板面积,耗电量也颇为可观。事实上,由于射频器件所需的电路板空间实在太大,当设计工程师为了整合蓝牙、电视、辅助全球定位系统(A-GPS)、无线网络或其它功能而必须在手机中增加无线电电路时,总会发现除了加大产品体积外几乎别无选择。另外,增加射频器件必然会增加耗电量和成本。

图1:黄线部分代表的射频收发相关功能约占

手机电路板器件总数的三分之一。

要解决这个两难的困境,关键在于不增加器件就能扩大手机功能的技术,而且要尽量提高核心器件的工作效率,让手机增加很少的电路板面积、耗电量和成本就能执行更多的无线电操作。

数字射频技术

德州仪器(TI)的数字射频(DRP)技术正朝此目标迈进,它所能节省的电路板面积、耗电量和成本对手机设计工程师具有极大的意义。DRP技术的目标在于让模数转换和数模转换功能尽量靠近天线,同时以数字方式执行初始滤波以外的所有处理工作。这种做法既可提高性能,又能减少约一半的电路板空间、硅芯片面积和功耗。

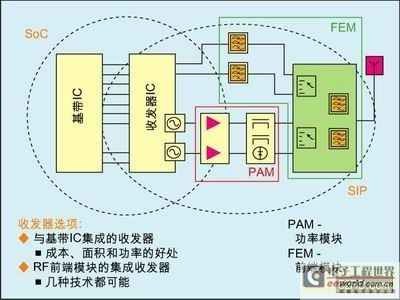

许多设计工程师选择系统级芯片(SoC)和系统级封装(SIP)来开发手机。SIP可将半导体器件层叠封装在一起以节省电路板面积,现已成为多数射频前端电路的最佳选择。功率放大器、声表面波滤波器、射频开关和相关无源器件则最适合采用系统级封装模块。另一方面,透过深亚微米CMOS工艺技术把射频收发器以及系统基频处理功能集成为SoC也会带来许多好处,包括可以减少耗电量、成本、电路板面积和测试成本,同时提高性能、手机制造良率以及加速测量、。

深亚微米逻辑工艺提供极高的逻辑电路密度和频率,设计工程师希望能利用SoC发挥这种工艺技术的优点。虽然这表示工程师可能要为深亚微米CMOS工艺发展新型无线电架构,但它确实为设计工程师带来许多重大好处。其中最重要的就是随着CMOS晶圆工艺技术进步而导致开关速度不断加快,这些器件也能提高它们的采样速率。输入信号的超采样可以减少混叠噪声(aliasing)问题并放宽输入电路的设计要求,设计工程师可以采用更复杂的滤波技术,并且在更靠近天线的位置执行模数转换。除此之外,SoC的集成也能提高系统生产良率,这是因为有更多功能改由逻辑电路实现,它们不像模拟射频电路会受到参数良率损失的影响。利用尺寸更小的先进工艺技术设计无线电功能还可减少电路板尺寸和硅片面积。

数字无线电技术只需少数无源器件,所以只要将收发器和数字基带处理功能集成在一起就可大幅减少电路板面积。高集成度SoC的成本有时虽略高于分立器件,但器件数通常也较少,使得产品的设计、测试和调试成本都能大幅下降。设计复杂性的降低还能加快新产品上市时间,这是高集成度器件的另一项附带的好处。

减少系统器件会降低功率需求,但大幅降低耗电的关键仍在于数字逻辑的耗电量非常小,CMOS工艺的功耗也远低于其它工艺,如特殊模拟器件常用的SiGe BiCMOS技术。事实上,90纳米CMOS技术早就用于实际生产,65纳米已有样品供应,45纳米工艺的发展也有一段时间。相比之下,SiGe BiCMOS还无法将电路结构尺寸缩小到如此程度,目前多数SiGe射频器件仍在使用180纳米技术。

数字射频技术的发展

数字CMOS技术是在最近几年才将时钟速度提高和耗电量降低至一定程度,使得射频信号的数字处理得以实现。利用数字技术处理射频信号时,时钟速度必须等于无线电频率,例如蓝牙应用的频率就高达2.4GHz。由于个人计算机和DSP的速率早已超过此水平,设计工程师现在已能将数字处理用于无线射频器,利用到数字处理技术的优势。

图2:无线电功能整合的可能选项。

随着工艺技术日益精密,数字工艺很容易就制造出更小的电路结构。然而无线电单元如前所述总是会有些模拟电路,要将它们完全消除就必须采用全新的无线电架构,系统设计也需要适度修改。尽管如此,这些无线电通常仍很容易升级到更先进工艺,因为它们的电路多半已是数字电路。

为了达到模拟和射频电路的某些严苛要求,DRP设计会将模拟电路的部份功能转移到数字电路,这让SoC也能采用90纳米或65纳米的CMOS工艺,厂商还能利用标准CMOS流程制造电阻和电容等模拟与射频整合所需的大部份器件,进而降低成本并提高功能集成度。

在我们的先进技术中,是以铜作为连接导线,铜的良好导电性最适合将电感和电容等无源器件集成在一起。采用多层导线的新型3D电容设计可在更小面积上制造出更大电容,顶部厚金属层不但将数字电源总线的IR压降减至最小,还能提高集成电容的Q值。

有了速度超快的CMOS射频器件,设计工程师不再需要某些要求严格的模拟滤波器。多数滤波器功能现在可由数字电路提供,使得功耗和芯片面积变得更小。CMOS射频器件只需很少的功率来开启和关闭阻抗固定的线性开关,这对于开关电容(switched capacitor)电路、混频器、开关电源、稳压器无源组件和D类放大器的设计都有极大帮助。

采样数据技术是避免使用高性能无源器件的方法之一。由于采样动作必然会导致频率变换,信号下变频将变得更容易。只要采样电容完成输入信号波形获取,我们就能轻易将多个电荷样本值结合在一起。在相同电容上对一个波形的多个采样可以实现简单的移动平均滤波器。采用这种方式,设计工程师还能很容易地开发出其它更复杂的FIR和IIR滤波器,还能藉由各种方法处理模数转换功能,同时利用数字信号处理技术进一步处理信号。

随着CMOS工艺的开关速度加快,器件也能以更高速率采样。输入信号超采样可以减少噪声混叠问题和放宽输入电路的设计要求,设计工程师可采用更复杂的滤波技术,在更靠近天线的地方进行模数转换,同时把更多的信号处理操作交给数字电路,以便充分利用逻辑工艺不断缩小所带来的各种好处。

由于65纳米对于设计规则的要求更严苛,因此面临工艺技术很多挑战,例如更狭窄的源极和漏极区所产生的更大寄生阻抗、更短的栅极宽度以及过孔更小的接触面,这些都可能导致器件性能下降。为了解决这些问题,厂商开发出许多新型硅化物材料,它们可以减少接触面电阻、源极/漏极寄生阻抗、栅极阻抗,避免性能的下降。

DRP的未来

要为A-GPS、数字电视、蓝牙、无线网络、UMTS或其它无线传输接口开发数字射频解决方案并不容易,因为它们的需求不同,例如无线网络需要更大频宽,EDGE必须使用8-PSK调制机制、宽带CDMA对于5MHz频带的线性特性也有许多要求。而先进的DRP技术提供了一套满足这些挑战的方法。

更小的工艺尺寸有助于厂商为各种系统及标准开发出数字射频解决方案和单芯片解决方案,例如将DRP升级至65纳米工艺的计划已经在进行中。升级到更先进的工艺会带来很多不同的挑战,解决此问题的关键是在研发初期就将工艺技术的开发和芯片设计方法紧密结合在一起。

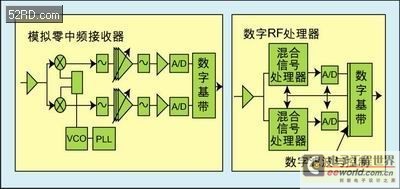

图3:数字收发器架构。

模拟射频不久的将来将从无线电行业消失,OEM厂商将开始生产更先进的手机,并透过手机所包含的多种无线电功能提供各式各样的应用。随着半导体厂商升级到更小的工艺尺寸,CMOS技术将成为射频领域的主流技术。SiGe BiCMOS仍将用于雷达或某些微波系统等设备,移动通讯基站也可能继续采用这种工艺技术。

我们预期射频电路将成为CMOS工艺技术的重要推动力,不断缩小的工艺技术会使得射频噪声处理、隔离和无源器件性能日益重要。逻辑电路的密度和速度也会是CMOS工艺发展的重要动力。

许多手机必须内建多种无线电路才能提供消费者所期盼的功能,DRP显然是它们未来应走的道路。软件无线电对于高效率使用无线电器件和减少器件数目固然重要,但电路板面积才是促使厂商整合射频功能的主要因素。此外,耗电量和成本考虑也会让模拟射频工艺更快地淡出舞台。

不同设计工程师可能选择不同的集成方式,例如短期内先将收发器与模拟或数字器件集成在一起,但就长期而言,无线信号的所有处理操作最终仍将以数字方式进行。接收信号会先通过天线、开关和滤波器,然后由采样电路对低噪声放大器的输出信号进行采样,此部份或许还会用到某些混频信号处理,但之后所有功能就全是数字技术的天下。