本文以OrCAD/PSpice 10.5为工具,对555定时器构成的三种典型电路进行仿真分析,得出了一些有价值的结论。

555定时器是一种将模拟功能与数字(逻辑)功能紧密结合在一起的中小规模单片集成电路。它功能多样,应用广泛,只要外部配上几个阻容元器件即可构成单稳态触发器、施密特触发器、多谐振荡器等电路,是脉冲波形产生与变换的重要元器件,广泛应用于信号的产生与变换、控制与检测、家用电器以及电子玩具等领域。

OrCAD/PSpice作为国际上著名的电子设计自动化软件之一,具有仿真速度快、精度高等优点,不仅可以用于电路分析和优化设计,与印制版设计软件配合使用,还可实现电子设计自动化,被公认是通用电路模拟程序中最优秀的软件之一。例如:基于该软件,Essakhi等人提出了一种微波整流天线的时域模型;Du等人提出了一种从三维时域场分析提取S参数的方法;Zhang等人仿真了E类功率放大器的特性,并进行了实验证实;Sakuta等人分析了低相位噪声振荡器的特性,并计算了有载Q值;Hayahara等人设计了△-∑A/D转换器,并对其信噪比进行了仿真;Brecl等人提出了一维、二维薄膜模型,并模拟了其接触电阻。这些表明,软件OrCAD/PSpice是现代电子电路设计的有利工具。

1 555定时器组成框图及工作原理

555定时器的图形符号及管脚图如图1所示,其中管脚1是公共端,管脚2为触发端,管脚3为输出端,管脚4为复位端,管脚5是控制电压输入端,管脚6为阈值端,管脚7是内部三极管的放电端,管脚8是电源端。

555定时器的内部电路方框图如图2所示,该集成电路由四部分组成:电阻分压器、电压比较器、基本RS触发器、输出缓冲器和放电三极管。

比较器的参考电压由三只5 kΩ的电阻器构成分压,它们分别使高电平比较器A1同相比较端和低电平比较器A2的反相输入端的参考电平为2Vcc/3和Vcc/3。A1和A2的输出端控制RS触发器状态和放电管开关状态。当输入信号输入并超过2Vcc/3时,触发器复位,555的输出端3脚输出低电平,同时放电,开关管导通;当输入信号自2脚输入并低于Vcc/3时,触发器置位,555的3脚输出高电平,同时充电,开关管截止。

MR是复位端,当其为0时,555输出低电平。平时该端开路或接Vcc。

CO是控制电压端(5脚),平时输出2Vcc/3作为比较器A1的参考电平,当5脚外接一个输入电压,即改变了比较器的参考电平,从而实现对输出的另一种控制,在不接外加电压时,通常接一个0.01μF的电容器到地,起滤波作用,以消除外来的干扰,以确保参考电平的稳定。

T为放电管,当T导通时,将给接于脚7的电容器提供低阻放电电路。

2 单稳态触发器仿真分析

单稳态触发器广泛用于脉冲整形、延时及定时电路中。单稳态触发器有一个稳态和一个暂稳态,在无外来触发脉冲作用时,电路保持稳态不变,而当有外来触发脉冲作用下,电路由稳态翻转到暂稳态,并输出一个脉宽和幅值恒定的矩形脉冲,输出的脉冲宽度TW等于暂稳态的持续时间,而暂稳态的持续时间取决于R2,C2,则:

![]()

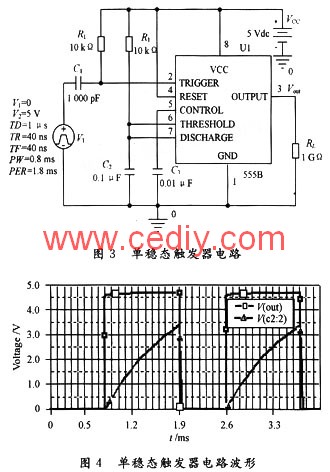

运行OrCAD/CaptureCIS,利用Schematics绘制的由555定时器构成的单稳态触发器电路见图3,输入信号Vi为脉冲电压源(VPULSE),设置其参数如下:

值得注意的是,输入信号VPULSE的重复周期必须大于输出的脉冲宽度TW,输入信号VPULSE的脉宽应小于TW,才能保证每一个正倒置脉冲起作用。

利用OrCAD/PSpice 10.5的瞬态分析功能进行仿真,瞬态分析(Time Domain Transient)是指在给定输入激励信号的作用下,计算电路输出端的瞬态响应,其实质就是计算时域响应。设置瞬态分析参数从零时刻开始记录数据,到4 ms结束,最大步长为0.1 ms。进行瞬态分析后,得到图4所示的输出电压波形图,其中类似于锯齿波的是电容C2两端的电压,而方波则是555的输出端Vout的电压波形。

由图4可见,电容C2存在自动充放电过程。当触发脉冲到达时,电源Vcc通过R2给电容C2充电,从0 V充电到约3.33 V之前,555定时器的输出始终保持高电平,而一旦电容充电到3.33 V,555的输出立即转换为低电平,随后电容C2开始从3.33 V迅速放电到0 V,此后又开始新的充放电过程。在555的输出端Vout可以获得周期性的矩形脉冲,而脉冲的宽度约为1.09 ms,与理论计算值1.1R2C2相近。并且输出脉冲的宽度与输入信号VPULSE的脉宽和幅度无关。

3 施密特触发器仿真分析

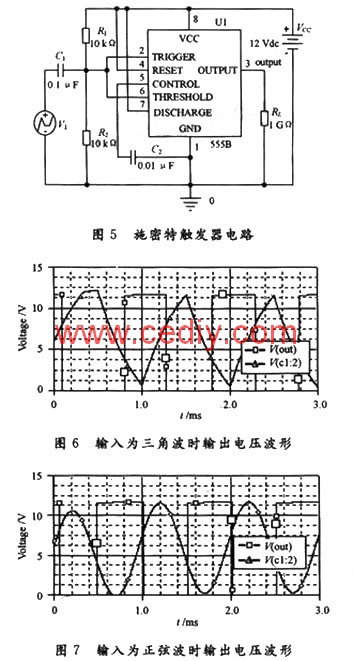

用555定时器构成的施密特触发器将阀值端和触发端接在一起作为输入端。运行OrCAD/CaptureCIS,利用Schematics绘制的555定时器构成的施密特触发器电路如图5所示。输入信号Vi为三角波电压源(VPWL),设置其参数为:

![]()

利用PSpice的瞬态分析功能进行仿真,设置瞬态分析参数从零时刻开始记录数据,到3 ms结束,最大步长为1μs,得到555的输出端Uout的电压波形与输入电压波形如图6所示。

由图6可见,该电路能将输入三角波转换成方波输出,当输入三角波电压升高,输出电平发生转换时所对应的门限电压约为8 V,而当输入三角波电压降低,输出电平发生转换时所对应的门限电压约为4 V,即上门限电压与下门限电压不同,输入与输出间具有迟滞特性。将输入信号换成正弦信号后,得到输入/输出电压的波形如图7所示,依然表现出迟滞特性,且上门限电压与下门限电压仍分别为8 V和4 V,而这正是施密特触发器电路的工作特性。仿真结果与理论计算结果的上门限电压(2/3 Vcc)和下门限电压(1/3 Vcc)相符。

4 多谐振荡器仿真分析

多谐振荡器是一种自激振荡器,接通电源后不需要外加触发信号便能自动产生矩形脉冲。运行OrCAD/Capture CIS,利用Schematics绘制的由555定时器构成的多谐振荡器电路如图8所示。

电路由一个555B芯片、两个电阻和两个电容组成,通过电阻给电容C1充电、放电的过程来产生振荡,从而输出矩形脉冲。启动PSpice瞬态分析功能,观察电容C1的端电压和555的输出端Vout的电压,得到图9所示的波形。由图9中发现555定时器构成的多谐振荡器的输出电压Vout始终保持高电平,并没有产生预期的振荡。

4.1 OrCAD/PSpice中555多谐振荡器不能起振的原因

分析可知,PSpice中555多谐振荡器不能起振的原因在于起振源。实际振荡电路之所以能自行起振是由于起振源的存在。实际振荡电路的起振源主要由两方面因素构成:一是由振荡电路晶体管内部的噪声和电路噪声(电阻热噪声等)引起;二是由电路接通电源瞬间的冲击电流引起。而直接利用PSpice对图6电路进行模拟仿真时,PSpice会将电路中的555定时器、电阻、电容、电源等元件和电路的接通过程都理想化,即电路中不能产生任何噪声和干扰。因此,没有起振源,自然就不能产生振荡。

4.2有效起振方法

经查阅相关文献[10],并经多次实验验证,发现有多种方法可以使电路起振,现介绍其中两种最简单的方法供大家参考:

(1)给电容加初始值(IC值),本例中只将C1和C2的IC设为0。电容上的初始电压,只是激发了振荡电路的振荡,没有改变电路起振后的输出波形,也没有影响对振荡电路起振特性的研究。

(2)在瞬态分析仿真设置(Simulstion Settings)中激活初始瞬态偏置点计算(Skip the Initial Transient Biaspoint Calculation)选项,直接使用各元件的起始条件来作瞬态分析。

两种方法都能顺利使555多谐振荡器发生起振,且持续地输出脉冲波形。

4.3仿真结果与理论计算值比较

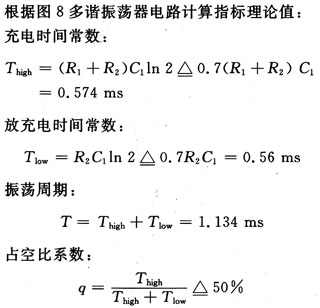

4.3.1计算指标理论值

4.3.2 仿真值

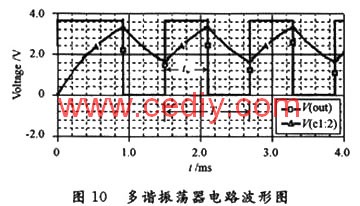

在OrCAD/PSpice中,采用前面提出的模拟振荡电路的起振方法得到555振荡电路输出端的矩形脉冲电压波形,如图10所示。

由图10可见,电源Vcc先通过R1,R2给C1充电,使电容C1从0 V充电到2Vcc/3,接着从2Vcc/3放电到Vcc/3,又再从Vcc/3充电到2Vcc/3,电容C1形成周期性的充放电过程,从而在555的输出端Vout形成周期性的矩形脉冲波,构成多谐振荡器。由图10所示,可得输出矩形脉冲特性参数:

仿真结果表明,输出脉冲周期、占空比系数的仿真值与理论值基本相符。同时分析可知,其值只与电阻、电容值有关,电容上的初始电压,只是激发了振荡电路的振荡,并不会改变电路起振后的输出波形,也不会影响对振荡电路起振特性的研究。

5 结 语

利用OrCAD/PSpice 10.5对555定时器构成的单稳态触发器、施密特触发器和多谐振荡器的特性进行了仿真分析。同时,针对仿真过程中多谐振荡器不起振的问题进行了讨论,提出了振荡电路的有效起振方法,仿真结果与理论计算值基本相符表明OrCAD/PSpice是电子线路设计人员必须掌握的基本工具之一。