0 引言

随着人们对无线通信需求和质量的要求越来越高,无线通信设备的研发也变得越来越复杂,系统测试在整个设备研发过程中所占的比重也越来越大。为了更加方便地对所设计的系统进行调试和测试,无线信道模拟器是进行无线通信系统硬件测试不可或缺的仪器之一。目前,关于无线信道的模型研究比较多,而基于理论模型的硬件实现并不是很广泛,同时成品十分昂贵,所以利用FPGA实现无线信道模拟器变得很有意义,节约了成本,而且也便于实现。FPGA是在PLD的基础上发展起来的高性能可编程逻辑器件,使用FPGA进行数字逻辑设计,开发过程的投资较少,研制和开发的时间较短,并且因为引脚的可分配性电路一般比较简单,修改和优化比较方便,并且在实际中易于使用。同时由于FPGA并行运算的特点,在大规模的数字运算中很有优势,延时很小。

1 频率选择性衰落信道模型

多径传播信道的信道脉冲响应模式是模拟一个离散的广义平稳非相关散射模型(WSSUS)。这样的频率选择性衰落信道应该满足两个假设条件:

(1)在时间t(可能是几个码元长度)内,衰落的统计特性是平稳的;

(2)电波到达角和传播时延是统计独立变量。

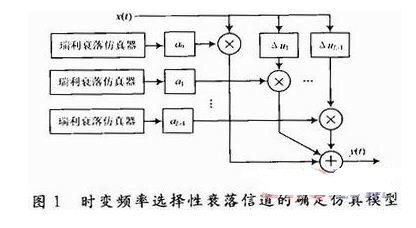

时变频率选择性衰落信道的确定仿真模型如图1所示。

Jakes在参考文献中介绍了一种单径衰落信道的仿真,且在此基础上提出了一种对频率选择性衰落信道的仿真方法。在原来第l径中的多普勒相移bnl的基础上,加上一个附加相移rnl,成为新的多普勒相移bnl+rnl,且保持其他参数不变。为了保证各个可分辨多径之间相互独立,所以必须选择合适的bnl和rnl,其中比较简单的一种方法是:

2 信道模拟器的FPGA设计

FPGA采用Xilinx公司的Virtex-2p,其中芯片工作时钟为100MHz。本文设置N0=8,fm=200 Hz,

为了计算方便,将所得的值扩大32倍,也就是左移5位之后四舍五入成整数值,存入寄存器调用。所以信道模拟器的实现过程主要为各个正弦波的FPGA实现,与对应的系数相乘叠加成单径衰落,输入信号经过l个路径时延之后叠加成为输出信号。

2.1 正弦波的FPGA实现

FPGA产生正弦波一般可以采用直接产生和Xilinx或者Altera利用自带DDS的IP核例化实现。FPGA直接产生是将三角函数值存入ROM中循环调用来产生正弦波,这样占用的逻辑资源比较少,缺点就是过程很麻烦而且不够灵活,模型需要8种频率的正弦波和余弦波,而且fm也可能根据需要而变化,每一次变化就需要在ROM中重新赋初值,十分麻烦。因此本文选择调用Xilinx自带DDS的IP核,通过逻辑资源换取效率。DDS的模块图如图2所示。

这样,通过控制DATA的值得到所需频率的正弦波。其中fclk为开发工作时钟,DATA为输入的频率控制字,B为DATA的位宽,fout为所得的频率。

2.2 时延模块的FPGA实现

输入通过时延后与各路径的衰落系数相乘,然后各个路径叠加成输出信号。本文中时延采用计数分频来实现,如延迟1μs,工作时钟为100MHz,所以计算100个时钟周期后,将输入的值存入寄存器1,再计算100个时钟周期后将输入值存入寄存器2,依次类推,本为路径l设置为5,所以最终有5个寄存器存放输入值。

2.3 测试模块的FPGA实现

最后需要将算得的数据上传到Matlab进行统计分析,所以还需要FPGA串口驱动,以及Matlab打开驱动读取FPGA算完的数据。根据异步串行通信的数据传送格式,每一帧数据由起始位、数据位、奇偶校验位和停止位组成,本文只选取了数据位,一共8位。通过串/并转换接收数据,算完后存入RAM,然后调用数据,通过并/串转换传输数据。

正弦波的输出有10位,其中l位是符号位,另外9位是小数位,而系数左移5位后化成整数,在所得的整数中也有5位小数位,所以最终数据一共有19位,其中5位整数位,14位小数位。因为串口是8位一帧数据,为了运算简便,选取了5位整数位,11位小数位,舍去最后3位小数,每个数分两次传输。因为最后的数据分为实部和虚部,所以每个复数需要4帧数据传输。Matlab接收数据重新组合,还原成FPGA的计算结果。

3 模拟器的性能测试与分析

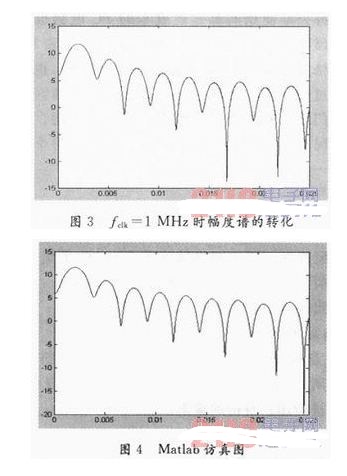

开发板的工作时钟为100 MHz,DDS IP核延迟2个时钟周期有输出值,乘法器延迟1个时钟周期有输出值,所以系统总共有3个时钟周期的延迟。串口传输数据比较慢,而且数据量太大容易出错,所以将工作时钟分别进行100倍分频上传衰落信道第一径的25 000个数据进行观察,工作时钟变成1 MHz,将所得的幅度谱转化成功率形式后如图3所示,fclk=1 MHz的Matlab仿真如图4所示。

图3和图4中横轴单位均为s,纵轴单位均为dB。通过比较图3和图4发现实际产生的结果与仿真结果大致相同,也因为系数的取整和最后上传数据的截断有少许误差,基本满足要求。

4 结语

本文采用Jakes改进模型,基于FPGA模拟了无线信道的传输特性,最终经过验证基本满足要求。为了简化实现过程,将系数取整以及传输数据进行截断,产生一些误差,在这方面可以采用浮点数表示系数得到更精确的值。