引 言

FPGA动态局部可重构技术是指允许可重构的器件或系统的一部分进行重新配置,配置过程中其余部分的工作不受影响。动态局部可重构缩短了重构的时间,减少了系统重构的开销,提高了系统的运行效率。局部动态可重构技术中通常将系统划分为固定模块和可重构模块。可重构模块与其他模块之间的通信(包括可重构模块和固定模块之间、可重构模块和可重构模块之间)都是由总线宏实现的。

动态可重构技术在FPGA中的实现是Xilinx公司首先提出的,并且提供了相应的开发工具和开发流程。他们从Virtex系列器件开始支持动态可重构技术,同时他们提供了现成的总线宏文件给动态可重构系统开发者使用,但是它们提供的总线宏设计与软件版本的兼容性很差。Xilinx提供的总线宏可能因为软件版本的问题会无法正常使用,所以用户需要借助正在使用的版本软件设计总线宏,以实现FPGA动态局部可重构设计。

在研究总线宏的结构基础上,采用FPGA Editor可视化的方法设计基于TBUF的总线宏,并通过FP-GA动态可重构实验验证了该方法的正确性。

1 基于TBUF的总线宏结构

在不同系列的Xilinx FPGA器件中,使用不同的总线宏来实现动态局部可重构技术。在Virtex,Virtex-E,Virtex-ⅡPro X,Spartan-Ⅱ,Spartan-ⅡE和Spartan-3系列器件中所使用的总线宏都是基于TBUF的,可重构模块的位置固定不变;在Virtex4,Virtex5更高性能的器件中,所使用的总线宏是基于Slice的,可重构模块的位置是可变的;而Virtex-Ⅱ,Virtex-ⅡPro所使用的总线宏既可以基于TBUF,也可以基于Slice。

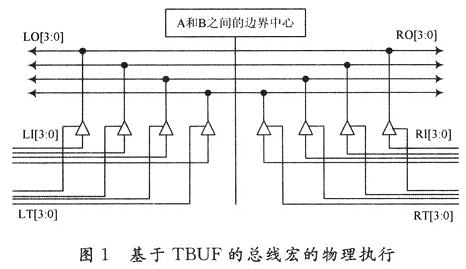

目前,使用最多的总线宏,其物理实现是使用6个三态缓冲器(TBUF),实现4位的双向通信。每个TBUF占用1位,每位使用1根TBUF长线,从FPGA的最左侧到最右侧,如图1所示。TBUF的T端是三态使能端口;I端是数据输入端口;O是数据输出端口。相应地,总线宏的T端(LT和RT)是方向控制端口,控制总线宏从左或从右输出;I端(LI和RI)是数据输入端口;O端(LO和RO)是数据输出端口。

总线宏的信息通信是双向的,既可以从左到右,也可以从右到左。但是对于一个设计来说,一旦信息通信方向确定以后就不能再改变。总线宏的位置精确地跨骑在模块A和模块B之间(A或B是可重构模块,或AB全是可重构模块),其中四栅三态缓冲器在模块A内,另外四栅在B内。对于Virtex-Ⅱ等系列器件,因内部结构不同,故两栅跨骑在模块A内,另外两栅跨骑在模块B内。

2 基于TBUF的总线宏设计

这里在深入研究Xilinx公司所提供的总线宏的基础上,结合宏的设计技术,完善了总线宏的设计。

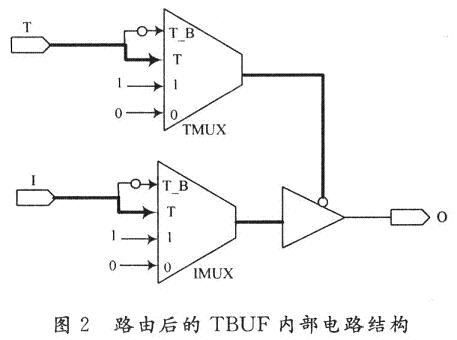

(1)TBUF的内部路由。图2给出内部路由后的TBUF电路结构图。TMUX的T端决定总线宏的控制端LT和RT高电平有效,而T_B端决定低电平有效。

无论控制信号是高电平有效,还是低电平有效,在使用总线宏进行通信时,LT和RT的值必须是相反的,或者是同时无效的。例如,当控制信号高有效时,即T端为1时,TBUF打开。如果总线宏是从左向右传递数据,则必须将LT设为1,RT为0,反之亦然;如果总线宏不需要传递数据,那么两个控制信号应同时为0,此时总线宏输出为高阻态。

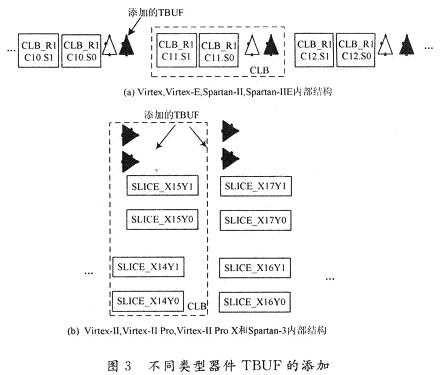

(2)TBUF添加的方法。Virtex,Virtex-E,Spar-tan-Ⅱ,Spartan-ⅡE的内部结构类似,与TBUF添加的方法是相同的。在相应的位置选择一个可编程逻辑块(Configurable Logic Block,CLB)中的一个TBUF作为总线宏的一个TBUF(1个CLB包含2个TBUF),依次选择同一行相连下一个CLB中的一个TBUF,直至选够8个TBUF为止;对于Spartan-3,Virtex-Ⅱ,Virtex-ⅡPro和Virtex-ⅡPro X系列器件;每一个CLB中的2个TBUF都作为总线宏的TBUF被选用,在同一行中依次选择相连的4个CLB中的8个TBUF作为总线宏的TBUF,如图3所示。

(3)TBUF外部端口的命名规则。根据图1的总线宏结构,对各个TBUF的外部端口T,I和O进行相应的命名,命名时要符合所使用版本软件的要求。例如,若对端口进行如下命名:LI<3>,LT<3>等,而端口在进行物理设计规则检查(Design Rule Check,DRC)时会出错,根据所提示的出错信息将命名改为:LI(3),LT(3)等,即能顺利通过DRC,完成端口的命名。

(4)总线宏输出端口的定义。总线宏输出端口的定义只能通过手工路由(Manual Route)方法,把相应TBUF的输出端口通过端口连线和TBUF长线连接起来。