目前,已经可以在1.2V 65nm CMOS技术的基础上实现8Vpp和脉冲宽度调制射频高压/大功率驱动器。在0.9到3.6GHz的工作频率范围内,该芯片在9V的工作电压下可向50Ω负载提供8.04Vpp的最大输出摆幅。这使得CMOS驱动器能够直接连接并驱动LDMOS和GaN等功率晶体管。该驱动器的最大导通电阻为4.6Ω。2.4GHz时所测量的占空比控制范围为30.7%到71.5%.通过使用新型薄氧化层漏极延伸MOS器件,该驱动器可实现可靠的高压操作,而这一新型器件通过CMOS技术实现时无需额外的费用。

技术背景

现代无线手持通信无线电(包括射频(RF)功率放大器(PA)在内)均是在深亚微米CMOS中得以实现。不过,在无线基础设施系统中,由于需要较大的输出功率等级,必须通过硅LDMOS或混合技术(如GaA和更先进的GaN)才能实现RF PA.对下一代可重新配置的基础设施系统而言,开关模式PA(SMPA)似乎能为多频带多模式发射器提供所需的灵活性和高性能。但是,为了将基站SMPA中使用的高功率晶体管与发射器的所有数字CMOS模块相连,需要能够生成高压(HV)摆幅的宽带RF CMOS驱动器。这样不仅能实现更优的高功率晶体管性能,而且还能将数字信号处理直接用于控制所需的SMPA输入脉冲波形,从而提高系统整体性能。

设计挑战

LDMOS或GaN SMPA的输入电容通常为几个皮法,必须由振幅高于5Vpp的脉冲信号驱动。因此,SMPA CMOS驱动器必须同时提供高压和瓦特级的射频功率。遗憾的是,深亚微米CMOS给高压和大功率放大器及驱动器的实现提出了诸多挑战,尤其是极低的最大工作电压(即可靠性问题引起的低击穿电压)和损耗较大的无源器件(例如用于阻抗变换)。

现有解决方案

用于实现高压电路的方法并不多。可以采用能够实现高压容限晶体管的技术解决方案(如多栅氧化层),但代价是生产流程较昂贵,必须向基线CMOS工艺添加额外的掩模和处理步骤,因此这种方案并不理想。此外,为可靠地增加高压耐受力,可以采用仅使用标准基线晶体管(使用薄/厚氧化层器件)的电路方案。在第二种方法中,器件堆叠或串联阴极是最常见的例子。但是,射频复杂性和性能具有很大的局限性,尤其是当串联阴极(或堆叠)器件的数量增加至2个或3个以上时。另一种实现高压电路的途径就是如本文所述的在基线CMOS技术中使用漏极延伸场效应管(EDMOS)来实现。

新的解决方案

漏极延伸器件基于智能布线技术,这得益于在ACTIVE(硅)、STI(氧化层)及GATE (多晶硅)区域中可实现十分精细的尺寸,并能在没有附加费用的条件下,利用基线深亚微米CMOS技术实现PMOS和NMOS两种高压容限晶体管。尽管与采用该工艺的标准晶体管相比,这些EDMOS设备的RF性能实际上较低,但由于消除了与其他HV等效电路相关的重要损耗机制(如串联阴极),它们仍能在整个高压电路中实现较高整体性能。

因此,本文所述的高压CMOS驱动器拓扑结构采用EDMOS器件来避免器件堆叠。RF CMOS驱动器采用薄氧化层EDMOS器件通过65nm低待机功耗基线CMOS工艺制造,且无需额外的掩模步骤或工序。对PMOS和NMOS而言,这些器件上测量到的fT分别超过30GHz和50GHz,它们的击穿电压限度为12V.高速CMOS驱动器前所未有地实现了高达3.6GHz的8Vpp输出摆幅,因而能为像GaN这样的基于宽带隙的SMPA提供驱动。

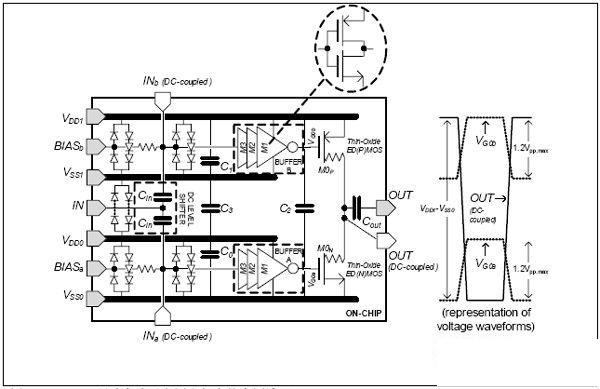

图1为本文所述驱动器的结构示意图。输出级包括一个基于EDMOS的逆变器。EDMOS器件可由低压高速标准晶体管直接驱动,从而简化了输出级与其它数字和模拟CMOS电路在单颗芯片上的集成。每个EDMOS晶体管均由通过3个CMOS逆变器级实现的锥形缓冲器(图1中的缓冲器A和B)提供驱动。两个缓冲器具有不同的直流等级,以确保每个CMOS逆变器都能在1.2V的电压下(受技术所限,即VDD1-VSS1=VDD0-VSS0=1.2V)稳定运行。为了使用不同的电源电压并允许相同的交流操作,两个缓冲器的构造完全相同,并内置于单独的Deep N-Well(DNW)层中。驱动器的输出摆幅由VDD1-VSS0决定,可随意选择不超过EDMOS器件最大击穿电压的任意值,而内部驱动器的运行保持不变。直流电平位移电路可分离每个缓冲器的输入信号。

图1:RF CMOS驱动电路示意图和相应的电压波形

CMOS驱动器的另一个功能就是对输出方波的脉冲宽度控制,该功能由脉宽调制(PWM)通过可变栅偏压技术实现。PWM控制有助于实现微调和调谐功能,从而提升高级SMPA器件的性能。缓冲器A和B的第一个逆变器(M3)的偏置电平可参照该逆变器本身的开关阈值对RF正弦输入信号进行上移/下移。偏置电压的改变将使逆变器M3的输出脉冲宽度发生变化。然后,PWM信号将通过另外两个逆变器M2和M1进行传输,并在RF驱动器的输出级(EDMOS)合并。

为确保输出级之前的两个RF路径的布局对称,所有逆变器(从M0到M3)都采用了统一的PMOS-to-NMOS晶体管尺寸比。所有CMOS级中每个加宽晶体管(M0级的总宽度可达4,032μm)的布局被分割成若干个单位晶体管布局参数化单元(P-cell),并通过优化实现最高频率。每个P-cell都包含一个版图不对称的多指晶体管(具有最小栅长)、护圈和所有与顶层内部金属的互连。每个晶体管的布局均可充分扩展。

此外,该驱动器还包含大尺寸的片上交流耦合和交流退耦平行板交指型金属边电容器。电容器Cin与两个DC输入偏压线路(BIASa,b)一起实现直流电平位移。使用片上电容器Cout可实现DC耦合或AC耦合两种方式的输出。AC耦合可驱动需要负栅偏压的功率晶体管(如GaN)。将四条宽粗的电源线(VSS0,1和VDD0,1)布线于位于两块更厚的金属顶部上的芯片内。采用电容器C0、C1、C2和C3对内部电源线进行退耦。此外还增加了专用的ESD保护电路以保护CMOS芯片。

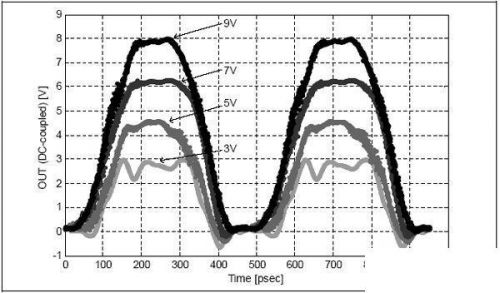

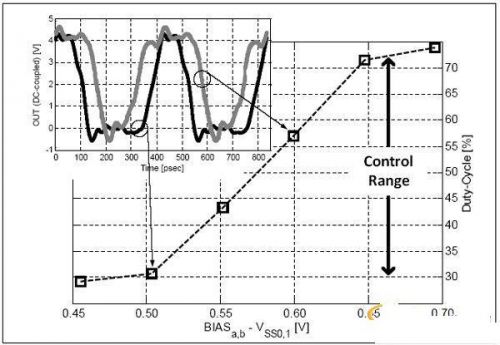

CMOS驱动器的总体芯片面积为1.99mm2,而工作面积(EDMOS和缓冲器)仅为0.16mm2.将原型裸片安装于PCB上以便于测试,并在50Ω的负载环境下进行测量。使用高速数字采样示波器可捕捉时域信号。图2显示了在3V、5V、7V和9V的供电电压下,且输入正弦波为2.1GHz时,驱动器DC耦合输出的时域波形。在50Ω负载和9V电源下所测量的最大摆幅为8.04Vpp.测量到的驱动器导通电阻低至4.6Ω。图3显示了测量到的脉冲宽度(以占空比表示)控制范围,以DC偏置电平(即BIASa,b-VSS0,1)的函数表示。该图还显示了不同占空比条件下的两种时域波形。在2.4GHz频率和5V电源下可观察到占空比控制范围为30.7%至71.5%.在高达3.6GHz的频率下,RF驱动器将其脉冲波形保持为8Vpp.在2.4GHz下进行的另一项测量表明,在5V和9V电源下连续工作24小时后,性能并未发生下降。

图2:2.1GHz时,多种电压下监测到的时域波形(VDD1- VSS0= 3V, 5V, 7V, 9V)

图3:2.4GHz时测量到的占空比

与之前最先进的CMOS器件相比,上述驱动器实现了更大的输出电压摆幅和更高的工作频率。此外,该CMOS驱动器具有与SiGe-BiCMOS等效电路相近的性能。相比之前所有HV驱动器,本文介绍的芯片具有带RF控制功能的附加脉冲以提升SMPA系统性能。

本文小结

本文主要描述了采用1.2V基线65nm CMOS技术实现8.04Vpp和3.6GHz工作频率的首款宽带PWM控制RF SMPA驱动器。该CMOS驱动器连接了数字CMOS电路与高功率晶体管,可充当面向无线基础设施系统的下一代可重新配置多频多模发射器的主要构建模块。