文献标识码: A

DOI:10.16157/j.issn.0258-7998.2016.08.009

中文引用格式: 沈志远,吴智,陈国胜,等. 整合3DEM的Virtuoso在片上电感仿真中的应用[J].电子技术应用,2016,42(8):44-47.

英文引用格式: Shen Zhiyuan,Wu Zhi,Chen Guosheng,et al. Using Cadence Virtuoso 3DEM for on-chip inductor extraction[J].Application of Electronic Technique,2016,42(8):44-47.

0 引言

片上电感是射频芯片中非常重要的器件,很多工艺厂商都在工艺库中提供片上电感的模型。但随着电路工作频率越来越高,许多工艺库中提供的电感模型已经不能满足设计需求,需要客户根据需求自定义片上电感的尺寸参数。在这种情况下,如何获取精确的电感模型是项目成败的一个非常关键的因素。

目前主流的方法是将片上电感的版图导入电磁仿真软件进行仿真。但是电磁仿真软件对片上器件的支持不是很好,导入数据以及建立仿真环境的过程非常繁琐,对于电磁仿真经验比较少的研发工程师来说是一个不小的挑战。而Cadence基于PowerSI工具的基础上研发的嵌入Virtuoso的3DEM电磁仿真软件可以很好的解决这个问题,其简便的操作方法,简单的环境设置以及快速而精确的仿真结果有助于快速掌握电磁仿真流程,获取精确的片上电感仿真模型。

1 电感建模及主流仿真软件的使用

1.1 片上电感建模介绍

虽然单端口电感的磁场眼中央空洞呈对称分布[1],其电场及电阻的分布却不对称,其共模噪声抑制能力较差。因此在射频集成电路中,更多的是采用差分电感。

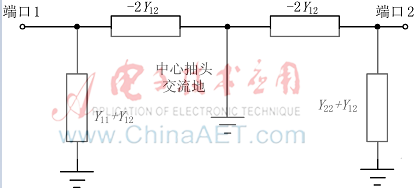

中心抽头差分电感的等效模型如图1所示[2]。

图1 中心抽头差分电感模型

差分阻抗以及等效的电感、品质因数计算公式如下[2]:

1.2 主流仿真软件的使用

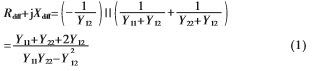

为了仿真片上电感的模型,首先需要提取电感的版图文件,另外还需要一个包含电感金属堆叠信息文件,同版图数据一起导入电磁仿真软件。仿真前,首先需要设置包含仿真器件几何形状的空气腔,以及器件下方的衬底层。然后设置衬底层和金属层的电学参数。若要仿真器件以及与之相连的金属线整体的模型,则随着走线及过孔的形状的不同,仿真难度也会相应的变化,过于复杂的几何尺寸将使得仿真数据量和仿真时间大大增加。主流电磁仿真软件的流程如图2所示。

图2 主流电磁软件优化仿真模型流程

从图中可以看到,版图文件导入后,还需要处理金属层和其他介质层之间的层叠关系。如果存在交叠部分,还需要手动处理。另外,有的片上器件存在一些虚拟金属,这些对模型的结果影响很小,手动去除可以减小运算量,但是这增加了设置模型的工作量。

最后需要将仿真结果导出为S参数,并引入电路的原理图或者电路的网表中仿真,如果需要重复迭代优化,这个过程将会大大降低优化的速度。

2 3DEM仿真及电感实例介绍

2.1 3DEM简介

3DEM是Cadence公司基于PCB板级电磁电磁仿真软件[3-5]研发的,嵌入到Virtuoso中的新一代电磁仿真软件。由于Virtuoso的普及度非常高,在研发环境内直接进行电磁仿真就便利很多。并且3DEM只需要Cadence提供的相应的库文件(通常是ict文件)就可以自动的导入器件所用到的金属层和介质层的相关电参数,同时调整各层的材料属性和厚度也很方便。另外,3DEM可以根据不同工艺角的工艺文件,建立不同的仿真模型,这大大加快了仿真的遍历性,对同一器件可以同时提取不同工艺角的S参数用于项目的仿真。

基础算法上,3DEM模块针对IC、封装和PCB结构,采用全三维有限元[6](3DFEM)算法,能准确分析复杂三维结构的性能参数。其全波求解器支持零阶和一阶的网格,网格采用自适应的生成方式能实现结果的快速收敛并提高仿真精度。电磁场方程的求解采用了先进的模型降阶方法,使仿真速度能提高一个数量级。由于采用了一种先进的低频段算法,大大提高了3DEM在低频段的精度和稳定性。

扫频方式上,3DEM采用的是KMOR扫频法,在频域里相当于所有本征模的线性组合。与其他基于曲线拟合的扫频方式不同,KMOR基于本征模的方法不会产生错误的谐振,而普通的逐点扫频法速度极慢,因此KMOR扫频法是一种又准又快的扫频方法。

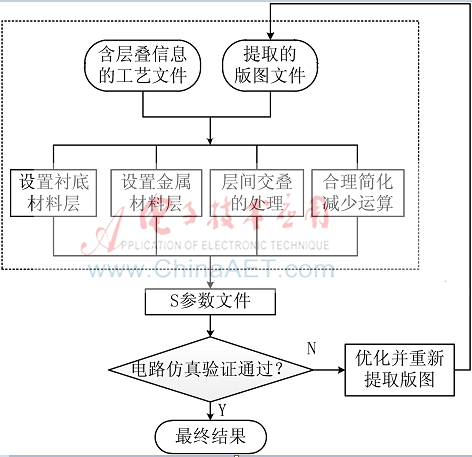

3DEM可以自动识别并生成器件的接口信息,这不仅大大节省了建立仿真模型的时间,并且在最终输出的结果中,求解器会自动减去由接口引入的寄生参数,从而保证了结果的精确性。并且由于3DEM集成在Virtuoso环境中,仿真输出的S参数可以直接反标回电路原理图,自动生成一个独立命名的原理图用于仿真,工程师只需复用之前的验证平台直接验证参数的正确性,使用起来非常方便。图3显示了电磁仿真验证流程。

图3 3DEM电磁仿真流程

为了验证仿真的性能,下面选择工艺库中的一个螺旋电感进行仿真验证。

2.2 仿真环境的启动及参数设置

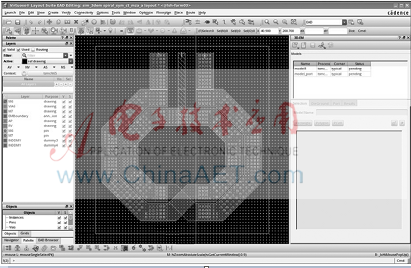

3DEM集成在Virtuoso中,直接选择电感的版图并右键选择打开的方式,选择“Layout EAD”选项即可,并在打开的版图界面逐次选择“Window→Assistants→3DEM”打开辅助界面。如图4所示。

图4 3DE完整界面

仿真时需要设置的工艺相关的参数均集成在辅助界面,并且操作非常简便。首先介绍衬底材料的设置,在辅助界面,选择“Process”按钮,在弹出的窗口“Substrate Parameters”设置衬底参数,不需要单独建立几何腔体即可直接设置。

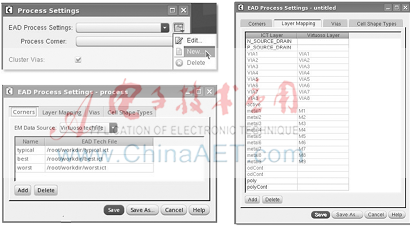

接下来就需要设置金属材料和介质层的相关参数,在打开的工艺设置界面,添加或者编辑工艺信息。在弹出的窗口中的“Corner”选项卡,可以添加不同工艺角的工艺文件;在“Layer Mapping”选项卡设置需要映射到3DEM中的版图中的层次;“Vias”选项卡则设置过孔简化的参数。设置如图5所示。

图5 设置工艺参数

工艺参数设置完毕后,就可以开始设置仿真的端口了。3DEM的端口设置分两种:如果选择仿真的是PCELL元件,这种元件自带的端口信息可以被捕捉,就不需要单独设置端口;如果选择的是普通的版图元件,则通过“Selection”选项卡,用“EMBoundary”层画一个区域,与这个区域切边的金属,可以通过“Port”选项卡的“Port Generation”按钮自动识别为端口。两种端口设置情况如图6所示。

图6 端口设置

地平面的设置也很简单,在“DieGround”选项卡中选择相应的设置选项,输入参数即可。

仿真参数的设置,在3DEM设置中选择“Simulation”选项,在弹出的窗口中分别设置好扫频方式、仿真器选项以及辐射边界条件。

2.3 仿真及反标输出

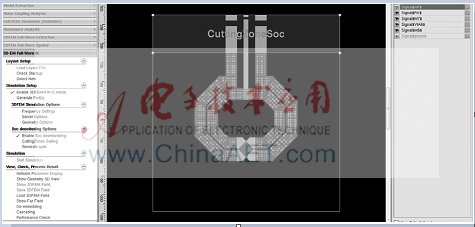

参数设置好后,选择“Start Simulation”,Virtuoso将自动打开3DEM仿真界面开始仿真,如图7所示。

图7 仿真界面

其中“CuttingZoneSoc”是将原始的走线自动延长到仿真腔的边缘,仿真结束工具会自动去嵌入(De-Embed)这部分引入的寄生参数[5],因此由仿真设置引入的结果误差降到最低。去嵌入的仿真原理如下:

(1)先求解电感(包括延长部分)的S参数;

(2)根据短路-开路法求出延长区“CuttingZoneSoc”的走线寄生S参数;

(3)从总的结果中减去这部分寄生,得到精确的电感器件的S参数结果。

普通片上电感大约需要仿真30-40 min,而同样一个例子,即使经过一些简化处理,采用主流的一款电磁仿真软件,仿真时间则需要10小时以上,所以3DEM的速度优势是十分明显的。仿真结果界面如图8所示。

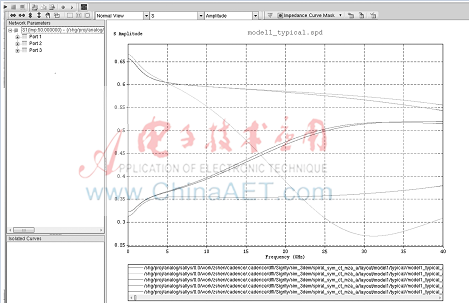

图8 仿真结果

仿真结束后,可以将结果直接反标回电路,并且自动产生一个新的原理图,方便仿真调用区分,这个功能使得优化仿真的流程更加简便。

2.4 结果对比

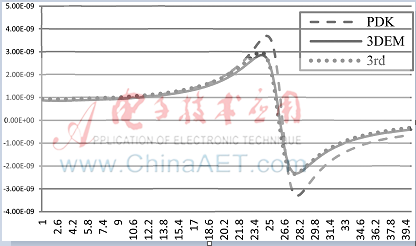

本次仿真结果同工艺库中的电感的频率特性进行了比较,同时同样的例子通过第三方的电磁仿真软件也进行了仿真。结果比较如图9所示。

图9 仿真结果比较

通过结果比较可知,仿真结果跟现在行业常用的电磁仿真软件相差无几,但是仿真速度和软件的易用性优势非常明显。因此是射频研发工程师提高研发和优化速度的非常实用的工具。

3 3DEM在实际项目中的应用

上面几部分介绍了3DEM应用于片上电感的电磁仿真方法,3DEM的优势不仅在仿真单个电感,而是在具体电路设计中,直接选取电路版图的一部分进行电磁仿真。这样不仅可以直接对感兴趣的任意版图部分进行电磁仿真,并且可以避免单独提取版图这一难题。仿真结果更接近实际工作情况,电路性能的仿真结果更具可信度。下面就以HDMI 2.1项目研发中的LC-VCO模块的电磁仿真为例,介绍3DEM的应用。

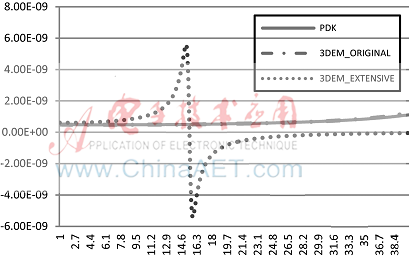

功能的验证由两部分组成:首先只选取电感的版图,3DEM仿真并与工艺库中的参数进行比较;然后选取电感加连线延伸部分,仿真带寄生参数的电感参数,同时与原电感参数进行比较。图10给出了这两种仿真的版图选取区域的不同,图11给出了仿真结果。

图10 仿真区域选择

图11 3DEM与工艺库及连线寄生结果比较

通过以上仿真比较发现,电感之外的连线引入了相对比较大的寄生参数,这在射频设计中是非常重要的。因为LC-VCO的频率调节范围本来就很小,如果电感参数的估计偏差较大,很可能最后震荡频率会跳出频率调节范围,从而无法到目标频率。3DEM精确的寄生参数仿真结果,可以让研发人员准确的调整VCO的设计,从而使得频率调节范围可以很好的覆盖目标频率。仿真的结果已经得到测试芯片的验证,从而验证3DEM仿真的准确性。

4 结论

通过单独电感和具体VCO的实例,熟悉集成与Virtuoso的3DEM的电磁仿真软件的性能。通过对仿真结果的对比发现,3DEM具有仿真方法简便,仿真速度快并且结果精度与流行的电磁仿真软件相差无几。因此3DEM是射频器件的建模仿真非常好的选择。

参考文献

[1] 刘小茶.片上螺旋电感的电磁特性分析[D].上海:上海交通大学,2006.

[2] 卢磊,周锋,唐长文,等.中心抽头差分电感的等效模型和参数提取[J].半导体学报,2006,27(12):2150-2154.

[3] RAMIREZ A Z.Power distribution network analysis using semi irregular plane shape approach and via modeling[C].2015 16th Latin-American Test Symposium(LATS),2015:1-6.

[4] SAVIC J,ARIA P,PRIEST J,et al.Electrical performance assessment of advanced substrate technologies for high speed networking applications[C].2009 59th Electronic Components and Technology Conference,2009:1193-1199.

[5] YU T,CHEN J,SHIH C.Efficient methodology for modeling structure of high-speed long transmission lines[C].Electrical Performance of Electronic Packaging and Systems(EPEPS),2015 IEEE 24th,2015:113-116.

[6] SINGH S,KUKAL T.Timing skew enabler induced by fiber weave effect in high speed HDMI channel by angle routing technique in 3DFEM[C].Electrical Performance of Electronic Packaging and Systems(EPEPS),2015 IEEE 24th,2015:163-166.