周春良1,2,樊文杰1,2,王连成1,2,冯曦1,2,周芝梅1,2,唐晓柯1,2

(1. 北京智芯微电子科技有限公司 国家电网公司重点实验室 电力芯片设计分析实验室,北京 100192;2. 北京智芯微电子科技有限公司 北京市电力高可靠性集成电路设计工程技术研究中心,北京 100192)

摘要:在介绍实时操作系统Nucleus Plus和LTE230芯片及硬件平台的基础上,详细论述了Nucleus Plus移植过程中的系统启动、系统初始化、内存管理、中断管理、高级中断和任务管理以及操作系统的测试,指出了Nucleus Plus在LTE230芯片上移植的重点和难点。目前移植的操作系统已成功应用于LTE230通信模块中,操作系统的实时性、任务及中断管理完全满足系统需求。

关键词:Nucleus Plus操作系统;CEVA-X1643 DSP;移植;中断;任务

中图分类号:TP316.2文献标识码:ADOI: 10.19358/j.issn.1674-7720.2017.01.007

引用格式:周春良,樊文杰,王连成,等. 实时操作系统Nucleus Plus在LTE230芯片上的移植[J].微型机与应用,2017,36(1):22-24,31.

0引言

LTE230芯片是针对230M电力无线通信专网推出的终端基带芯片,芯片采用软件无线电技术,除物理层时域部分用中频电路实现,物理层频域和比特符号级处理、协议层媒体访问和无线资源控制、网络层协议以及芯片内外大量设备管理都是用CEAVX1643 DSP(简称X1643)软件来实现[1],因此软件非常复杂,涉及到很多实时性要求较高的中断和任务,传统的基于中断触发的软件架构已不能满足芯片基带处理的需要,须将实时操作系统及其多任务调度机制引入进来,通过多任务管理来完成系统的多种功能及功能的扩展与更新,达到简化DSP软件设计、提高开发效率的目的。

目前主流的商用实时操作系统都不支持X1643,同时使用CEVA DSP的芯片厂商所需支持操作系统皆是自行购买后进行移植,故可借鉴的经验很少。经详细评估,考虑到实时性、内核大小、用户数等诸多因素,最终选定Mentor Graphics的Nucleus Plus操作系统(简称Nucleus)作为移植对象。Nucleus是为实时嵌入式应用而设计的一款基于优先级的抢先式多任务操作系统,支持ARM等主流处理器,最新版本接近99%的代码是用ANSI C编写的,非常便于移植。在典型的目标环境中,核心代码不超过20 KB。Nucleus采用软件组件的方法,易于替换和复用,常用组件包括任务控制、内存管理、中断管理及定时器管理等[2]。

1芯片及其硬件平台

芯片是一个以DSP为核心的SoC,整体结构如图1所示,片内集成了高性能的X1643处理器、大容量的eDRAM存储器、具有载波聚合功能的中频模块以及通用的UART、SPI、I2C、Timer、WDT、GPIO、PWM等外设。

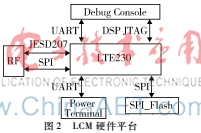

基于芯片的通信模块采用基带芯片+射频芯片的方案,如图2所示。基带芯片与射频芯片之间的控制接口为SPI,数据接口为JESD207;与电力终端之间的控制与数据接口皆为串口。

2操作系统移植

Nucleus暂不支持X1643,在芯片上进行移植涉及到系统启动、系统初始化、内存管理、中断管理和任务管理等工作。X1643采用单指令多数据SIMD和超长指令字VLIW相结合的架构,其核心寄存器约有100多个,包括累加寄存器ACF、寻址寄存器ARF、程序寄存器SRF、模式和状态寄存器MSR、断定寄存器PR以及存储子系统寄存器MSSR几大类[3],相比于ARM处理器,寄存器的分类及功能有较大的不同,移植时有些寄存器的使用须特别注意。

2.1系统启动

芯片通过BootStrap Pin来控制启动方式。可经BootROM引导,通过串口或SPI Flash把操作系统和应用程序加载到TCM和eDRAM中执行;因X1643支持从指定的地址启动,也可通过SPI控制器的memory mode直接从SPI Flash启动程序;在早期的调试过程中,可使用JTAG仿真器把程序直接下载到TCM和eDRAM后开始执行。与ARM等处理器稍有不同的是,Program TCM不能通过X1643内部数据总线和芯片系统总线访问,只能通过JTAG或使用Program DMA进行程序加载。

2.2系统初始化

系统正常启动后,PC指针将跳到零地址,即Program TCM中,开始系统的初始化。首先进行板级初始化,主要过程如图3所示。

BootROM中会对时钟复位及存储器控制等进行基本的初始化,在板级初始化时主要进行操作系统本身及X1643核的初始化操作。操作系统的启动栈放在系统的内存池中,在切换到系统栈后,启动栈占用的空间将会被回收到内存池中。X1643提供的“饱和”、“乘移位”、“模”等操作是针对特定的数字信号运算的,操作系统不会使用,在初始化中须关掉,以防误触发引起程序行为异常,汇编代码如下:

;Clear all saturation mechanisms

mov moda, a0

or #0x1F, a0

;Disable multiplier post shift mechanisms

mov #0xFFFF1FFF, a1

and a1, a0

mov a0, moda

;Disable the modulo mechanisms

mov mod0, r0

ands r0, #0xffffff00, r0

mov r0, mod0

X1643采用编译器驱动的架构,指令流水线的数据、资源及控制相关是通过编译器来解决的,但编译器对汇编代码不做处理,故在编写初始化及其他汇编代码时,需手工加nop指令来隔离相关操作,这一点须特别注意。

板级初始化后的操作系统软件组件初始化和应用程序初始化都是用C代码实现的,其过程与在ARM处理器上相似,在此不再详述。

2.3内存管理

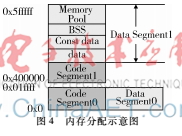

Nucleus提供分区内存管理和动态内存管理两种方式,前者具有非常好的确定性,但不够灵活;后者非常灵活,但内存分配与回收的时延不够确定。考虑到芯片基带处理的内存需求很明确,故选用分区内存管理的方式。具体的内存分配如图4所示。

图4中,Code Segment0使用Program TCM, Data Segment0使用Data TCM, X1643是哈佛结构,两个TCM使用相同的地址空间。eDRAM起始地址为0x400000,总容量2 MB,前一部分分配给代码段,后一部分分配给数据段。内存池起始地址在BSS段之后,结束地址为eDRAM末尾。Nucleus要求BSS段是链接时的最后的数据段,BSS后的空间保留给内存池,不能被占用,但链接器在链接基带处理中调用CEVA库函数时看不到这个区域,须加链接约束,确保其位于BSS之前。

2.4中断管理

X1643有5个中断源,其中INT0、INT1和INT2分别来自中频、外设(所有外设中断经中断控制器合成一个中断源)和OS Tick Timer,INT3和INT4保留给X1643内部Program和Data DMA,仅在启动时使用,可采用查询方式。在操作系统中只对INT0、INT1和INT2进行处理,且这三个中断使用统一的通用中断处理程序,通过ID来区分。在操作系统中,可调用NU_Register_LISR把每个低级中断服务程序LISR注册到中断函数指针数组中。LISR耗时极短,仅能调用极少的系统服务,复杂的数据处理及系统调用可激活高级中断服务程序HISR来完成。

当中断发生时,处理流程如下:

(1)进入中断入口,关中断(硬件) ;

(2)设置中断ID到a0,并保存a0原先的值到栈中,进入通用中断处理程序;

(3)保存X1643寄存器到栈中(push);

(4)保存栈指针,切换栈指针到系统栈;

(5)跳转到操作系统中断服务入口,进行中断处理(LISR);

(6)恢复栈指针;

(7)如中断服务程序要求上下文切换,进行上下文切换(context switch,HISR);

(8)从栈中恢复X1643寄存器(pop);

(9)恢复中断ID占用的a0寄存器;

(10)开中断,中断返回。

编译器把X1643内部寄存器分为两类:CallUsed寄存器和CallSaved寄存器[4]。为提高中断处理效率、降低处理延迟,在步骤(3)、(8)中仅保存和恢复CallUsed寄存器。CallUsed寄存器主要有:

ACF(40bit register):a0~a7,a16~a23

ARF:r0~r3,g1~g3,s0~s1,modu0,modu1

SRF :lcstep0,lcstep1, lci0~lci3

MSR和PR: mod0,moda

2.5高级中断和任务管理

Nucleus高级中断可认为是一种优先级较高的任务,两者都有各自的堆栈空间,在创建时进行堆栈初始化,在调用之前要保存上下文(堆栈),在调用之后要恢复上下文(堆栈)。在移植操作系统时,重点关注的是高级中断和任务与X1643体系结构及编译器密切相关的堆栈结构及初始化、堆栈保存及恢复的实现过程。

Nucleus堆栈有两种:Solicited Stack和Unsolicited Stack。堆栈初始值仅在第1次调用时会用到,此时真正需要通过堆栈得到的值是高级中断和任务运行的地址及传递的参数,大多数寄存器初值只要不影响运行,可不初始化。

Solicited Stack用于高级中断,是一种minmum stack。在进入LISR时,已保存了CallUsed寄存器,Solicited Stack只须保存CallSaved寄存器。Solicited Stack数据结构是在C语言中声明的。需要注意的是,X1643 ACF a8~a15是40 bit的寄存器,为使push/pop处理方便,高8位按“UINT32 a8e”方式声明。此外,针对数字信号处理中大量运算都集中在循环执行少量核心代码上,为省去循环计数测试指令,X1643设置了最大4级嵌套的零消耗循环控制专门硬件(BlockRepeat Mechanism Register[3])来提高代码执行效率。用汇编语言编写高性能循环代码或用C语言编写,且在加高级优化选项编译时会用到循环控制硬件寄存器,为确保程序运行正常,须初始化这4组寄存器为0。同样在进行上下文切换时,须对这4组寄存器进行保存和恢复,这4组寄存器使用相同的名字,其保存汇编代码如下:

bkst ;第1组

push{dw}bknest1 || push{dw} bknest0

;第2/3组与第1组操作类似,此处省略

bkst ;第4组

push{dw} bknest1 ||push{dw} bknest0

Unsolicited Stack用于任务,须保存当前所有寄存器,其初始化、保存及恢复操作与Solicited Stack类似,但因其包含了用于“饱和”、“模”等操作的寄存器,故须对MSR的mod0和moda进行初始化。

3操作系统测试

操作系统移植后的测试分两步:首先应用Kernel Demo[2]进行基本功能测试;然后应用LTE230附着过程进行典型场景测试。

Kernel Demo创建了7个任务、1个消息队列、1个信号量和1个事件组。Task_0是一个定时器任务,每隔1 s产生一个事件;Task_1是一个生产者任务,向队列中发送消息;Task_2是一个消费者任务,从队列中获取消息;Task_3和Task_4使用相同的任务入口函数来竞争一个信号量;Task_5等待Task_0产生的事件,并对事件进行计数;Task_6检测串口按键输入,输出Task_0到Task_5的状态信息。

LTE230附着是终端开机后与网络建立连接的必要过程,包括小区搜索、随机接入、MIB/SIB接收等步骤。在附着过程中,除OS Tick中断外,还须处理中频模块收发相关的4个中断、1个物理层定时中断、发送和接收2个任务以及中断与任务之间的信号量通信。

Kernel Demo和LTE230附着过程正常工作,表明操作系统的多任务调度、中断处理及通信机制功能正常,在此基础上,可进行完整的芯片驱动、LTE协议栈、TCP协议栈、业务通道处理等整个软件系统的移植和测试。

4结论

本文详细介绍了Nucleus在LTE230芯片上的移植过程和注意事项,目前移植的操作系统已在试点项目的通信

模块中稳定运行了一年多,充分表明操作系统移植是很成功的。因操作系统移植是基于LTE230芯片的X1643进行的,故在移植过程中需对X1643内核寄存器有深刻的理解,用汇编语言完成板级初始化及任务调度和中断处理时对内核寄存器的保存和恢复等操作,这是针对一款新的处理器进行操作系统移植的重点和难点。本文论述的方法对其他嵌入式实时操作系统在CEVA系列DSP核上进行移植也有重要的参考意义。

参考文献

[1] 周春良,张峰,程伦,等. LTE230无线通信基带芯片的设计与应用[J].电子技术应用,2015,41(12):4850

[2]Mentor Graphics,Inc.. Nucleus Kernel Guide[Z].2013.

[3] CEVA,INC.. CEVAX1643 Architecture Specification[Z].2012.

[4]CEAV,INC.. SmartNcode SDT Users Guides V9.2[Z].2011.