Intel换了CEO能做苹果M1那样的芯片吗?PC处理器大小核反击战

2021-01-14

来源: 电子工程专辑

2020年对Intel而言实在不是友好的一年。虽然Intel的财报仍未表现出大问题,但Intel在很多领域的前景是不乐观的。在《2021年十大热点应用趋势展望》中,我们提到了在PC处理器领域,“AMD将吃下‘半壁江山’”,这源自AMD Zen架构处理器的强势;苹果M1的问世则为这个趋势火上浇了一勺油;与此同时,数据中心市场显现出的市场趋势是,CPU逐渐被边缘化,英伟达DPU在这方面显现出的野心是相当显著的。

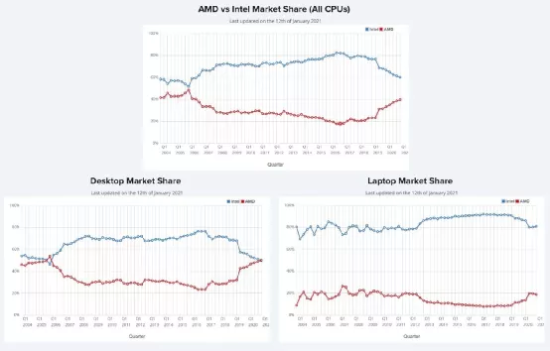

PassMark的CPU市场份额数据虽然有幸存者偏差,但在截至今年1月12日的数据更新中,AMD的桌面CPU市场份额已经达成自2006年以来,首次对Intel的超越——当然两者的笔记本市场份额仍然相差较大,毕竟OEM客户是Intel的基本盘。在整个x86 CPU市场,AMD的份额总体刚刚突破了40%(PassMark)。

来源:PassMark,注意这组数据带有明显的幸存者偏差,仅供参考[1]

Intel十多年来,在PC处理器技术上的碾压级优势,似乎在这短短2年内便彻底丧失——不仅是Skylake这种年迈架构表现的弊端,而且在10nm工艺迟迟无法大规模量产的情况下,7nm又双叒叕延后了半年。

AMD Zen架构进步在我以往的不少文章里,都有比较详细的阐述,Zen 3已经事实上在单核和多核性能上实现了对Intel处理器的全面赶超——虽然Intel的marketing仍然相当顽强。而苹果Mac系列在抛弃Intel处理器之后,自研的M1芯片则可以说几乎让整个x86阵营汗颜,仅3.2GHz的主频、低很多的功耗,就能将Intel最高端的Core i9踩在脚下,并彻底无视Intel最新的Tiger Lake(十一代酷睿)。

所以美国西部时间1月13日,英特尔宣布新任CEO Pat Gelsinger的即将上任,换下Bob Swan。事实上在此之前,Intel首席工程官Dr. Venkata (Murthy)的离职就能够从公司管理层面,显现Intel对现状的反思。

本文篇幅较长,这里给出导读,读者可根据自己的兴趣,做选择性阅读。

● x86处理器做大小核设计的背景

● 大小核设计的意义

● Intel的初代大小核处理器Lakefield实际表现

● Lakefield的小核心Tremont(可选读)

● Lakefield的封装技术(可选读)

● Intel大小核处理器面临的问题和展望

x86阵营也开始做大小核

有关M1芯片为何能达到这个程度,我会另外撰文详述。M1的逆天表现虽然不是本文要谈的重点,不过M1的出现却已经向市场证明,Arm在PC高性能领域是大有可为的,与此同时还能兼顾低功耗。从极客湾测试的数据来看,日常工作中,M1版MacBook Pro的功耗之低,与整个x86阵营都是有量级差距的:B站看个视频,M1功耗在0.5-0.7W,而Intel Tiger Lake需要4-4.5W;待机功耗,M1达到了震惊PC处理器市场的0.02W,而Tiger Lake是1.1W。MacBook如今的续航因此可以达到20小时甚至更高。

这其实并不让人意外,毕竟Arm平台的大小核(big.LITTLE)设计早已是Arm芯片参与者做惯了的事。Arm过去始终在移动平台活跃,而手机之类移动设备对功耗是非常敏感的,所以处理器采用大小核心搭配是必须的。

而x86阵营的参与者,如Intel就是自PC处理器起家的,PC对功耗更不敏感(尤其是桌面PC)。所以PC处理器也更倾向于通过提升频率(而不是增加更多专用单元)来提升性能,自然也不存在“小核”设计。两者功耗上的差距显得相当顺理成章。

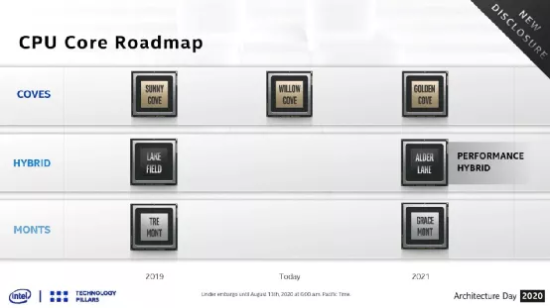

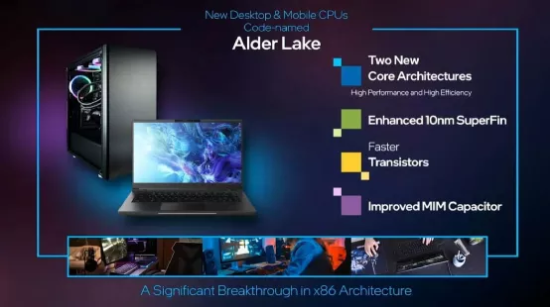

但在持续提频的道路上,移动办公逐渐风行的当下,Intel也一早就意识到了功耗需要有越来越高的优先级。这两天在美国进行的CES大会上,Intel再度提到了规划中的“混合x86产品”Alder Lake,也就是x86版的大小核设计。去年Intel的Architecture Day 2020上,Intel正式宣布Alder Lake路线图:未来的Alder Lake处理器,会将高性能计算核心(Golden Cove)与“高效率”核心(Gracemont)放到一起。

将其比作Intel版的M1芯片并不合理,毕竟Intel要做此类处理器的意愿也不是M1出现后才有的,不过两者大方向总算是趋同的。Alder Lake会面向桌面和移动两个平台推出(这里的移动主要只是笔记本或同类设备),这颗规划中的芯片也事实上成为x86阵营针对Arm大小核设计思路的反击(主要是骁龙8cx和苹果M1这类芯片)。不过在规划上,Alder Lake需要等到今年下半年。而且Intel在这种大小核设计方案上,也还处在试探期。

在Alder Lake之前,Intel在Architecture Day 2018上展示了其初代“混合x86处理器”产品:Lakefield,也是将Core(酷睿)和Atom(灵动)架构处理器核心放到一起,作为Intel版本的大小核。

如今Alder Lake相关消息仍然很少,本文尝试以Lakefield为依据,从技术角度谈谈x86阵营推行这种混合处理器,能否在Intel最艰难的历史时期,帮助Intel重回PC处理器市场巅峰——以及这种“混合”“大小核”设计究竟有多大价值。

另一方面,Lakefield处理器虽然目前的出货还非常少,而且由于规格定义并不面向高端PC(与笔记本)市场,但它几乎可以认为浓缩了Intel当下最先进的一批技术。所以对Lakefield剖析,也能更全面地了解Intel如今在PC处理器市场的处境和底牌。

而且Lakefield不仅标志着Intel PC处理器的未来规划,也预示了PC处理器整个市场的未来,即便它本身只是x86指令处理器的试水之作。(要知道AMD这边到现在其实都还没有自家的“小”核心设计,虽然早期架构的改款还是可以考虑)

大小核有意义吗?

从苹果开始为MacBook采用M1芯片,以及微软积极拥抱Arm推类似Surface Pro X这样的Arm笔记本设备(和Window on Arm)就不难发现,x86在笔记本这样注重移动性的设备上显得不够高效。抛开兼容性问题不谈,Surface Pro X在采用高通处理器以后,续航就远高于x86版本的Surface;新版MacBook就更不用说了。

如前文所述,Arm的低功耗与其很早就推big.LITTLE(以及DynamiQ灵活搭配)设计是有很大关系的(更多原因我将在M1架构分析中阐述)。这种大小核设计,在面对轻度工作负载时选择小核心,而在需求高性能时则用大核心去跑任务。这种方案基于一个事实:两种核心在不同的性能区间,其功耗表现是大不一样的。

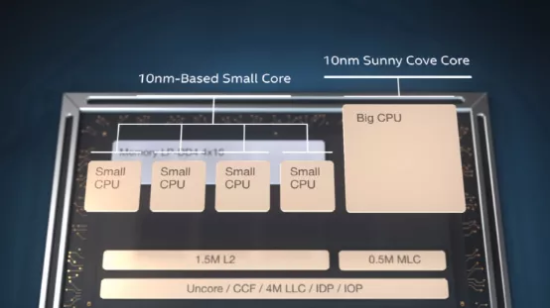

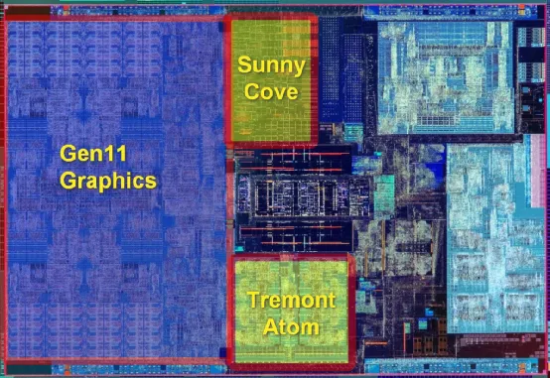

Lakefield“大小核”的整体设计大致上可以反映这个思路。Lakefield搭配的大小核分别是Sunny Cove(十代酷睿上的核心)和Tremont(最新的Atom核心),具体是1颗Sunny Cove搭配4颗Tremont。Arm阵营如今颇为常见的搭配方法是4+4,或者1+3+4/2+2+4,越来越多的手机芯片倾向于大中小三簇核心的搭配方法。

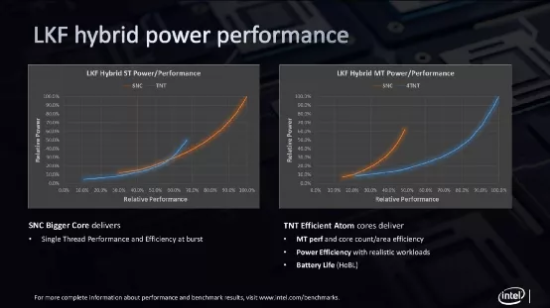

用一张图大致能够说明,大小核设计带来效率提升的价值:

这张图是Intel官方提供解释Lakefield两种核心,在不同性能下的功耗情况的:横轴代表相对性能,纵轴代表相对功耗,随性能提升,功耗也在提升。

左边这张展示的是单线程下,两种核心的性能与功耗关系(橙色代表Sunny Cove-SNC,蓝色代表Tremont-TNT);右边这张图标识的则是多线程性能与功耗关系。比较显然的一个结论是,仅看单线程情况,在较低性能状态下,小核心能够达成更低的功耗;但到了高性能区间,小核心的功耗反而会崩,此时大核心的效率会更好。

更具体地说,在相对性能低于58%时,Tremont核心效率高很多,而在性能高于58%时,Sunny Cove显然是更好的选择。当然多线程性能又是不同的,毕竟Sunny Cove核心在Lakefield中就只有一个。Intel提供的数字是,Tremont在能效上打败Sunny Cove时,最高可以达成Sunny Cove 70%的性能;性能水平介于Sandy Bridge(2-3代酷睿)和Haswell(4代酷睿,2013-2014年)之间——整数性能与Haswell相近,同时效率会高很多。

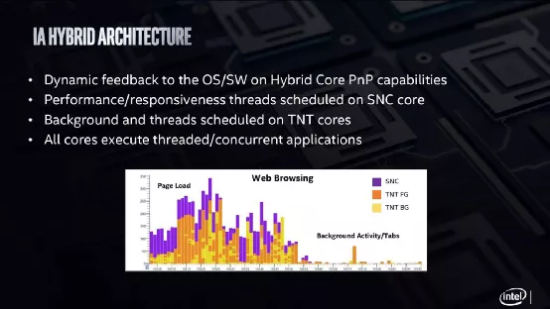

事实上,Lakefield并不通过任务负载性能需求高低来决定用哪种核心工作。在Intel的定义中,Sunny Cove针对需要快速响应,以及与用户体验切身相关的线程;而Tremont则针对要求多线程性能的相关任务,以及需要在较高效模式下跑的非用户相关后台任务。比如视频编码工作,通常考虑用四个Tremont核心来跑,Windows后台任务也交由Tremont完成;类似用户点击开始菜单、滚动网页这种操作,要求快速响应,则交给Sunny Cove。

x86初代大小核处理器的性能怎么样?

Lakefield(酷睿i5-L16G7)的其他参数还包括CPU基频1.4GHz,大核心的最高睿频3.0GHz(全核最高1.8GHz),不支持超线程,TDP 7W;核显为Gen11(GT2 64EU,500MHz,频率远低于Ice Lake);堆叠了8GB LPDDR4-4267内存;计算die部分的工艺为10nm。

从这些配置来看,就知Lakefield在性能表现上可能并不怎么样,定位的就是低功耗便携式或者一些二合一设备。尤其多线程工作基本全部交给Tremont去完成——这让Lakefield在很多情况下变身Atom处理器——对不起酷睿的名头。

即便有一颗Sunny Cove大核,也不支持超线程。另外比较重要的一点是,原本Sunny Cove是支持AVX-512指令的,但因为Tremont小核不支持,所以为了达成“混合CPU”的这种大小核设计,唯有令两者对支持的指令完全达成一致,所以Sunny Cove也就阉割了对AVX-512指令的支持,另外阉割的还包括了AVX、AVX2,以及Tremont小核心的GFNI、ENCLV、CLDEMOTE等指令。

像这样异构核心方案,在指令方面需要满足木桶最低板的原则(或者跨所有核心的ISA兼容性),在Arm世界也同样适用。否则线程在大小核之间迁移时就会出问题。所以Cortex-A55作为Arm处理器的小核心被用了这么多年不动摇,也是这个道理。

来源:AnandTech[2],四颗Tremont核心簇的面积和一颗Sunny Cove相差无几

无论AnandTech还是WikiChip,都认为从Lakefield的die shot来看,Sunny Cove核心部分的AVX-512相关的单元并未被实际移除,虽然Intel宣称是“移除”了的。

Intel宣传的数字是,相比Amber Lake i7-8500Y(Intel的超低压处理器,TDP 5W),Lakefield的多线程性能高24%,单线程则快12%,图形性能提升70%——这些变化实则都在预期内。以及有大核心的加持,web性能高出33%,效率提升17%——这一点对比的显然就是单纯的四核Atom了。可预期的是看B站会比以前省电……

另外比较重要的是每瓦性能提升24%(相比Amber Lake),待机功耗“大幅降低”,达到2.5mW左右——这就和前文列出M1的待机功耗数字差不多了。达成最高的效率原本就是这种设计的重要目的。苹果在发布会上最爱谈的就是每瓦性能以表现芯片的高效率。在Architecture Day 2020上,Intel就宣称Alder Lake将能够达成Intel有史以来最高每瓦性能——当然这是Lakefield后续产品了,也是Intel的预期。

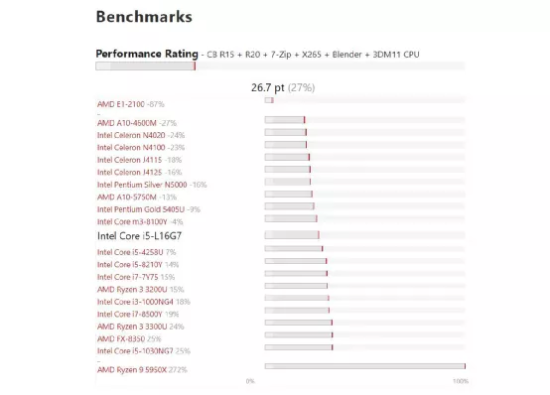

当前针对Lakefield尚无十分系统的性能测试。已经上市的Lakefield产品主要包括了联想ThinkPad X1 Fold、三星Galaxy Book S以及微软Surface Book Neo。NotebookCheck的实测数据是,Lakefield(i5-L16G7)综合性能(也包括了核显性能)弱于超低压的酷睿i5-8210Y和四代酷睿42 85U。

来源:NotebookCheck[3]

这个数据可能并不是很合理,一方面在于NotebookCheck用于跑分测试的Cinebench版本(R15与R20)在多线程性能测试中甚至都无法用上Lakefield的Sunny Cove大核(但却的确能反映其实际使用情况,因为如前文所述,Lakefield中的Sunny Cove并不像很多人理解的那样,是简单用于“高负载”任务),另一方面和OEM厂商的具体实施方案有关。

Cinebench R23似乎是目前唯一能够实现5核全开的测试,但网上找不到R23的Lakefield跑分。总之Lakefield大致上也就用来做word或者ppt文档以及看看网页和爱奇艺了。

有关Tremont小核心(选读)

很多同学抱怨我文章写太长,所以更全面的微架构分析文章,后续我会发到我的面包板专栏,感兴趣的同学可以前往关注。本文我只简单聊聊Lakefield中的小核心Tremont,毕竟大核心的Sunny Cove其实算是非常知名了,Intel十代酷睿的Ice Lake用的就是这个核心。而且Lakefield也实在谈不上“高性能”,它本身更重在“低功耗”上。

Tremont相比前代(Goldmont Plus,2017年)主要是提升单线程性能,IPC有超过30%的提升。作为Atom处理器中的一款产品,它重在考量每核功耗与每核面积。所以前文给出的die shot就能看出,Lakefield中的Tremont四核心簇整体尺寸才相当于一个Sunny Cove。

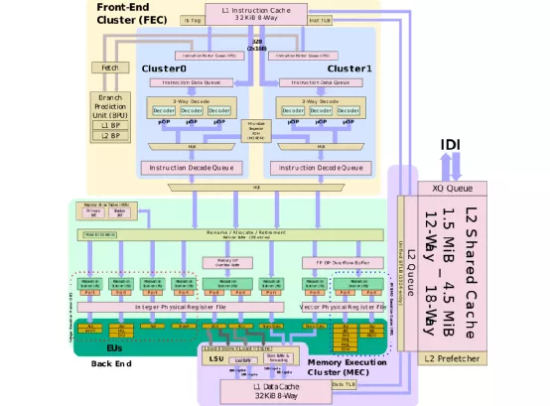

来源:WikiChip[4]

从“小”核心的角度来说,Tremont与知名的Arm Cortex-A55小核心并不是一个量级。Tremont首先是个乱序核心,前端解码宽度6-wide(虽然是分两组),这就决定了它比A55这样的选手还是壮实多了。这一点和苹果的思路就很像(2019年苹果A12的Tempest小核心,在性能上几乎达到了Cortex-A72的程度)。

其余具体的微架构可参见上图,包括allocation 4-wide,re-order buffer增加至208条(+119%),后端有10个执行端口,双load/store管线;L2 cache最高可配置4.5MB,L1-D cache增加33%,L2 TLB(页表缓存)增加到1024-entry;另外还有新指令引入——不过对Lakefield而言,这一点就不存在了,前文已经提到。感觉整体看起来,这都不像是个“小”核心。

其最大的变化在前端,包括分支预测单元升级——接近于“大”核心级别的精度(两级结构);以及最重要的解码宽度变化。不过这个所谓的“6-wide”宽度并不是类似酷睿5-wide那类方案(1个复杂decoder,4个简单decoder,再加μop cache),实际上是两组3-way对称解码。每一组都有自己的指令流。配合分支预测器,预测指令流可以进第二组(上图的Cluster 1),不打断第一组(Cluster 0)的工作,两组并行预测、读取、解码。

这种实际上的3-wide设计,相比真正的6-wide解码要节省面积和功耗,没有μop cache。Intel宣称这种设计能够平衡资源。Tremont也支持仅开其中一组的模式,预期实现更低的每核峰值功耗。更多包括re-order buffer加深、执行引擎和存储子系统拓宽等,本文皆不再赘述。还有一些额外的特性,比如RDT技术支持,可实现带宽分配、QoS、优先级之类的操作(服务器芯片中常见);Speed Shift技术;信任安全启动;内存加密等。

当大小核遇上3D封装(选读)

抛开更微观的层面不谈,Lakefield整体看来还是比较草率的,包括1+4的这种组合方式,及其表现出的实际性能。Lakefield之所以没有加入更多的Sunny Cove大核心,很大程度应该也是受限于Sunny Cove核心的体积和功耗。以Lakefield如今计算die占据的82mm?来看,及其预定义的尺寸,它很难再塞入更多CPU核心,何况Sunny Cove的功耗也实在不算低。

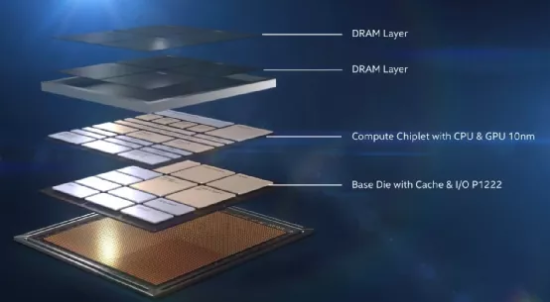

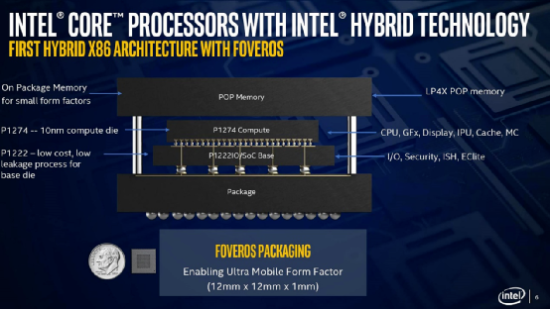

所以我们才说,Lakefield很像Intel针对“混合”或者大小核设计的一个试水,和打怪升级的必经之路。而作为一款实验性质的作品,Lakefield不仅有Intel最新的大小核,而且在封装上也算是集Intel芯片制造厂的大成了。它用上了传说中的Foveros 3D芯片堆叠技术,也是Intel首款采用这种封装方案的芯片。

前面谈的这些CPU大小核、GPU等都是Lakefield的计算die(计算die上另外还包括了图像处理单元IPU、LPDDR4X内存控制器、Gen11 Display engines等),采用的是Intel的10nm工艺(与Ice Lake一致,理论上属于Intel的二代10nm工艺);有关Intel 10nm工艺本文不再详述,详情参见我的面包板专栏文章。

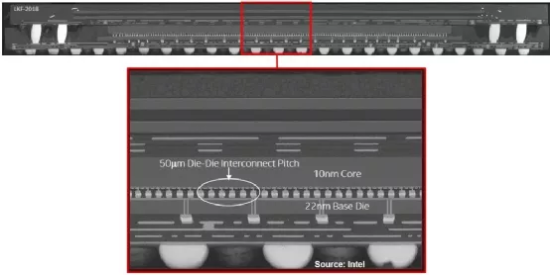

而在计算die之下,还有个base die。下面的这片base die主要是处理器外设的active interposer(主动中介层)。Active interposer相比传统passive interposer,不只是用于连接的中介层,本身也发挥功能逻辑的作用,其上包含各种PCIe 3.0、各种I/O控制、音频codec、安全等。Base die所用的制造工艺是22FFL——22FFL并不是早期的22nm工艺,而是14nm的功耗优化版(更稀疏的版本),针对的就是更高效的IO。22FFL则必然又在成本上显著低于10nm了,这也属于典型的chiplet设计和制造思路。

计算die和base die之间采用50μm间距bump的die-to-die互联(Foveros Die to Die Interface),承载信号(数据)和供电的连接。这种互联应该是3D堆叠方案上的绝对难点。Intel宣称其最大传输速率是500MT/s(mega-transfers per second),而且每bit数据传输耗能0.2pJ(皮焦)。0.2pJ在die间数据传输的耗能量级上可以认为是非常小的,这应该也是实现低功耗的一部分。

值得一提的是,IO部分Lakefield仅给到了PCIe 3.0六条通道支持,这就决定了其IO连接会相当捉襟见肘。ThinkPad X1 Fold为Lakefield配套的SSD,仅拿到PCIe 3.0 x2的通道,带宽因此大受限制;配独立GPU什么的,那也是想都不用想的了。[5]从这样的小细节也能看出Lakefield试水的本质。

最后在Lakefield整个封装的最上层是内存(Package on Package),有4GB和8GB两种规格可选,应该是来自其他内存制造商的定制方案。值得一提的是,内存与中间的计算die之间并没有采用什么黑科技连接方式,与CPU的通讯是需要经由最底层的package转道再经过base die之后,再到compute die的。它也没有M1芯片那样的Unified Memory Architecture特性。

这样的堆叠方案下,散热会成为一个大问题,Intel为此似乎还是颇费了一番功夫的,不过现阶段主要在不同IP模块的设计上做到减少局部的高温聚集点、互联金属层厚度控制等,所以散热在设计上有更高的优先级;另外Intel还探讨过在两个die之间采用“流体通道(fluidic channes)”的可行性——这就属于未来的方向了。有关Lakefield封装细节,AnandTech的文章中有比较详细的阐述[2],我也会在面包板专栏再行刊文。

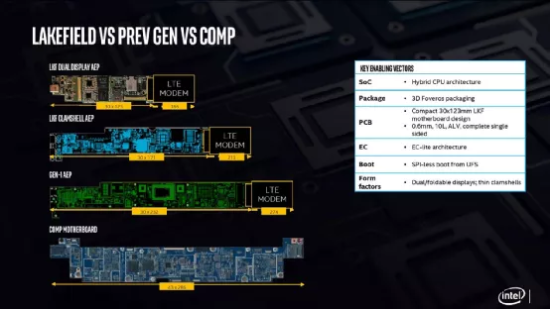

经过这种Foveros 3D堆叠后,Lakefield芯片整体达成了12x12x1mm的三围尺寸。板级设计也就可以更为紧凑,相比之前的低功耗CPU实施方案,主板可以减少60%的尺寸。加上LTE modem的话,整体主板尺寸总算是可以和高通的设计比一比了。

Lakefield真的能成吗?

最后来稍稍总结一下Intel在Lakefield处理器上现存的问题。首先Lakefield基本上是很难获得市场大范围的肯定的,即便它塞入了Intel这么多最尖端的研究成果。不过Lakefield作为Intel首款涉足大小核设计的处理器产品,其积累经验的作用也明显大于市场本身。下一代的Alder Lake才是值得观察的关键。

所以这个问题应当换成Intel的大小核设计能成吗?

事实上Intel在这种非其传统强项的处理器产品中,遭遇的问题可能是形形色色的。从具体到抽象总结这种处理器“能成吗”的关键:

其一是scheduler(调度)。Intel此前并没有设计大小核处理器的经验,Windows也始终不曾有不同类型的核心间做线程(进程)迁移的scheduler(微软和高通勾搭上之后,必然有密切合作在不同CPU设计间管理负载的scheduler,但至少x86是没有的;不过从Wikichip的介绍来看,Intel似乎也提交过非一致指令集的异构核心一起工作,针对操作系统的算法和加强[6][7])。要知道Android和Arm在这方面可是有着比较长期的演进的,包括线程迁移对实际体验造成的影响;苹果就更不用说了。

Cinebench更早版本在做Lakefield多核性能测试时,并不会启用Sunny Cove大核可能就能说明一些问题(但AnandTech猜测这可能是功耗或者热聚集考量所致)。

传言未来的Alder Lake预计会包含8+8的设计,这其中的线程调度就不只是Intel如今列出、如上图这样Lakefield简单的网页浏览场景了。那将更考验Intel的功力。

第二是处理器本身的性能。Lakefield宣传中似乎的确有着不错的功耗表现,但性能实在是不大够看。这应该并不是什么大问题,一方面在于Lakefield本身就不定位在高性能,另一方面则是这款产品试水和积累经验的成分居多。在Architecture Day 2020之上,Raja Koduri表示Intel从Lakefield身上学到了很多东西,Alder Lake未来会聚焦到性能上。

终极问题大概是,在性能和效率上Intel能否做到苹果M1那样的程度。M1芯片表现出的性能和效率,我个人看来是基于三个要素共同构成的:其一是超宽的处理器架构,其二是有针对性地添加一些专用单元,其三则是对自家封闭生态超乎寻常的掌控力(令其能够很随意地做出同一内存架构这样的东西)。

这将在未来M1的文章中做详述。这三要素可认为是仅有苹果这种掌控从芯片设计到开发生态,到消费终端产品销售全环节的企业才有的资源。比如前两者,超宽处理器架构和专用单元是需要以die面积(即成本)为代价的,苹果可以这么玩是基于其终端产品的高利润与高销量;对于Intel、高通这种单纯赚取处理器利润的厂商,这种玩法非常不经济(x86还存在变长指令不利于解码宽度拓宽这样的现实问题)。要达到M1的性能水平不难,但效率就没那么简单了。

还有其他的一些妥协,比如说前文提到的为实现指令的对称性,Lakefield不支持AVX指令——这原本可是Sunny Cove主打的升级特性;再比如3D堆叠的两层die分别用了两个PMIC(电源管理IC)。这些其实都表明Lakefield的不成熟,不过这些问题未来都有解决的办法。

最后更抽象的是,是Intel的速度问题。这里的速度是指Intel行事与决策的响应速度。不说Skylake缝缝补补新三年旧三年,最典型的是芯片制造工艺已经落后于台积电,且可预期的未来,行进速度还将非常缓慢。比如下半年大小核处理器Alder Lake要用上10nm Enhanced SuperFin(应该是第四代10nm工艺),这还是预期中的。届时的市场格局或许都不好说了,以及7nm工艺遥遥无期(最早一批7nm要等到2022年下半年或2023年上半年)。

若以多年前Intel在PC处理器市场的地位,这些问题或许都不足多虑。AMD推土机推了那么多年,苹果也还偏安在iPhone上,Intel有的是时间;但在如今这般光景下,情况就相当不乐观了。

好在2021年下半年也还不算遥远。Intel即将上任的CEO Pat Gelsinger也有多年技术背景,这预计也会加快Intel技术推进速度,这正是目前Intel最需要的。Intel在去年的ISA Extensions Reference手册上确认,Alder Lake还将加入新指令支持[8],包括LBR、HLAT、SERIALIZE,其中LBR可用于分支提速,对性能还有价值。从多方面来看,传说中拥有最高每瓦性能表现的Alder Lake都成为Intel规划的产品线中让人最为期待的处理器,并且真正让我们看到Intel在大小核设计上的实力。