SiFive开发出128核的RISC-V,与X86和ARM差距进一步缩小

2021-10-28

来源:半导体行业观察

SiFive于2016年脱颖而出,成为微控制器的小型低功耗内核开发商。到 2020 年底,该公司拥有可以运行 Linux 的芯片,本周表示它开发了一个 CPU 内核,可与设计的现代产品相媲美英特尔和 Arm。该公司认为,此类高性能设计可用于多种应用,包括具有128核的服务器级片上系统。

SiFive 的下一代高性能内核“在单核性能方面与英特尔的 Rocket Lake 系列和Arm 的 Cortex-A78设计接近,”SiFive 产品营销和传播高级总监 James Prior ,告诉The Register。目前细节很少,但Prior暗示下一代核心在架构上与其现有的Performance P550设计相似,但在各个方向上都进行了增强以提取更高的性能。

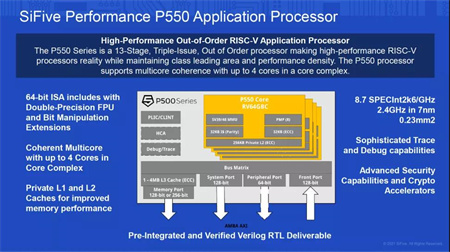

SiFive的Performance P550

今年早些时候,SiFive 推出了新的Performance系列 P550 通用内核,该内核基于该公司的 64 位 U84 微体系结构,具有13 级、三发射、无序流水线,针对多核应用处理器。P550 内核具有专用的 2x32KB L1 和 256KB L2 高速缓存、具有位操作扩展的数据精度 FPU,并支持多核一致性配置,在一个内核复合体中具有多达四个内核和统一的 4MB L3 高速缓存。

该公司声称 P550 内核在采用 7 纳米制造工艺时的尺寸为 0.23 平方毫米,并且可以在 2.40 GHz 左右运行。至于Performance P550 的 SPECINt 2006 得分为 8.65/GHz,可与当代 Arm 和 x86 内核的性能相媲美。同时,SiFive 表示,与 Arm 的 Cortex-A75 相比,P550 每平方毫米的性能提升了三倍。

P550 可从 SiFive 获得许可。由于这只是一个 CPU 内核,被许可方可以向其添加各种专用加速器、IP 和 I/O 接口,以获得满足其需求(或目标细分市场/工作负载)的独特片上系统。

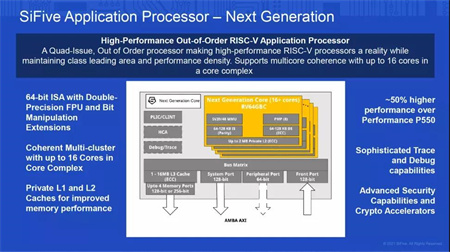

SiFive的Performance P550:每个SoC最多128个内核

SiFive的下一代核心应用程序的性能要求似乎是基于与P550非常相似的微架构,但这一款实际上是一个四个问题的Oder微架构,每个时钟的性能更高。除了一个更广泛的问题,未来的核心还将有更大的L1缓存(高达128KB),以及高达2MB的私有L2缓存。此外,它支持多核一致性,在一个复合体中具有多达 16 个内核和 16MB 三级缓存……

SiFive 声称,与 P550 相比,下一代 Performance内核可以提供 50% 的更高性能。此外,还可以将设计一直扩展到 128个内核并解决对性能要求很高的应用程序。由于具有 128 个内核的 SoC 用于虚拟化环境,因此该内核还添加了管理程序和中断等功能。同时,由于每核性能与 Arm 和 Intel 的最新微架构不相上下,SiFive 的下一代内核可以随着时间的推移解决高性能计算 (HPC) 应用程序,正如 监督开发的组织 RISC-V International所设想的那样RISC-V 指令集架构。不过,我们希望 HPC 客户希望从 SiFive 获得更多专有的东西。

James Prior 表示,下一代内核将在明年作为 RTL 交付品提供。客户还可以在 FPGA 模型上测试驱动内核。