Integrity 3D-IC引领3D封装设计未来十年

2021-10-29

来源:cadence

编者按:Cadence公司发布了突破性新产品Integrity 3D-IC平台,该工具运用系统级思维,将设计规划、物理实现和系统分析统一集成于单个管理界面中。设计工程师可以利用该平台集成的热、功耗和静态时序分析功能,实现由系统来驱动的PPA 目标。日前,Cadence公司数字与签核事业部产品工程资深群总监刘淼接受了记者专访,详细介绍Integrity 3D-IC的独特之处。

过去10年,整个业界都在追求趋势摩尔定律,硅材料的极限很难有突破的前提下,从2D走向3D的封装技术,从系统角度出发推进了芯片的功耗和性能空间。

Cadence公司数字与签核事业部产品工程资深群总监刘淼表示,2.5D和3D封装技术使得芯片里或功能间的连线变短了,一方面降低了线上能量损失,另一方面减小了信号的延迟,从而获得了低功耗和高性能。

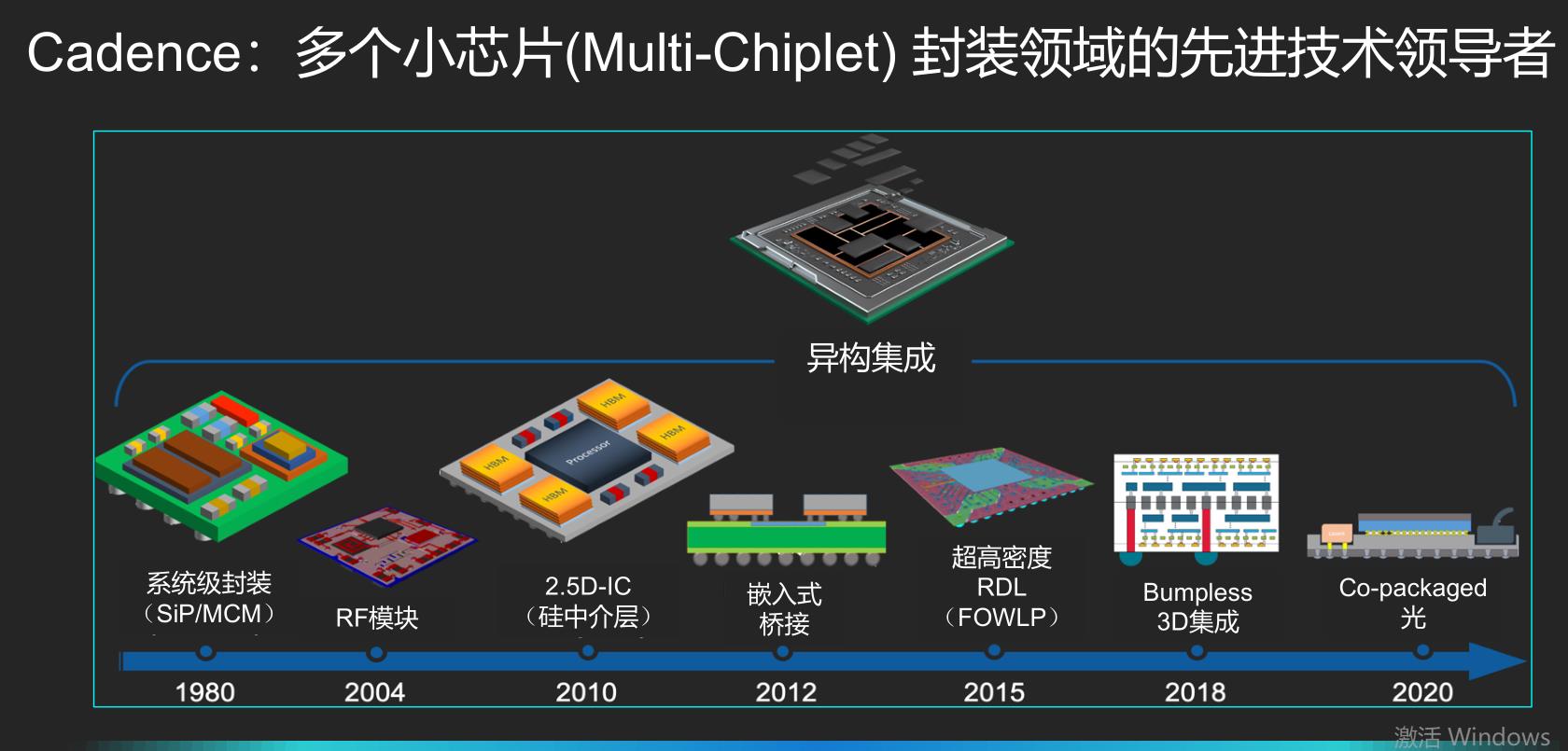

据刘淼介绍,Cadence在多芯片(Multi-Chiplet)封装领域已经耕耘了20多年,从1980年就开始在做系统级的封装,2004年做RF模块,2010年研发2.5D封装设计技术,2012年推出了嵌入式键桥技术,2015年推出了超高密度RDL(FOWLP),2018年的3D集成工具Bumpless,以及2020年的硅光集成工具Co-package。

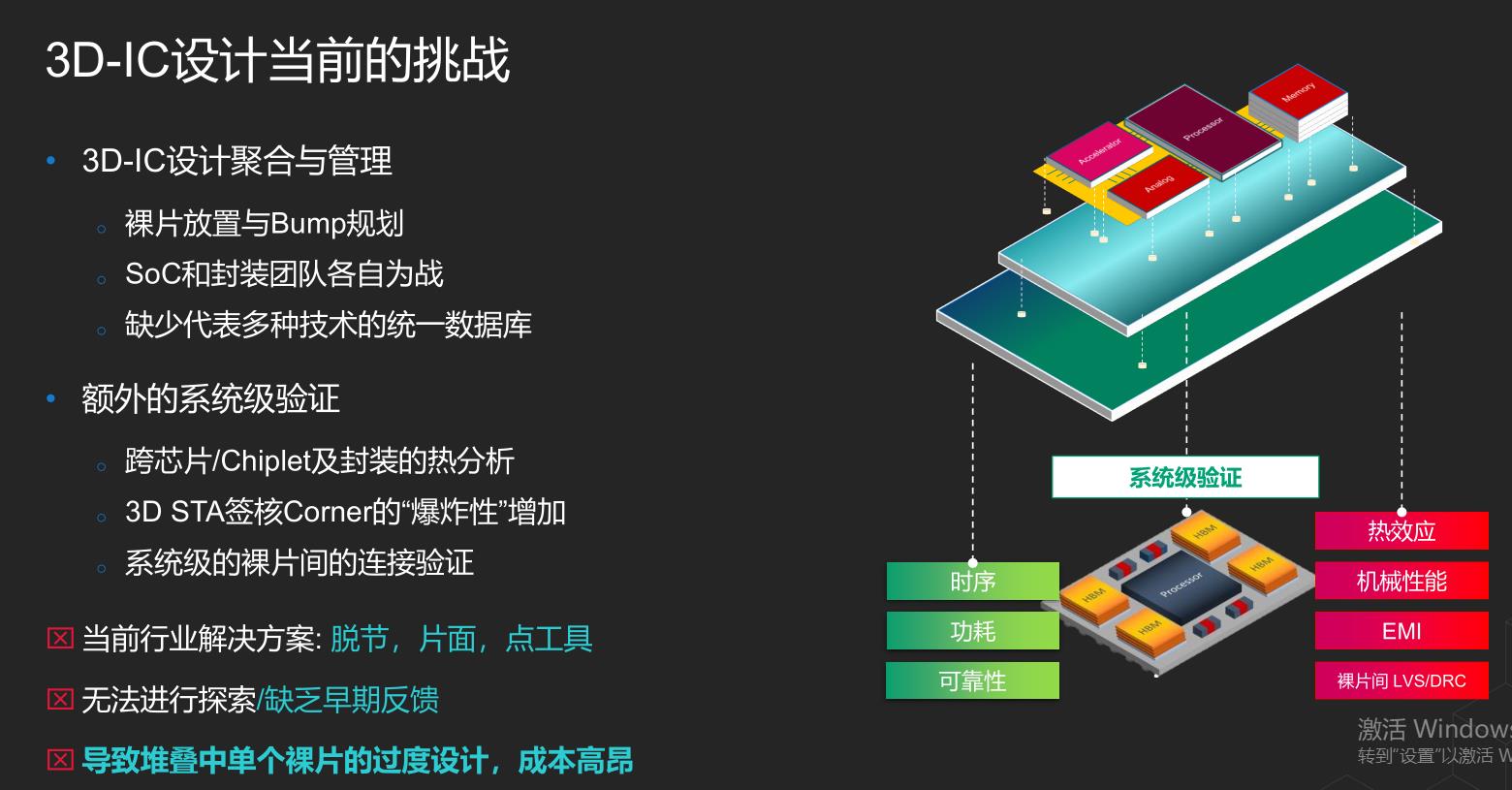

封装技术向着3D进军的过程中,设计师面临着很多挑战。

首先要进行Bump规划,即讨论尝试找到芯片放置的最佳方案;其次,实现3D封装要解决数字技术部分和模拟技术部分间的通讯和连接问题,这需要数字工程师和模拟工程师紧密协作,这里面有沟通效率的挑战,第三个挑战就是系统级验证工作,这是一项需要调动更多设计部门参与的工作,比如跨芯片/Chiplet及封装的热分析和系统级裸片的连接验证;第四是STA的签核,3D封装设计里的STA的签核会有爆炸性的增加,2D时代的手工完成几乎不可能。

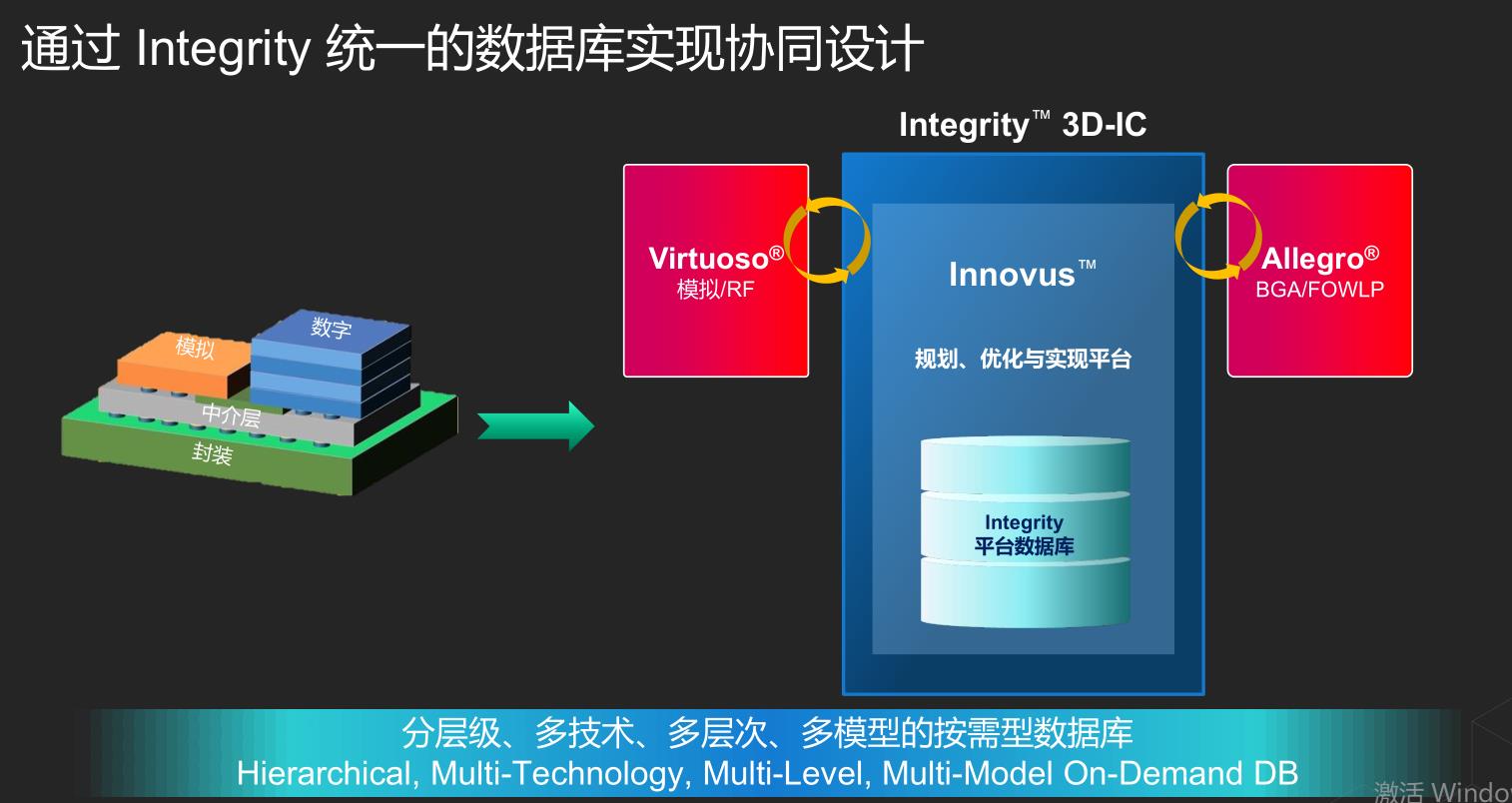

为了应对上述挑战,Cadence公司最新推出Integrity 3D-IC开放平台,这是一个跨集成电路全流程的平台工具,横跨芯片设计,芯片设计实现,以及到系统规划、系统分析的全流程产品。

Intgrity 3D-IC平台作为Cadence广泛3D-IC解决方案的组成部分,在数字技术之上同时集成了系统、验证及IP功能。

广泛的解决方案支持软硬件协同验证,通过由Palladium ® Z2和Protium X2平台组成的Dynamic Duo系统动力实现全系统功耗分析。

平台同时支持基于小芯片的PHY IP互联,实现面向延迟、带宽和功耗的PPA优化目标。另外,Intgrity 3D-IC平台支持与Virtuoso设计环境和Allegro技术的协同设计,通过与Quantus ExtractionSolution提取解决方案和Tempus Timing Signoff Solution时序签核解决方案提供集成化的IC签核提取和STA,同时还集成了Sigrity技术产品,Clarity 3D Transient Solver,及Celsius Thermal Solver热求解器,从而提供集成化的信号完整性/功耗完整性分析(SI/PI),电磁干扰(EMI),和热分析功能。

刘淼表示,全新Integrity 3D-IC平台和更广泛的3D-IC解决方案组合,建立在Cadence SoC卓越设计和系统级创新的坚实基础之上,是Cadence公司能系统设计(Intelligent System Design)战略的代表产品之一。