PCIe 6.0时代下的IP挑战

2021-11-03

来源:半导体行业观察

现在云计算、存储和机器学习等领先应用需要传输大量数据,这要求开发者以最小的延迟集成最新的高速接口,以满足这些系统的带宽需求。PCIe作为历史上使用最广泛、可扩展最强的互连技术,其创新的步伐正在加快,如今PCIe 6.0标准已然来临。对于高性能计算、AI和存储SoC开发者来说,转向PCIe 6.0为设计师提供了一系列关于IP、SoC和系统的考虑。及时理解并做好所需要的面对的关键变化,以及由此带来的设计挑战,将有助于其顺利过渡到PCIe 6.0时代。

PCIe 6.0的新变化

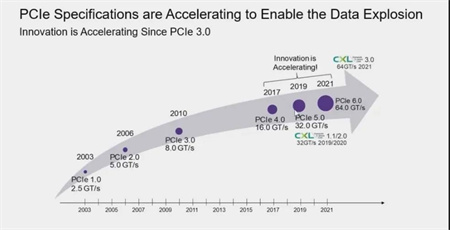

过去,PCIe的标准基本保持在3-4年一更迭的速度,但自PCle 3.0以来,PCIe的标准正在快速演进,基本在2年一更新,到现在已经到了PCIe 6.0的时代。PCle标准的加速也是数据爆炸的使然。

图1:PCIe标准的演进路线图(来源:新思科技)

那么,PCIe 6.0有哪些新变化呢?首先是数据速率从32GT/s翻倍至64GT/s,吞吐量在大多数情况下超过两倍;其次,保持其兼容性,PCIe 6.0向后支持所有PCIe的标准;再者,PCle 6.0 PHY IP必须为所有PCle 6.0数据速率提供出色的性能,所以从NRZ编码转换到PAM-4编码,以及由此带来的纠错影响,PAM-4适用于新Gen6 64GT/s。

下图就很好的解释了为何PCIe 6.0会引入PAM-4。可以看出,当数据速率从16GT/s加倍到32GT/s时,奈奎斯特频率也从8GHz加倍到16GHz,使得PCIe 5.0的频率相关损耗比PCIe 4.0要严重得多。再加上电容耦合(噪声和串扰)的增加,使得PCIe 5.0通道成为最难处理的NRZ通道。如果PCIe 6.0仍然保留NRZ信号,则奈奎斯特频率将增加到32GHz,通道损耗大于60dB,这对于实际系统而言太大了,因此需要从NRZ更改为PAM-4信号。这一变化意味着发射和接收的信号现在有四个不同的电压电平,而不是两个。

图2:NRZ通道面临的挑战(来源:新思科技)

其他额外的变化是,PCIe 6.0采用了新的轻量级FEC,平均往返时延约为2ns;PCIe 6.0引入新的FLIT模式,采用了256B FLIT作为标准大小的数据传输单元;由于FEC要求,FLIT模式现在支持所有数据速率;PCIe 6.0引入了一种新的低功耗状态,称为L0p,允许PCIe 6.0链路在不中断数据流的情况下扩展带宽利用率,从而降低功耗;为了在64GT/s下保持性能,PCIe 5.0的768个标签限制远远不足以支持大多数PCIe 6.0系统的性能,因此标签数量最大值急剧增加,变为基于14位的15,360个标签。除此之外,单个应用程序接口可能不再足够,所以使用多个应用接口来提高PCIe 6.0链路利用率。

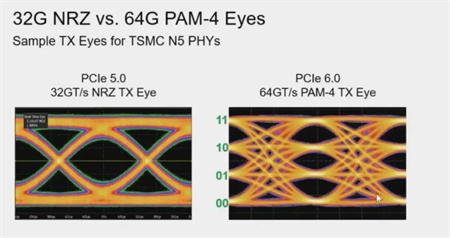

下图显示了在相同比例的眼图,图1(a)显示了使用NRZ信号的PCIe 5.0的眼图,包含两个电压电平和单眼。图(b)显示了使用PAM-4信号的PCIe 6.0的眼图,包含四个电压电平和三眼。由于发射端(TX)的总体电压摆幅没有增加,因此PAM-4系统中每只眼的可用电压仅为NRZ的1/3。因此,信号在TX和接收端(RX)之间遇到的任何噪声都会对信号完整性造成更大的损害。这也是为什么需要在进行PAM-4信号传输时,需要额外的FEC支持的原因。

图3:32G NRZ VS 64G PAM-4眼图(来源:新思科技)

PHY IP该如何应对?

要满足PCIe 6.0的上述新变化,对PHY层来说也有一定的需求变化。因为PCIe 6.0需要支持64GT/s的带宽,所以速率需要从原来的32G变为64G。另外一点是不仅要支持PCIe 6.0 64G的PAM-4,还需要支持从低速的2.5G-32G的NRZ,向后兼容所有PCIe的标准。另外还需要引入轻量级的FEC,使得PHY BER能满足<=1e-06的要求。轻量级FEC结合CRC和重试,以减少延迟影响。还需要支持新L0p的低功耗要求。在PCle 6.0速率下,支持32db的信道损耗。

大家都知道,新思科技在Serdes中已经可以达到112G的Ethernet,但对于PCIe 6.0来说,并不是只通过降速就可以满足其要求,还要考虑低延迟、SSC/SRIS的支持、更复杂的发射机、低功率状态、100x更严格的误码率要求等等。所以对于PCIe 6.0,新思有单独的支持64G速率的方案。

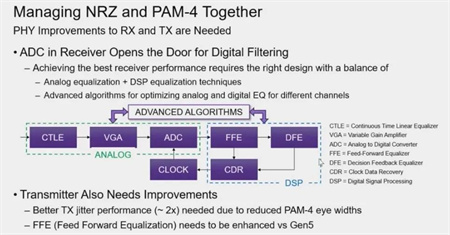

上面我们提到PHY的接收通路不仅要满足NRZ,也要满足PAM-4。所以PHY在接收端采用了特别的模拟+DSP的组合架构,可以满足对于功耗和接收性能的兼顾。再者,发射通路也需要加以改进,如上图3所示,PAM-4的信号眼图相对NRZ会变得更为严格,所以对于发送通路的发送信号的质量要求会更高。由于减少了PAM-4眼宽,所以需要更好的TX抖动性能(~ 2x);而且与Gen5相比,FFE(前馈均衡)也需要加强。

图4:为了同时满足NRZ和PAM-4,需对接收端和发送端进行改进(来源:新思科技)

PCIe 6.0 FLIT模式的新L0p低功耗状态,能带来真正的带宽/功率缩放。L0p可以根据链路的数据吞吐量去动态改变有效的车道(lane)的数量。比如说在高吞吐量的需求情况下,可以将所有的车道都开起来,当不需要那么高的吞吐量时,可以关闭多余的车道,这样就可以做到真正的节省功率。值得一提的是,这种调整是不需要做PHY层的训练等,这是PCIe 6.0新的L0p的低功耗Power State的功能。

图5:新的L0p可以根据链路的数据吞吐量去动态改变有效的车道(lane)的数量 (来源:新思科技)

但在数据结构方面,PHY是有所区别的。前文我们提到PCIe 6.0采用了256B FLIT作为标准大小的数据传输单元。这就要求在FLIT模式下需要将可变数量的TLP重新封装到256B固定长度的FLIT数据结构中。这是IP设计中需要引入的新的变化。此外,FLIT自带完整性的校验,所以在吞吐量和数据传输方面的开销对于TLP或者DLP会更有优势,所以可以将TLP或DLP直接封装到FLIT里面,FLIT的overhead比较小,所以对链路的性能是有提升的。

图6:使用FEC需要固定大小的数据单位,而不是可变的TLP(来源:新思科技)

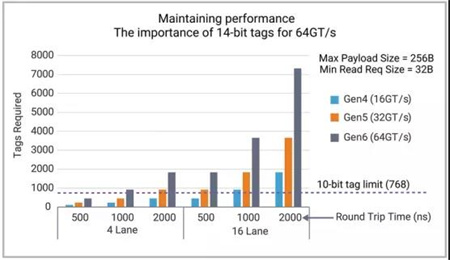

PCIe 6.0为了满足高效的post数据传输,需要引入高比特tag的需求。如图7所示,当16个lane都工作的时候,要满足高性能的要求需要将近7000多个tags的数量,意味着tag的位宽要达到14bit,所以进行控制器设计的时候,需要能够处理这么多的post的能力。

图7:达到第4代到第6代链路的最大吞吐量所需的tag数量(来源:新思科技)

在应用层接口方面,PCIe 6.0可以做到1024G这样高的数据传输,如果在应用层采用单独的接口的话,链路利用率会比较低,所以PCIe 6.0将采用双接口的方式。例如在32Byte的Payload下面,两个接口相对于一个接口的话,其链路利用率将能达到80%的提升。

图8:单接口和双接口应用程序接口的传输链路利用率和控制器数据路径宽度(来源:新思科技)

对验证IP和系统层面的挑战

PCie 6.0的到来也为验证和系统层面带来的许多新的挑战。首先,验证必须要充分涵盖PAM-4、FEC、FLIT模式、Equalization的更新以及PIPE 6.0接口。再者,验证需要校验方案中有大量的协议检查,降低PCle 5.0到PCle 6.0迁移的风险。需要增强对模拟误码率的功能检测,还需要完整的FLIT控制和操作的验证。

所以综合来讲,PCIe 6.0标准下的验证IP应该能支持最新的PCle 6.0规范版本;要有一个全面的源代码测试套件;同时使用分层控制实现广泛的协议检查,可以覆盖到成千上百的应用需求;支持分岔的多链路DUT,对内置(控制器)和客户(客户自己)情况的鲁棒错误注入的支持,支持所有拓扑,包括根复杂,端点,应用程序层,主动/被动监控,也要覆盖到广泛的PHY验证。

在系统层面,如果PCIe 6.0和控制器能有综合完整的解决方案,对于系统的吞吐量、兼容性和有效性来说是非常有利的。另外,PCIe 6.0采用的是PIPE接口选项,PIPE 5接口规范不支持PCIe 6.0,必须指定支持PCle 6.0的最新版本PIPE 6规范。再者,PCle 6.0的行业正在转向SerDes架构,它简化了64GT /s PHY设计,支持CXL 3.0对低时延的要求。

此外,还要考虑数据路径和时间的问题,只有2个可行的选择,以权衡时间关闭和延迟。一个是在1 GHz定时关闭。要关闭1GHz PIPE接口的计时,必须使用64b (80b) PIPE。对于x16链路,需要有16 * 64b = 1024的超宽的数据路宽。另一个是最小延迟选项。为了减少延迟,时钟可以运行在2GHz,将周期削减到0.5 ns/时钟,时钟必须在2GHz的管道接口关闭,对于x16链路,控制器数据路径为512b。

图9:数据路径和时间考虑 (来源:新思科技)

对于封装来说,64G的封装设计需要新的考虑。因为在同样的奈奎斯特下,从NRZ 转换为 PAM-4,其信噪比更恶劣9.6dB。而且PCle 6.0的封装从TX 到 RX 需要满足- 60db (PCIe 5.0是50dB)到16Ghz的Xtalk Spec。除此之外,还有一些返回损耗和反射、插入损耗,和串扰控制的要求都很高。

首个PCIe 6.0 完整IP解决方案已出

在PCle 5.0方面,新思科技已经拥有超过170个许可的应用。在PCIe 6.0标准下,目前新思科技已推出业界首个PCI Express 6.0完整IP解决方案DesignWare IP ,包括控制器、PHY和验证 IP。可实现PCIe 6.0 SoC设计的早期开发。

DesignWare IP完全支持PCIe 6.0规范,其中包括64GT/s PAM-4信号传输、FLIT模式和L0p功耗状态。新思科技的完整IP解决方案可满足高性能计算、AI和存储SoC在延迟、带宽和功耗效率方面不断提高的要求。

如前文所列出的诸多挑战,新思科技都做了很好的应对。新思科技面向PCIe 6.0的DesignWare PHY IP在5纳米工艺中的高性能PHY采用独特的模拟和DSP技术,可在芯片对芯片、转接卡和背板接口上节省20%的功耗。面向PCIe 6.0的DesignWare PHY IP感知布局架构可最大限度地减少封装串扰,并支持针对x16链路的密集SoC集成。

DesignWare控制器采用了MultiStream架构,可提供相当于Single-Stream设计2倍的性能。该控制器采用1024位架构,可让开发者在1GHz时序收敛的条件下实现64GT/s x 16的带宽。此外,该控制器还可在处理多个数据源以及使用多个虚拟通道时提供最佳流量。

为了通过内置验证计划、序列和功能覆盖来加快测试平台的开发,面向PCIe的VC验证IP采用了本地SystemsVerilog/UVM架构,只需小量的工作即可完成集成、配置和定制。

DesignWare IP的推出将是设计者的一大福音,它能帮助开发者很好的解决从PCIe 5.0过渡到PCIe 6.0的诸多难题,加速其在芯片领域的成功之路。