1nm争霸“暗战”开打

2021-12-16

作者: 畅秋

来源: 半导体行业观察

半导体制程已经进展到了3nm,今年开始试产,明年就将实现量产,之后就将向2nm和1nm进发。相对于2nm,目前的1nm工艺技术完全处于研发探索阶段,还没有落地的技术和产能规划,也正是因为如此,使得1nm技术具有更多的想象和拓展空间,全球的产学研各界都在进行着相关工艺和材料的研究。

上周,IBM和三星公布了一种在芯片上垂直堆叠晶体管的新设计,被称为垂直传输场效应晶体管 (Vertical Transport Field Effect Transistors,VTFET)。当前的处理器和SoC,晶体管平放在硅表面上,然后电流从一侧流向另一侧。相比之下,VTFET彼此垂直,电流垂直流动。该技术有望突破1nm制程工艺瓶颈。

IBM和三星表示,这种设计有两个优点。首先,它可以绕过许多性能限制,将摩尔定律扩展到IBM当前的纳米片技术之外,更重要的是,由于电流更大,该设计减少了能源浪费,他们估计VTFET将使处理器的速度比采用 FinFET 晶体管设计的芯片快两倍或功耗降低 85%。IBM和三星声称,这一工艺技术有望允许手机一次充电使用整整一周。他们表示,它还可以使某些能源密集型任务(包括加密采矿)更加节能,因此对环境的影响较小。

IBM 和三星尚未透露他们计划何时将该工艺技术商业化。他们并不是唯一一家试图突破 1 nm瓶颈的公司。今年5月,台积电与合作伙伴发布了1nm工艺技术路径;7 月,英特尔表示,其目标是在 2024 年之前完成埃级芯片的设计。该公司计划使用其新的“英特尔 20A”制程节点和 RibbonFET 晶体管来实现这一目标。

台积电依然是先锋

近年来,科学界一直在寻找可以替代硅的二维材料,挑战1nm以下的制程工艺,但至今未能解决二维材料的高阻、低电流问题。

近些年,在先进制程的研发和商业化方面,台积电一直是行业先锋。

今年5月,台积电、中国台湾大学(NTU)和麻省理工学院(MIT)联合宣布,1nm芯片研发取得重大突破。

该突破主要体现在材料方面,使用半金属铋(Bi)作为二维(2D)材料的接触电极,可以大大降低电阻并增加电流。这可以实现接近现有半导体尺寸物理限制的能源效率。该消息是在IBM早些时候宣布其2nm芯片之后发布的。

每一种新的工艺技术都会带来新的挑战,在这种情况下,关键挑战是找到合适的晶体管结构和材料。同时,为晶体管供电的晶体管触点对其性能至关重要。半导体工艺技术的进一步小型化增加了接触电阻,从而限制了它们的性能。因此,芯片制造商需要找到一种电阻非常低、可以传输大电流并且可以用于量产的触点材料。

使用半金属铋作为晶体管的接触电极可以大大降低电阻并增加电流。目前,台积电使用钨互连晶体管,而英特尔使用钴互连。两者都有其优点,并且都需要特定的设备和工具。

为了使用半金属铋作为晶体管的接触电极,研究人员不得不使用氦离子束 (HIB) 光刻系统并设计一种“简单的沉积工艺”。这种工艺仅用于研发生产线,因此还没有完全准备好进行大规模生产。

目前,台积电的 1nm 制程节点仍处于探索阶段,工厂正在尝试各种选项,也不能保证未来量产时确定使用半金属铋。

IMEC指向2027

近日,比利时微电子研究中心 (IMEC)表示,1nm制程2027年就可实现商业化,之后的0.7nm 预计将在2029年后实现量产。

IMEC的CEO Luc Van den hove博士在接受采访时强调,搭配全新技术,“摩尔定律要前进多少个世代都不是问题。”据悉,IMEC和ASML合作的EUV设备研发工作正在进行,日本的 TEL也参与其中,预计测试设备有望在2023年初完成,也有企业打算在2026年投入量产。

此外,IMEC还开发了一种新方法,可以在采用1nm制程工艺技术构建的芯片中使用金属互连来减轻焦耳热效应。

IMEC研究人员表示,在对基于铝的二元化合物的实验研究中,重点关注其电阻率,化学计量的AlCu和Al2Cu薄膜的电阻率低至9.5?Ωcm。这些结果在实验上支持它们在先进的半镶嵌互连集成方案中用作新导体的承诺,在这些方案中,它们可以与气隙结合以提高性能。然而,在这种组合中,焦耳热效应变得越来越重要。这是通过在12层后端 (BEOL) 结构中结合实验和建模工作预测的。

1nm制程需要在后端最关键的层中引入新的导体材料,如二元和三元金属间化合物(例如,Al 或 Ru 基),其电阻率低于按比例尺寸的常规元素金属(例如 Cu、Co、Mo 或 Ru)。IMEC已经通过实验研究了铝化物薄膜的电阻率,包括 AlNi、Al 3 Sc、AlCu 和 Al 2 Cu。在20nm 及以上厚度时,所有 PVD 沉积膜的电阻率与 Ru 或 Mo 相当或更低。28nm 的 AlCu 和 Al 2膜的最低电阻率达到 9.5 ?ΩcmCu – 低于 Cu 的值。

IMEC设想在先进的半镶嵌集成方案中引入金属间化合物,包括直接蚀刻可图案化金属以实现更高纵横比的线条。通过在金属线之间逐渐引入部分或全部气隙,可以进一步改善 RC 延迟。用电隔离气隙代替传统的低 k 电介质有望降低按比例尺寸的电容。但是气隙的导热性极差,这引起了对操作条件下焦耳热的担忧。

IMEC通过在局部 2 层金属互连级别执行焦耳热“校准”测量并通过建模将结果投影到 12 层 BEOL 结构,量化了这一挑战。该研究预测,空气间隙会使温度升高 20%。发现金属线的密度起着重要作用:较高的金属密度显示有助于降低焦耳热。

“这些研究结果是改进半镶嵌金属化方案作为1nm制程互连选项的关键,” IMEC研究员兼纳米互连项目总监 Zsolt Tokei 说。“此外,IMEC正在通过其它选项扩展互连路线图,包括混合金属化和新的中间线方案,同时解决与工艺集成和可靠性相关的关键挑战。”

1nm之后将如何发展?

当硅基芯片突破1nm之后,量子隧穿效应大增,将形成“电子失控”,使芯片失效。这种情况下,替换芯片的硅衬底,也许是芯片进一步发展的可行出路之一。

电子可以连续地从一个门流向下一个门,而不是停留在预期的逻辑门内,这在本质上使得晶体管不可能处于关闭状态。

由于晶体管由三个端子组成:源极,漏极和栅极。电流从源极流向漏极,并由栅极控制,栅极根据施加的电压而进行导通或关断电流。

硅和二硫化钼(MoS2)都具有晶格结构,但是通过硅的电子有效质量比二硫化钼小。当栅极长度为5nm或更长时,硅晶体管可以正常工作。

而通过二硫化钼的电子有更高的有效质量,他们的流动可以通过更小的门长度来控制。劳伦斯伯克利国家实验室对此方案的可行性进行了实验验证,但该研究仍处于非常早期的阶段。

一个14nm制程芯片上有超过10亿个晶体管,而伯克利实验室团队还没有开发出一种可行的方法来批量生产新的1nm晶体管,甚至还没有开发出使用这种晶体管的芯片。

但是哪怕仅仅作为概念的证明,这里的结果仍然是非常重要且令人鼓舞的,期待后续新材料的发现可以继续允许更小的晶体管尺寸,并随之提高未来芯片的能效。

中国也有亮点

目前,全球1nm制程工艺都处于研发探索阶段,距离商业化生产还要几年的时间。因此,虽然中国大陆地区的先进制程工艺的商业化水平不高,但在相关的理论研究方面也在跟随国际前沿。例如,湖南大学在1nm制程工艺的研究方面也有亮眼的表现。

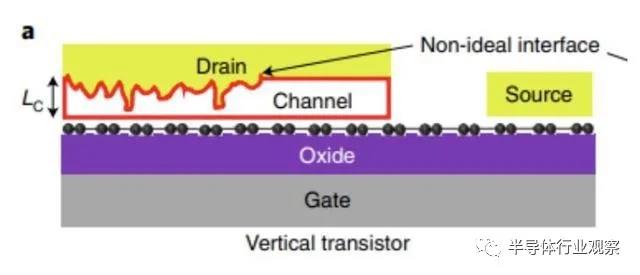

今年6月,湖南大学的研究团队研发出了超短沟道的垂直场效应晶体管(VFET)。这种晶体管技术,可以把晶体管做到3nm大小,而沟道长度只需要0.65nm。在以往的制程工艺中,沟道长度代表的就是芯片制程,也就是说0.65nm的沟道长度,就意味着0.65nm制程。

就是晶体管不是平行排列的,是垂直排列的。这种纵向的结构具有天然的短沟道特性,半导体沟道位于底电极与顶部电极之间,沟道长度仅取决于材料厚度。

更重要的是,这种垂直场效应晶体管不是平行排列的,是垂直排列的。这种纵向的结构具有天然的短沟道特性,半导体沟道位于底电极与顶部电极之间,沟道长度仅取决于材料厚度。

研究人员采用了范德华(vdW)金属电极集成方法,以二硫化钼(MoS2)作为半导体沟道的薄层甚至单原子层,也就是说沟道长度,其实就是一层二硫化钼材料的厚度,所以最短达到了0.65nm。由于排列方式的不同,无需缩短晶体管与晶体管之间的距离,搭积木式的一层一层往上垒就行了,这就使其不完全依赖于高精度光刻机。不过,该研究只是实验室的产物,要真正走向量产,还有很长的路要走。

向1nm光刻机进发

以上谈的都是工艺技术和材料的研发,要实现1nm制程的落地,制造设备,特别是EUV光刻机是必不可少的,这就不得不提到ASML。

目前,ASML的主力出货EUV光刻机分别是NXE:3400B 和3400C,这两款机型的数值孔径(NA)均为0.33,其中更新一款的3400C 的可用性已经达到90% 左右。

ASML预期,到今年年底,NXE:3600D 将会开始进行交付,该设备的匹配套精准度提升了,在30mJ/cm2下的晶圆吞吐量达到160片,相比3400C提高了18%,将会成为未来台积电和三星3nm制程工艺的主要设备。

除此之外,ASML还公布了未来的三代光刻机研发计划,三款机型的型号分别是NEXT、EXE:5000 和EXE:5200。从EXE:5000开始,将数值孔径提高到了0.55。

0.55NA 比0.33NA 有着巨大的提升,包括更高的对比度,图像曝光成本更低等,是未来发展的趋势。

目前,硅片、曝光洁净室已经逼近物理极限,现在的5nm/7nm 光刻机变得十分精密,设备零件多达10万+、体积为40个货柜。据悉,1nm 光刻机体积要比现在3nm 的多出一倍。

由于光刻机拥有非常多的零件,需要高精度的装配,导致光刻机从发货到配置/培训的整个流程需要长达两年时间。按照这个参考推算,预计0.55NA 的大规模应用得2025~2026年了,那时,大概率是1nm制程工艺试产时段。

结语

以上这些只是目前行业内进行1nm制程相关研发工作的代表,并非全部。相信随着3nm的量产,以及2nm进入商业化阶段,1nm制程的研发会逐步成熟,当下的这些实验室级研究,预估将有不少会落地到晶圆厂,同时,还将会有更新的工艺和材料技术诞生。