入门:FPGA之组合逻辑与时序逻辑、同步逻辑与异步逻辑的概念

2022-12-11

来源:CSDN技术社区

逻辑电路" target="_blank">组合逻辑电路与时序逻辑电路

数字电路根据逻辑功能的不同特点,可以分成两大类:一类叫做组合逻辑电路,简称组合电路或组合逻辑;另一类叫做时序逻辑电路,简称时序电路或时序逻辑。

如果数字电路满足任意时刻的输出仅仅取决于该时刻的输入,那么该数字电路为组合逻辑电路。相反,如果数字电路任意时刻的输出不仅取决于当前时刻的输入,而且还取决于数字电路原来的状态,那么该数字电路为时序逻辑电路。例如,下图中只由一个与门组成的电路就是一个组合逻辑电路。

对于上图所示数字电路,无论在任何时刻,并且无论上次A、B输入是什么情况,只要在当前时刻输入端口A、B同时为逻辑1时,输出端C才会输出逻辑1,而其他情况下输出端C都会输出逻辑0。由此可见符合组合逻辑电路的定义。

如果上图中与门的两个输入端分别是来自一个寄存器的输入和输出,如下图所示,那么这就肯定是一个时序电路。

对于上图所示数字电路,假设寄存器中目前保存的值是逻辑1,而此时输入端B没有从逻辑0到逻辑1的跳变(B相当于寄存器的时钟信号),设此时B为逻辑0,那么如果输入端A为逻辑1,则C输出逻辑1;但是如果过了一段时间后,A变为0,且随后B的上升沿到来,那么寄存器中保持的值变为逻辑0,那么在这之后,若令输入端A为逻辑1,B为逻辑0,则由于寄存器中保存着逻辑0值,所以C输出逻辑0。对比前后两种情况,A、B两端的输入都是逻辑1,但是C的输出却不同。由此可见,该数字电路的输出并不完全由输入决定,因此它是一个时序逻辑电路。

对比如上两例我们可以看出,时序逻辑电路和组合逻辑电路并不是完全割裂开来的,而更像是一种包含关系,即时序逻辑电路中肯定有组合逻辑的成分存在,但组合逻辑电路中却不可能有时序逻辑的成分存在。由此可见,只要加以恰当的限制,时序逻辑电路甚至可以完全模拟组合逻辑电路的功能,例如查找表LUT。FPGA中用LUT来实现组合逻辑,但是LUT本身是不包含任何功能的,在FPGA上电或配置的时候对其中的存储载体进行相关设定的赋值,然后LUT由于记住了这个赋值设定,才能模仿各种各样的组合逻辑功能。由于FPGA一般都是基于SRAM工艺的,因此FPGA中的LUT不太可能是基于多路选择器和一系列到电源和地的熔丝组成,如果该查找表是由ROM、RAM或者寄存器等实现的,那么它也是有记忆的,只不过在整个电路工作期间,它不会改变自己的记忆罢了。所以,我们可以认为时序逻辑电路是有记忆的,而组合逻辑电路是无记忆的。有记忆的可以模仿无记忆的,而无记忆的却不能模仿有记忆的。

同步逻辑电路与异步逻辑电路

基于FPGA的设计几乎都是时序逻辑电路,极少会有设计纯组合逻辑电路的情况。记忆性赋予时序逻辑电路更多的功能和更丰富的表达,因此,时序逻辑电路在FPGA的设计中占有非常重要的地位。对于时序逻辑,按信号间关系来看,又可分为同步时序逻辑和异步时序逻辑,简称同步逻辑和异步逻辑。

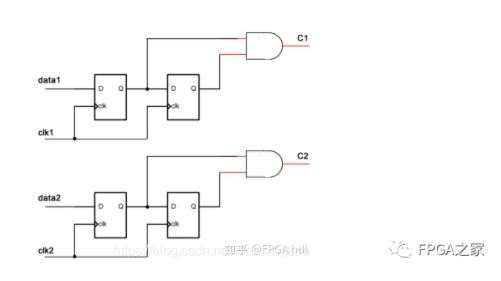

时序逻辑电路中最关键的就是驱动各个记忆元素(例如寄存器、RAM甚至锁存器等)进行记忆动作的时钟信号。通常,我们认为只被一个时钟信号驱动的设计叫做同步时序逻辑。这是因为所有记忆元素都在被同一个时钟信号驱动,那么它们的输出都会同时变化,所以它们对数字电路的影响是同步的。例如下图:

不过这个定义还有些狭隘,广义的同步时序逻辑概念中,允许数字电路中有多个时钟存在,但是这些时钟之间应该有着固定的因果关系,又或者它们所驱动的记忆单元在电路上是完全隔离的。对于第一种情况:如果多个时钟信号之间有固定的因果关系的话,那么即使它们对电路的影响不是完全同时的,但可以根据时钟之间的因果关系推断出这种时间上的固定误差,从而电路状态的变化也是完全可预期的,因此可以认为是同步。例如

如果多个时钟驱动的记忆单元之间完全是隔离的,那么其实它们就是多个同步时序逻辑电路的简单集合体,因此也是同步的。例如:

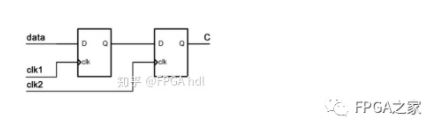

那么从广义同步时序逻辑电路的概念出发,凡是不符合的即属于异步时序逻辑电路。不过这样的定义显得太过偷懒,那么这里总结一下异步时序逻辑的特点,给出异步时序逻辑电路的概念:如果时序逻辑电路存在至少一个这样的组合逻辑功能块——它的输入、输出端口不全来自或导入一个时钟或若干个具有因果关系的时钟所驱动的记忆元素,那么该电路为异步时序逻辑电路。例如,下图组合逻辑(一根连线也是组合逻辑,可看成缓冲门)的输入由clk1时钟驱动的寄存器提供,输出却给了clk2驱动的寄存器。

或下图,与门的输入来自不同的时钟所驱动的寄存器。

或下图,与门的两个输入一个来自时钟驱动的寄存器,一个来自纯组合的输入端口。

对比同步逻辑和异步逻辑的概念,我们可以了解到它们也不是完全割裂开来的,其实也是一种包含关系。即异步逻辑中肯定有同步逻辑的成分在,但是同步逻辑中不可能有异步的成分在。关于异步时序逻辑电路的使用一定要尽量避免,如果不能避免一定要非常的谨慎和小心。

更多信息可以来这里获取==>>电子技术应用-AET<<