为什么UCIe最适合多晶片系统 ?

2023-01-16

作者: 王树一

来源:TechSugar

《道德经》里说“图难于其易,为大于其细。天下难事,必作于易;天下大事必作于细。”其实芯片也是这样,要做大,先做小,这里的从小做起不仅是指器件建模、RTL描述或IP实现,还包括以真正的“芯粒”组合来搭建大芯片。

在当前先进工艺开发的大型SoC中,根据主要功能划分出计算、存储、接口等不同模块,每个模块选择最合适的工艺制造完成后,再通过封装技术组合在一起,已经成为了一种常见选择。这种“硬核拼搭”的乐高积木式开发方法,可以有效化解集成度持续提高带来的风险,例如良率面积限制、开发成本过高等问题,因而逐渐成为行业发展的热点方向。

小芯片之间如何拼接,成为多晶片系统(Multi Die System)设计方法学实现的关键。在多晶片系统(Multi Die System)出现的早期,由于技术新颖,都是各厂商自己摸索,采用自有技术实现不同小芯片之间的连接。但各家都是自研接口技术,不仅重复开发工作繁重,而且也难以真正发挥多晶片系统(Multi Die System)的效力,如果能够将芯粒的接口技术标准化,则不仅可以加速推广多晶片系统(Multi Die System)技术,减少重复开发工作量,也可以打破厂商界限,将不同供应商的芯粒组合在一起,从而进一步提高资源利用率和开发效率,最终围绕芯粒建立一个大型的生态系统。

正当其时的UCIe

近年来,已有不同的行业组织提出了适用于多晶片系统的芯粒间(Die-to-Die)互连技术规格,而通用芯粒互连标准UCIe(Universal Chiplet Interconnect Express)在2022年3月发布,作为较晚出现的技术标准,UCIe不仅获得了半导体生态链上各主要厂商的支持,也是到目前为止,技术规范定义最完整的一个标准。

从UCIe联盟公布的白皮书来看,UCIe 1.0标准支持即插即用,在协议层支持PCIe或CXL等成熟技术,也支持用户自定义的流式传输,兼具普适性与灵活性;在协议上,UCIe定义了完整的芯粒间互连堆栈,确保了支持UCIe技术的芯粒相互之间的互操作性,这是实现多裸片系统的前提条件;虽然是为芯粒技术定制,但UCIe既支持封装内集成,也支持封装间互连,可用于数据中心等大型系统设备间的互连组装;对封装内互连,UCIe既支持成本优先的普通封装,也支持能效或性能优先的立体封装。总而言之,得到了半导体及应用领域各环节核心厂商支持的UCIe,具备了成为普适技术的基础。

UCIe规范概述

UCIe是一个三层协议。物理层负责电信号、时钟、链路协商、边带等,芯粒适配器(Die-to-Die Adpater)层为提供链路状态管理和参数控制,它可选地通过循环冗余校验 (CRC) 和重试机制保证数据的可靠传输,UCIe接口通过这两层与标准互连协议层相连。

其中,物理层是最底层,这一层是封装介质的电气接口。它包括电气模拟前端AFE、发射器、接收器以及边带信道,可实现两个裸片间的参数交换和协商。该层还具备逻辑PHY,可实现链路初始化、训练和校准算法,以及通道的测试和修复功能。

芯粒适配器层负责链路管理功能以及协议仲裁和协商。它包括基于循环冗余校验 CRC 和重试机制,以及可选的纠错功能。

协议层可支持对一个或多个 UCIe 支持协议的实现。这些协议基于流控单元(Flit),用户可根据需要选择PCIe/CXL协议,也可以根据应用自定义流式传输协议。优化的协议层可为用户提供更高的效率和更低的延迟。

能否统一封装内互连技术?

芯粒间接口技术标准化,既可以为众厂商提供技术发展路线图做参考,又可以让不同厂商生产的符合标准的芯粒自由组合,打破良率尺寸限制,建立起基于先进封装技术的SoC开发新生态。

在当前已有的协议中,UCIe在协议完整性、支持厂商等方面都具有优势,也具备进一步的发展空间,例如支持更高的数据速率和3D封装等,只不过由于UCIe技术相对较新,要成功推广,还需要产业链上核心厂商在IP、工具和制造等方面提供足够的支持。

例如,新思科技就已经推出了完整的UCIe设计解决方案,包括PHY、控制器和验证IP(VIP):

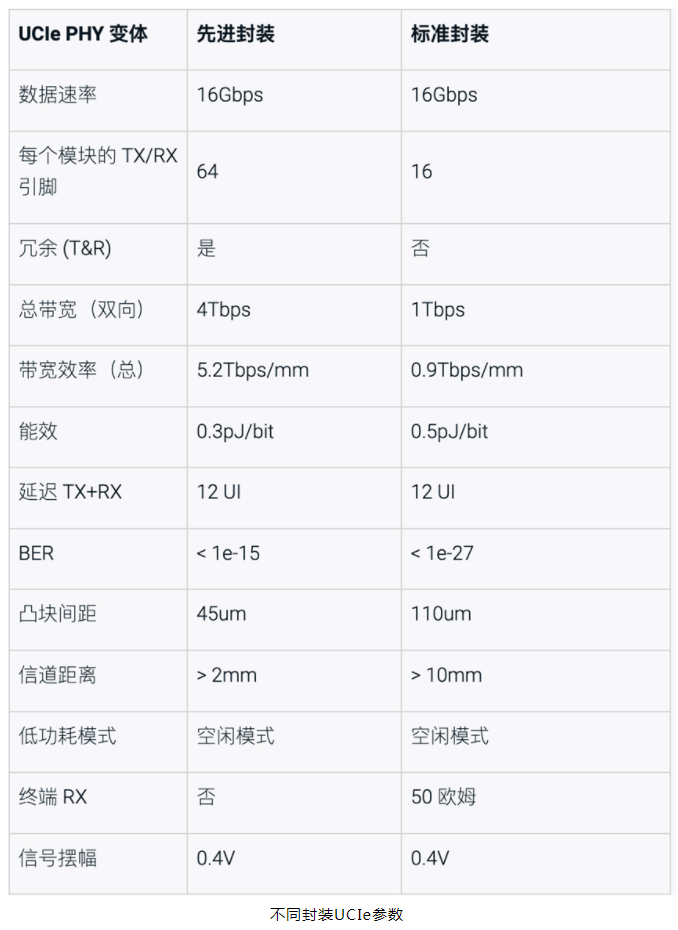

PHY──支持标准和高级封装选项,可采用先进的FinFET工艺,获得高带宽、低功耗和低延迟的裸片间连接。

控制器IP──支持PCIe、CXL和其它广泛应用的协议,用于延迟优化的片上网络(NoC)间连接及流协议;例如与CXS接口和AXI接口的桥接。

VIP──支持全栈各层的待测设计(DUT);包括带有/不带有PCIe/CXL协议栈的测试平台接口、用于边带服务请求的应用编程接口(API),以及用于流量生成的API。协议检查和功能覆盖位于每个堆栈层和信令接口,实现了可扩展的架构和新思科技定义的互操作性测试套件。

新思科技的解决方案不仅带来了稳健、可靠的芯粒间连接,并具有可测试性功能,可用于已知良好的裸片,和用于纠错的CRC或奇偶校验。它将使芯片设计企业能够在芯粒间建立无缝互连,实现最低的延迟和最高的能效。

从UCIe的命名来看,UCIe联盟颇有将UCIe技术发展成PCIe或者USB的雄心,而历史经验表明,只要技术标准足够开放互利,再有成熟的产业链支撑,就有机会统一市场。

更多信息可以来这里获取==>>电子技术应用-AET<<