铜柱倒装封装技术面临怎样的清洗挑战?

2023-11-30

来源:ZESTRON

当Bump(凸点)与Bump之间的间距小于150个微米时,使用锡球连接晶片与基板的工艺方式明显遇到瓶颈,这时,具有优秀散热能力的铜柱工艺在众多可行性中脱颖而出,不仅拥有卓越的电迁移性能,更高的I/O密度,而且相比金,在成本上有不可比拟的优势。

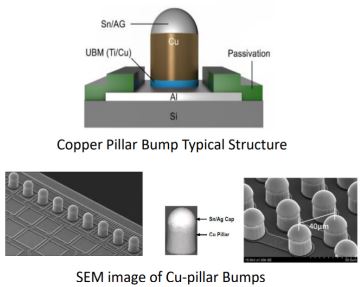

图1是典型的铜柱结构示意图。如图所示,最底部灰色的硅基板上是铝焊盘,周围绿色的是高分子钝化层,起到绝缘的作用。蓝色是由铜和钛组撑的合金,铜柱最顶层是锡银合金的锡帽。由于铜柱工艺是依靠沉积形成,所以这些凸块可以有各种形状,大小的差异,铜柱的高度大于直径也是可行的,工艺上的可调整性表现非常优秀。同引线键合封装相比,铜柱凸块技术提高了芯片到基板的散热性,更短的信号传输路径会使信号较少失真。尤其是高产量时,铜柱凸块工艺要比引线键合工艺更具经济性。因此,综合多种因素考虑,铜柱凸块技术在逐步成为倒装芯片最主要的连接方式。

图1:SEM下铜柱影像

倒装芯片使用的助焊剂大部分都用到水溶性助焊剂,一般客户首选的清洗方案是去离子水。由于水本身的物理性质,这种清洗方式虽然省时省力,却在小于50微米或bump间距紧密的产品上显露出很大的局限性。在小间隙条件下,去离子水只洗掉了最外层表面的助焊剂残留。无法充分进入芯片底部,也无法提供持续的机械力来清洗小间隙下半封闭结构中的助焊剂残留。

ZESTRON也曾对铜柱倒装芯片的清洗开展过对比研究,希望发现分别应用去离子水和专门设计的清洗剂进行清洁有何不同。实验完成后,ZESTRON采用包括IC离子色谱,SEM/EDS扫描电镜元素分析,FTIR傅里叶红外变换光谱分析的多种分析手段获得精确的对比数据,随即又采用TC高低温循环测试,HTSL高温工作环境寿命测试,以及MSL湿敏气密性测试开展了可靠性验证。实验表明:清洗剂在低浓度(5%)下完全能够去除无铅水溶性助焊剂残留物,相比去离子水配合较慢的链速(2.0fpm),即便使用更快的链速(3.0fpm)也能达到更优秀的清洗结果。如图2所示。

图2:3.0fpm链速下SEM分别应用 DI水(左)和清洗剂(右)的分析结果

铜柱工艺是TSV硅穿孔技术的基础工艺。随着芯片制造技术的发展,芯片密度越来越高,芯片之间的间距不断减小,芯片互联的可靠性要求也更严苛。ZESTRON专门研发用于去除各种封装类产品的水溶性助焊剂,如倒装芯片,包括2.5D/3D TSV堆叠、BGA和SiP等,同时能为底部填充、引线键合和注塑成型等后道工艺提供绝佳的表面条件。特别是应对TSV封装面临的封装密度和底部间隙上的挑战。

更多精彩内容欢迎点击==>>电子技术应用-AET<<