基于TMS320C6701的扩频通信抗窄带干扰自适应滤波器实现

2008-07-17

作者:王海江 1,2, 谢明元1,

摘 要: 扩频" title="扩频">扩频通信体制在现代通信中的应用越来越广泛。由于扩频码的伪随机性和优良的相关特性,这种体制本身就具有一定的抗干扰性能。但扩频信号的带宽宽,容易受到空间电磁信号和人为发射的恶意信号干扰,干扰信号较强时,需要采取抗干扰措施。针对扩频通信中的窄带干扰" title="窄带干扰">窄带干扰,提出了一种基于TMS320C6701的抗干扰自适应滤波器" title="自适应滤波器">自适应滤波器的实现方案,并在其EVM板上进行了实验,取得了较好的抗干扰效果。

关键词: 扩频 窄带干扰 自适应滤波器

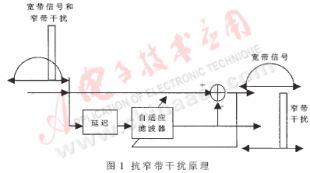

扩频通信中的窄带干扰可以通过时域自适应滤波和频域门限滤波的方式进行抑制。所谓窄带干扰是指干扰的带宽远远窄于信号带宽。由于干扰信号的前后相关性很大,而有用信号的前后相关性很小,因此可以对干扰信号进行自适应跟踪估计,然后从接收信号中减去,这就是自适应陷波技术。自适应陷波技术原理如图1所示。

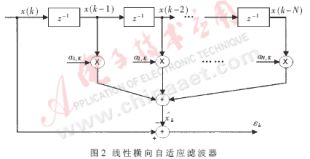

其中自适应滤波部分如图2所示,称为线性横向自适应滤波器[1~2]。其滤波及系数更新过程如下:

其中, μ为收敛步长因子。上面使用的收敛算法称为LMS算法。如果信号是平稳的,则均方误差" title="均方误差">均方误差将朝着均方误差曲面的底部(最小均方误差)方向移动,直到曲面“碗底”。但前面已经说过,信号平稳的假设在现实情况中很难成立,均方误差曲面处在不断变动中,因此最小均方误差只是一种趋势。

1 抗窄带干扰自适应滤波器的实现

抗干扰算法比较适合用DSP实现,考虑到其运算复杂度,笔者选定了TI公司的TMS320C6701作为其实现器件。根据接收信号的仿真处理流程提出了一个硬件设计基本框图,其基本结构如图3所示。

其中,固定频率下变频模块的作用是为了降低采样后的信号速率,从而减小后面DSP芯片的运算量。

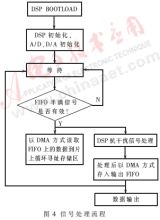

为了减少DSP的资源消耗,DSP并不是直接逐个读取A/D" title="A/D">A/D采样后的数据,而是在中间加了一块FIFO,当FIFO半满后通知DSP,DSP通过DMA方式读入数据,进行处理。DSP处理后的数据先放在片内存储器中,达到一定数量后以DMA方式输出到FIFO中,后面一块FIFO可与最后面的解调解扩模块一块起到速率调节的作用。信号处理流程如图4所示。

1.1 A/D 的选择

A/D变换芯片与系统的抗干扰性能紧密相关。芯片的采样速度决定了干扰抑制算法的误差收敛速度和最小误差的浮动范围(有信噪比的损失),以及以后的解扩、解调的可实施性。芯片的采样位数决定了干扰抑制的程度和信噪比损失的大小(量化噪声)。在抗干扰系统中,在最大的干信比为20dB~45dB、有用信号的量化精度为4位的情况下,可以算出并行A/D变换的采样位数,具体计算如下:

其中, [a]为大于a的最小整数。

一般情况下,接收信号的采样速率为码片传输速率4~8倍。在基于CDMA的卫星通信系统中,一般采用与IS-95相同的码片传输速率(典型速率为1.2288Mchip/s)。选取采样数率为数据速率的4倍,则A/D采样的最小采样速率为:

S=[1.2288×4]+1=6Mchip/s (5)

根据以上理论分析并查阅相关的芯片资料可知,采用TI公司的THS1215可以完成该项工作。THS1215的具体参数如下:

电源电压:3.3V

转换位数:12位

转换数率:15Mbps

适用温度范围:

0℃~70℃(THS1215CPW THS1215CDW)

-40℃~85℃(THS1215IPW THS12150IDW)

A/D与DSP之间以FIFO连接。由于FIFO芯片有输入输出两个时钟,只要输入输出不同时读写同一个缓存单元,就不会出现时钟冲突。因此,这种设计方式可以忽略DSP与A/D的时钟不一致的影响。更进一步,FIFO可以缓存比较多的数据,DSP可以采用突发读写的方式,通过中断或DMA方式一次读入多个数据,这样可以提高数据传输的速率。

1.2 基于CCS的滤波算法程序

为了便于实现FIR滤波,笔者采用循环寻址的方式,在程序开始时就要设定寻址方式。寻址方式要在寻址方式寄存器中设置。有8个寄存器(A4~A7,B4~B7)可以执行线性或循环寻址。在循环寻址寄存器里,有2bit域用来设置寻址方式(线性或循环,其中线性是默认的寻址方式)。在循环寻址模式下,有一个BK域规定循环寻址区的大小。

设定循环寻址的区域后,FIFO中的数据半满后即可以循环寻址的方式存入该区域,进行FIR滤波时DSP也以循环寻址的方式从这个区域取源数据。A/D采样位数为十二位,因此,存取的数据按半字即可。

假设数据循环寻址缓冲区地址指针寄存器为A4,系数存储区地址指针为B4,为了节省DSP资源,加快执行速度,可以用LDW命令一次读两个数据到一个32位的寄存器里。程序如下:

(1)FIR滤波

LOOP: LDW .D1 *A4++[1], A6

LDW .D2 *B4++[1], B6

SUB .S1 A1, 1, A1

[A1] B .S2 LOOP

MPY .M1X A6, B6, A14

MPYH .M2X A6, B6, B14

ADD .L1 A14, A15, A15

ADD .L2 B14, B15, B15

ADD .L1X A15, B15, A8

(2)系数更新

LOOP: LDW .D1 *A4++[1], A6

SUB .S1 A2, 1, A2

[A2] B S2 LOOP

MPY .M1X A6, A12, A14

MPYH .M2X A6, B12, B14

STH .D2 A14 , *B4++

STH .D2 B14 , *B4++[2]

2 抗干扰性能

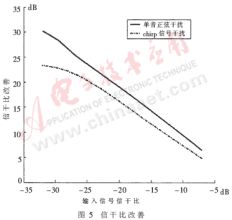

笔者在TMS320C6701的EVM板上进行了实验,采用Gold序列扩频后的BPSK信号,信息速率为2.4kbps,扩频码长度为511。在扩频信号中加单音正弦波干扰和chirp信号干扰,滤波器对这两种干扰抑制后的信干比改善如图5所示。可以看出,在不同的输入信干比条件下,滤波后信干比都有较大改善。抗干扰前后信号的频谱如图6所示,可以看出,原来叠加在有用信号中的窄带干扰已经被抑制掉。

本项目由成都信息工程学院科研基金资助,项目号为CRF200526。

参考文献

1 Leslie A. Rusch, H.Vincent Poor. Narrowband Interference Suppression in CDMA Spread Spectrum Communications. IEEE Transactions on Communications,1994;42(2/3/4):1969~1979

2 H.Vincent Poor, Leslie A.Rusch. Narrowband Interference Suppression in Spread Spectrum CDMA.IEEE Personal Com-munications Magzine,3rd Quate 1994:14~27

3 TMS320C6000 CPU and Instruction Set Reference Guide. Texas Instruments. October,2000

4 Simon Haykin.自适应滤波器原理.北京:电子工业出版社,2003