摘 要: 介绍一种基于CPLD" title="CPLD">CPLD的多普勒声纳" title="多普勒声纳">多普勒声纳回波信号仿真卡的设计实现,该板卡作为PXI测试系统的一个组成模块,数据交换基于PXI总线" title="PXI总线">PXI总线,使用S5920" title="S5920">S5920实现总线控制,利用CPLD实现板卡的时序逻辑控制,外围电路包括信号调理与匹配电路、DDS电路、A/D采集电路、高速FIFO" title="FIFO">FIFO存储电路、D/A转换电路等。重点介绍了CPLD内部功能模块的实现。该设计已成功应用于多普勒声纳的PXI测试系统中。

关键词: 多普勒声纳;PXI总线;S5920;CPLD;FIFO

水下航行器可利用声波信号的多普勒效应进行导航,多普勒声纳按一定的角度向海底发射声波,利用回波信号的多普勒频移测得航行器相对于海底的速度,然后通过对地速的积分结合航向信息就可以获得导航解[1]。在水下航行器的研制、生产、实验、验收等环节中,经常需要对导航声纳的性能参数进行测试,若进行实物的水下航行实验,不仅会花费大量的人力、物力和财力,而且实时参数的获取也有一定的困难。本文提出一种利用模块化的PXI总线测试平台对水下航行器导航系统进行测试的解决方案,使得对导航系统的测试可以在陆上实验室完成。测试平台大部分由成熟的通用测试模块构成,其中对回波信号多普勒效应的模拟是整个系统设计的关键环节,本文通过设计专门的多普勒声纳回波信号仿真卡实现[2]。

1 仿真卡的组成与工作原理

1.1 仿真卡组成

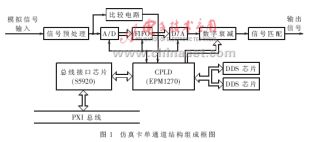

仿真卡主要由总线接口芯片、CPLD、门限比较电路、DDS(直接数字频率合成)电路、A/D采集电路、FIFO存储电路、D/A 转换电路以及输入输出端的信号调理与匹配电路等组成。导航系统包括4个安装在航行器底部的多普勒声纳,因此仿真卡有4个相对独立的工作通道,分别模拟多普勒声纳4个不同方向的回波信号,其中一个通道的结构组成如图1所示。

1.2 工作原理

总线接口芯片S5920实现仿真卡与PXI测试系统的桥接,可简化接口部分的设计。CPLD实现仿真卡的总体时序逻辑控制。对接换能器输出的模拟信号在板卡上经信号预处理电路后分为两路,一路信号送A/D采集电路,另一路信号进入门限比较电路。当多普勒声纳发射信号时,对接换能器对应有模拟信号输出,门限比较电路会产生一个触发信号送CPLD,CPLD启动仿真卡的数据采集过程。数据采集与回波信号模拟的时序逻辑如图2所示,t1为发射信号周期,T为发射脉冲宽度,采集数据同时存入4路FIFO存储器,经过t2时间的延迟后由CPLD控制读取4路FIFO中的数据并进行D/A转换,然后经数字衰减电路和信号匹配电路后由对接换能器发射出去。若声速为c,则该回波信号模拟的是传播距离为m=ct2/2的回波信号,T′为回波信号的脉冲宽度。

DDS芯片产生A/D采集芯片、FIFO芯片以及D/A转换芯片的工作时钟,CPLD通过程控DDS产生不同的工作时钟信号,使得D/A转换时钟不同于A/D采集时钟,从而实现采集数据在时间上的拉伸与压缩,模拟回波信号的多普勒效应。真实回波信号在信道中传输后会有不同程度的衰减,因此D/A转换后的数据需经数字衰减电路进行程控衰减。信号预处理电路和信号匹配电路的核心都是一级射随电路。板卡上共有5片DDS,产生5路时钟信号,DDS0时钟作为A/D采集时A/D芯片和FIFO芯片的工作时钟,另4路时钟DDS1~DDS4作为D/A转换时FIFO芯片和D/A芯片的工作时钟,DDS芯片和数字衰减器需经CPLD配置参数才能正常运行。

2 主要功能模块硬件设计

功能仿真卡硬件设计要满足以下指标:

(1)板卡作为PXI测试系统的一个模块,与PXI主机的数据交换基于PXI总线;

(2)系统运行的逻辑控制和部分芯片的配置功能由CPLD[3]完成;

(3)板卡数据采集系统的时钟由程控的DDS产生,数据采集频率10MHz~40MHz;

(4)采集数据的存储采用高速大容量的FIFO存储器实现,存储深度为1MB;

(5)A/D采集和D/A转换采用8bit芯片,工作频率≥40MHz[4]。

PXI总线是在PCI局部总线的基础上增加了用于多板同步的触发总线和参考时钟而成的,PXI是PCI总线的一种扩展总线,因此完全兼容PCI总线的规范协议。利用成熟的PCI模块,通过软件兼容性设计与修改,就可以完成PXI系统的设计与开发。由于PCI总线协议的逻辑时序比较复杂,这里采用PCI总线接口芯片S5920来实现接口功能[5]。S5920内部配置寄存器的定义信息存储在外接的EEPROM芯片AT24C02中,系统上电时由操作系统的配置软件读取。

CPLD是整个仿真卡的主控模块,根据S5920提供的控制信息,控制实现各部分电路的时序逻辑功能。CPLD采用Altera公司MAX II系列的EPM1270芯片。MAX II CPLD采用类似于FPGA的全新架构,与传统的CPLD相比,可以提供给用户更多的逻辑资源,更多的用户I/O,同时具有更低的功耗。

DDS采用AD公司的AD9850芯片。AD9850内部包含高性能的D/A转换器和高速比较器,通过设置32bit的频率控制字,可产生0~40MHz的稳定方波信号。射随电路采用低噪声、高精度运算放大器OP37。门限比较电路采用低偏置电压的四路比较器LM339,参考电压由外部基准源ADR510提供。AD采集部分由宽频带电流反馈运放OPA681和8bit精度A/D转换芯片ADS831组成,ADS831采用内置参考电压,单极性输入信号,输入电压信号范围为1.5V~3.5V。FIFO存储器采用IDT公司512KB的IDT72V2113,为实现1MB的存储深度,IDT72V2113设置成512K×9bit工作方式,并采用两片进行级联。AD9709和高速运放AD843构成D/A转换电路,AD9709是一种双通道8位D/A转换器,因此4个转换通道只需要两片AD9709。程控衰减电路采用AD7111N和OP37构成的典型应用电路,通过锁存一个字节的配置数据,AD7111N可以实现0~88.5dB的程控衰减,衰减步长为0.375dB。

3 CPLD功能实现

CPLD模块的设计是整个仿真卡的核心,其要实现的功能包括:(1)接口功能。能够实现CPLD与PCI桥芯片S5920的数据通信,并锁存所预设的参数;(2)根据主机设定的参数,正确配置5片DDS和4片数字衰减器;(3)初始化各外围芯片,运行过程中控制其运行状态,必要时可重新复位;(4)根据外部触发信号启动A/D采集,并按照预设参数值适时启动D/A转换过程。

CPLD的开发工具采用Altera公司提供的集成开发工具Quartus II 5.1[6]。设计方法采用VHDL和原理图的混合设计。CPLD控制器的内部功能实现较为复杂,模块之间的逻辑联系较多,下面仅以接口功能模块、配置模块和逻辑控制模块三个主要部分来介绍CPLD的内部功能实现。

3.1 接口功能模块

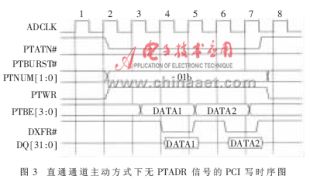

接口模块的功能主要是使CPLD能够正确接收主机的控制和数据信息,并对数据进行锁存。S5920将PCI总线信号转换成相对简单的外加总线(ADD_ON_BUS)信号,根据S5920的不同数据传输方式,外加总线信号也分为直通通道引脚和邮箱通道引脚两大类。这里采用直通通道传输方式,图3为直通通道主动操作方式下不使用PTADR#信号的PCI写时序图。PTATN信号低电平有效表示一个PCI总线周期正在进行;PTBURST信号无效表示未用猝发传送方式,而是单周期方式;PTNUM是直通通道的通道号;PTWR信号有效表示是进行写操作;PTBE是直通通道的字节允许标志,指示32位双字中的哪个字节有效;DXFR为主动方式传送完毕信号,其为低电平时表示有数据正在传送,因此接口模块是在DXFR低电平的时钟上跳沿时锁存数据。

数据传送采用16位总线方式,低8位是数据,高8位是地址信息,接口模块在接收到16位信息后直接对地址译码后将数据锁存入存储区中的相应地址。这些数据信息包括系统的运行参数、DDS与数字衰减器的配置数据以及主机控制板卡工作状态的控制信息。同时接口模块还要提供外加总线的时钟信号ADCLK作为S5920的工作时钟。

3.2 配置模块

系统在启动或复位后,需要对DDS和数字衰减器进行配置,配置数据由主机写入接口模块进行锁存。由于DDS与数字衰减器的配置过程类似,这里以相对复杂的DDS配置过程为例说明相应功能的CPLD实现。

AD9850的配置可采用并行或串行配置方式,这里采用并行方式,配置时序如图4所示。40bit的配置数据分成5个字节,第一个字节是相位调制和电源功能信息,后4个字节是频率控制字。配置前先由RESET信号对芯片复位,5个字节的配置数据在W_CLK的上升沿写入AD9850,FQ_UD是配置结束信号,AD9850在FQ_UD的上跳沿刷新输出频率。

CPLD内部的DDS配置模块的顶层原理图文件如图5所示。主要包括一个配置逻辑产生模块dds_cfg、6bit计数器lpm_counter0和一个T触发器lpm_tff1。5片DDS共用一个dds_reset信号,图中6位计数器lpm_count0作为地址发生器,dds_cfg模块根据不同的地址信息读取配置数据并产生如图5所示的配置逻辑信号。计数器使能的有效信号由预设参数结束后的启动信号begin产生,配置完成后的cnt_clken信号使计数器使能信号变低,使整个配置模块停止工作,从而完成配置过程。

3.3 逻辑控制模块

CPLD的控制功能主要由逻辑控制模块实现,控制模块的主要功能示意图如图6。4片FIFO的读空信号(FIFO_OR)取逻辑与后经脉冲同步产生一个脉冲复位信号,这里取与的目的是取最后读空的FIFO读空标志,同时主机的控制信号经或门也可以对系统进行复位。这样每个工作周期系统便自动复位,而主机也可以随时对仿真卡进行复位。外部触发信号与主机的控制信号取与后作为计数器的时钟使能信号。比较器将计数器的计数值与上位机的预设参数相比较,当计数到预设值后产生相应的控制信号送时钟控制模块。时钟控制模块主要是根据计数比较结果、FIFO读空信号以及外部触发信号控制A/D、D/A和FIFO芯片的工作时钟,以控制各外围电路的工作,同时时钟控制模块还对DDS产生的时钟信号进行必要的整形或反相,以满足外围电路正常工作的时序要求。

4 CPLD内部设计仿真与板卡调试

CPLD内部设计的功能仿真和时序仿真都通过Quartus II集成的仿真工具进行。由于时序仿真包含了布局布线后的延时信息,能够真实地反映芯片的工作情况。时序仿真前,需要编辑完整的测试激励文件,设置正确的时序约束参数,如设置具有一定裕量的时钟周期、时钟建立时间、时钟保持时间等,剪除非相关时钟域中的时序路径,并将内部非时钟路径的T触发器输入端管脚设置为非时钟等。最终时序仿真的结果完全能够满足设计的功能要求与时序要求。

由于在Windows XP系统中应用程序无法直接对硬件端口进行操作,因此需要编写专用的驱动程序。这里采用目前应用广泛的WinDriver开发工具,利用它的向导工具,不需要深入了解操作系统的整个内核体系结构,就可以开发出高质量的驱动程序,应用程序采用Visual C++开发。将仿真卡在整个PXI测试系统中进行调试,发现该板卡能够完全满足最初的设计要求,且运行稳定可靠。

基于CPLD多普勒声纳回波信号仿真卡的研制,满足了设计指标要求,特别是CPLD的应用使得整个板卡具有结构简单、成本低、可靠性高等优点。该仿真卡现在已成功应用于对某水下航行器多普勒导航声纳进行陆上检测的PXI测试系统中,并取得了良好的效果。

参考文献

[1] 李俊,沈安文.基于多普勒速度声纳的水下航行器导航方法[J].华中科技大学学报,2004,(1):73-75.

[2] 谢志刚,陈自力.PXI总线数字输入/输出模块的设计与实现[J].电子技术应用,2005,(2):67-69.

[3] MAX II Device Handbook Data Sheet.2004,4.

[4] 王立欣,刘双宝.基于PCI总线的100MSps,256MBit数据采集系统[J].哈尔滨工业大学学报,2005,(2):246-248.

[5] AMCC S5920 32-Bit PCI Bus Target Interface Data Sheet.1998,10.

[6] 王诚,吴继华.Altera FPGA/CPLD设计(基础篇、高级篇)[M].北京:人民邮电出版社,2005.