同步数字复接的设计及其FPGA实现

2008-09-12

作者:王 志1, 石江宏2, 周剑扬2

摘 要: 在简要介绍同步数字复接" title="复接">复接基本原理的基础上,采用VHDL语言对同步数字复接各组成模块进行了设计,并在ISE集成环境下进行了设计描述、综合、布局布线及时序仿真,取得了正确的设计结果,同时利用中小容量的FPGA实现了同步数字复接功能。

关键词: 同步数字复接/分接 FPGA 位同步" title="位同步">位同步 帧同步" title="帧同步">帧同步检测

基群速率数字信号的合成设备和分接设备是电信网络中使用较多的关键设备,在数字程控交换机的用户模块、小灵通基站控制器和集团电话中都需要使用这种同步数字复接设备。近年来,随着需要自建内部通信系统的公司和企业不断增多,同步数字复接设备的使用需求也在增加。FPGA(现场可编程门阵列)器件的高性能简化了数字通信系统的设计与实现。本文基于FPGA的技术特点,结合数字复接技术的基本原理,实现了基群速率(2048kbps)数字信号的数字分接与复接。

1 同步数字复接的基本原理

在数字通信网中,为了扩大传输容量和传输效率,常常需要把若干个低速数字信号合并成为一个高速数字信号,然后通过高速信道传输;而在接收端又按照需要分解成低速数字信号。数字复接技术就是实现这种数字信号合并(复接)和分解(分接)的专门技术[1]。

1.1 系统划分

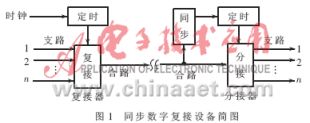

同步数字复接终端包括同步数字复接器" title="复接器">复接器(Synchronous Digital Multiplexer)和同步数字分接器" title="分接器">分接器(Synchronous Digital Demultiplexer)两部分,如图1所示。数字复接器把两个或两个以上的支路数字信号按时分复用方式合并成单一的合路数字信号;数字分接器把单一的合路数字信号分解为原来的各支路数字信号。通常总是把数字复接器和数字分接器装在一起做成一个设备,称为复接分接器(Muldex),一般简称数字复接设备[2]。

同步数字复接器由定时和复接单元组成;而同步数字分接器则由同步、定时和分接单元组成。定时单元给设备提供各种定时信号,复接器的主时钟可由内部产生,也可由外部提供,而分接器主时钟则从接收信号中提取,并通过同步电路的调整控制,使得分接器基准时序信号与复接器基准时序信号保持正确的相位关系,即收发同步。同步的建立由同步单元实现[1]。

1.2 位同步[3]

在数字通信中,位同步是最基本的同步。位同步的基本含义就是收端和发端时钟信号必须同频同相,这样接收端才能正确接收和判决发送端送来的每一个码元。为了达到收发端时钟同频同相,接收端需要从收到的码流中提取发送端的时钟信号来控制接收端时钟,从而做到位同步。实现位同步的方法分为插入导频法和直接法两类。而直接法按照提取同步信号的方式,大致又可分为滤波法和锁相法。锁相法的原理是:在接收端用鉴相器比较接收码元和本地产生的位同步信号的相位,如果两者不一致,则用鉴相器输出误差信号去控制本地同步信号的相位,直至本地的位同步信号的相位与接收信号的相位一致为止。

1.3 帧同步

在复接分接器中,如果只是循环交织地复接各支路数字信号,那么一旦合并成为一个合路数字信号后就难以正确地实施分接。为了保证接收端分路系统能和发送端一致,在保持位同步的基础上还必须要有一个帧同步系统,以实现发送端与接收端的帧同步[2]。

实现帧同步的基本方法是在发送端预先规定的时隙(即帧同步码时隙)插入一组特殊码型的帧同步码组;在接收端由帧同步检测电路检测该码组以保证收发帧同步[2]。

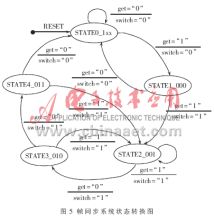

帧同步检测状态有失步态、同步校核态、同步态和同步保护态四种状态。

2 基于FPGA的同步数字复接的设计与实现

FPGA/CPLD既继承了ASIC的大规模、高集成度、高可靠性的优点,又克服了普通ASIC设计的设计周期长、投资大、灵活性差的缺点,逐步成为复杂数字电路设计的理想首选[4]。

ISE是XILINX公司提供的一个开发FPGA/CPLD的集成环境,其集成的工具可以完成从设计输入、功能仿真、综合优化、综合后仿真、布局布线、时序仿真到配置芯片等整个FPGA/CPLD开发过程。

本设计采用ISE集成环境进行开发,使用SPARTAN-3系列FPGA器件实现设计。

2.1 按码字复接系统的设计

数字信号复接主要有两种方式[1]:一种是“逐位复接”,另一种是“按码字复接”。其中按码字复接方式保留了码字结构,有利于多路合成处理和交换。本设计要实现32路信号的复接,信息位采取各支路彼此循环且每次插入一个8位信息位到合路数字信号中的码字复接形式,帧同步码采用CCITT推荐的10011011。

2.1.1 复接器和分接器的设计

复接器应完成两个功能。一是循环接收32个64kbps的支路信号,每支路每次送入8位信息位(其中第一支路送入固定的帧同步码10011011),形成合路数据;二是将合路数据以2048kbps的速率发送出去,形成合路信号——基群速率信号。

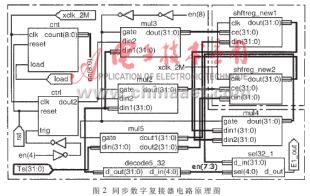

同步数字复接器电路原理图如图2所示,复接器由移位寄存器和定时模块两部分构成。移位寄存器分两组,每组由32个8位移位寄存器组成。在一帧时间(125μs)内,当其中一组移位寄存器在64kHz时钟控制下同时移入32个支路的数据时,另一组移位寄存器在2048kHz时钟(xclk_2M)的控制下将上次存入的32个支路的数据依次送出。在下一帧时间内,则由第一组移位寄存器输出2048kbps的合路信号,第二组移位寄存器读入32个64kbps的支路数据。依此规律,在定时模块的控制下,由两组移位寄存器交替变换工作任务,实现了支路输入和合路输出的连续性。定时模块由计数器(cnt)、多路选择器(mul2~mul5)等组成,为两组移位寄存器提供工作允许信号、合路信号输出的切换选择信号。

为了提高时钟的可靠性、降低时钟的延时抖动、提高时钟的驱动能力,从而更好地完成同步复接,利用FPGA自身提供的全局时钟资源驱动本设计的主时钟,将外部时钟从芯片的全局时钟管脚输入,经过BUFGP(IBUFG+BUFG)后通过全局时钟网络送至同步复接部分。

分接器的功能与复接器相反。分接器在其定时单元的控制下,对两组移位寄存器进行2048kbps的数据写入和64kbps的数据读出,实现基群速率合路数字信号的32路分接。

2.1.2 位同步提取电路的设计

实现合路数字信号的分接,需要从数据流中提取时钟同步信息。目前,在数字通信系统中,常常采用数字锁相法提取位同步信号[3]。

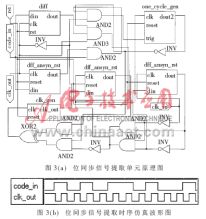

位同步提取电路如图3(a)所示,主要由微分与鉴相模块、添门/扣门控制模块、高频时钟模块以及分频器(clk_gen)等部分组成。微分电路(diff)的功能是把非归零码转换为归零码,以利于定时信息的提取。鉴相器的功能是比较接收码元(code_in)与分频器输出的本地时钟信号(clk_out)的相位,若本地时钟超前于接收码元的相位,鉴相器向扣门电路输出一个超前脉冲,在16分频器输入端扣除一个高频窄脉冲,使分频器输出的时钟信号的相位滞后1/16周期;若本地时钟滞后于接收码元的相位,鉴相器向添门电路输出一个滞后脉冲,增加一个高频窄脉冲,使分频器的输出脉冲的相位提前1/16周期。高频时钟模块将本地高频时钟输入信号clk_in转换为两路相位差为90°的窄脉冲序列,分别为添门和扣门提供高频窄脉冲序列。添门为常闭门,在没有滞后脉冲控制时,此门始终关闭;扣门为常开门,若无超前脉冲控制时,窄脉冲信号通过此常开门。分频器将输入的高频时钟信号分频后输出位同步信号clk_out。

对位同步提取电路进行时序仿真,得到的时序仿真波形图如图3(b)所示。图中,code_in为输入码流,clk_out为位同步信号输出。由图可知,该电路可以从输入码流中准确提取位同步信号,并且在码流相位有变化的时,位同步信号可以快速地做出相位调整,保持同步。

2.1.3 帧同步单元的设计

为了正确地实施分接,在分接前必须先通过帧同步单元对合路信号进行帧同步检测。

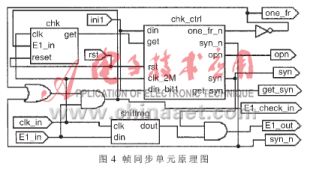

帧同步单元是复接设备中较复杂也很重要的部分。如图4所示,它主要由同步码检测模块(chk)和同步检测控制模块(chk_ctrl)两部分组成。其中,同步码检测模块对输入的数据流进行搜索,一旦检测到帧同步码(10011011),立即输出一个捕获脉冲信号(get);同步检测控制模块由帧同步系统状态计数器和一帧计数器等构成,完成帧同步单元的状态转换控制、每帧检测同步头的控制等功能。

帧同步的关键部分是前方保护和后方保护的设计。为了减少从失步到重新获得同步的时间和减小信道误码对同步工作状态的影响,从而得到较好的通信质量,本设计采用了2帧后方保护和3帧前方保护的方案。

帧同步系统状态转换图如图5所示。系统上电复位后,在起始时刻处于失步状态(STATE0_1xx——其中x表示无关值),系统从外部输入的合路码流中搜捕帧同步码“10011011”,若合路码流中没有帧同步码,状态计数器仍保持为1xx;若从合路码流中检测出同步码(get=“1”),则状态计数器清零为000,系统进入同步校核态(STATE1_000),开始将合路码流写入移位寄存器,分接器输出开关仍然为关闭状态(switch=“0”)。在同步校核状态下,若下一帧确认帧同步码不正确,判断为虚假同步,则状态计数器减1变为111,系统回到失步态;相反,若下一帧确认帧同步码正确,则系统进入同步态(STATE2_001),分接器输出开关打开(switch=“1”),开始正常分接合路码流。系统进入同步态后,若合路码流中出现帧同步码丢失,则状态计数器加1,系统进入同步保护态1(STATE3_010);若下一帧仍然检测帧同步码失败,则状态计数器再加1,系统进入同步保护态2(STATE4_011);若连续第三帧未收到帧同步码,则状态计数器再加1转为100,系统进入失步状态,停止分接合路码流(switch=“0”),同时重新开始搜捕帧同步码“10011011”。系统在同步保护态(状态计数器值为01x)下,若检测帧同步码正确,则状态计数器置数为001,系统回到同步态。

2.2 系统仿真与验证

在ISE集成环境下,调用ModelSim仿真软件对系统各模块进行功能仿真、综合后仿真以及布局布线后的时序仿真。仿真结果表明,复接器、分接器、同步单元等所有模块的设计均满足设计要求。

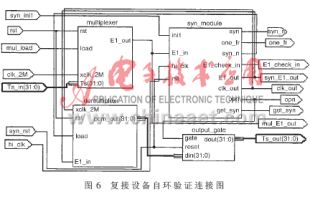

为了进一步确保系统设计的可实用性,将系统各组成模块按照自环工作状态连接起来,对系统各模块进行了联合仿真。复接设备自环验证的原理图如图6所示。

将32路64kbps的支路信号Ts_in(31:0)送到复接器(multiplexer)的支路信号输入端Ts(31:0),复接器的合路信号输出端E1_out与同步单元syn_module(包括位同步和帧同步)的合路信号输入端E1_in相连(自环),合路信号经过位同步信号提取以及帧同步检测后,由同步单元将非失步状态下的合路序列从信号输出端E1_out送出,同步单元还提供位同步信号clk_out,送分接器demultiplex的输入端xclk-2M,同步单元输出的合路序列送入分接器的合路信号输入端E1_in,经过分接器实施分接后,最后从支路输出控制单元output_gate的输出端可以得到各个支路的输出信号Ts_out(31:0)。

图7为复接设备自环验证的仿真时序图。其中,Ts_in为32个支路送来的64kbps的激励信号;mul_E1_out为经复接器实施复接后的合路信号;E1_check_in为进入帧同步码检测模块的合路序列;get_syn为帧同步码检测的结果;one_fr为同步校核和同步保护所需的帧同步码检测控制信号;syn_n为系统失步信号;syn_E1_out为非失步状态下的合路序列;opn为支路信号输出允许信号;Ts_out为实施分接后各支路的64kbps输出信号;Ts_in(1)为复接器第一支路输入信号;Ts_out(1)为分接器第一支路输出信号。

将输入激励信号Ts_in与系统支路输出信号Ts_out相比较,结果表明,在从同步到下一次失步的时间内,Ts_out与Ts_in信号波形基本一致——Ts_out中会出现一些1~2ns的过渡值,这些过渡值是由于Ts_out总线中32个支路信号到达寄存器输出端的时间不一致而造成的,这是由FPGA器件时延不确定性决定的。由Ts_in(1)和Ts_out(1)的波形比较可知,对于每个单一的支路信号,并不存在这种过渡值,分接后的支路信号与复接器支路输入信号一致。因此,Ts_out总线中出现的这种过渡值不会影响系统的性能。

时序仿真结果表明,复接、同步以及分接功能均正常,满足设计要求。在5万门的SPARTAN-3系列FPGA器件xc3s50上实现设计,硬件资源的使用情况如下:319个Slice,263个Slice Flip Flop,562个4 input LUT,70个bonded IOB,2个GCLK。该设计已作为一个模块应用到其它系统中,具有一定的实用价值。同时,由于该设计采用VHDL语言描述,具有可移植性,利用中小容量的FPGA就能实现该系统功能。

参考文献

1 张应中,张德民,温 荣.数字通信工程.北京:人民邮电出版社[M],1996.8

2 曹志刚,钱亚生.现代通信原理[M].北京:清华大学出版社,1992.8

3 段吉海,黄智伟.基于CPLD/FPGA的数字通信系统建模与设计[M].北京:电子工业出版社,2004.8

4 王 诚,薛小刚,钟信潮.FPGA/CPLD设计工具——Xilinx ISE 5.x使用详解[M]. 北京:人民邮电出版社,2003.6