1、引言

阿尔法磁谱仪(Alpha Magnetic Spectrometer,AMS)实验室是丁肇中博士领导的由美、俄、德、法、中等16个国家和地区共300多名科学家参加的大型国际合作项目。它是国际空间站上唯一大型物理实验,是人类第一次在太空中精密地测量高能量带电原子核粒子的实验。其目的是为寻找反物质所组成的宇宙和暗物质的来源以及测量宇宙线的来源。

但是对于AMS实验的空间电子系统,同样会受到高能粒子的袭击,导致存储器的内容发生变化,改写半导体存储器件的逻辑状态,导致存储单元在逻辑‘0’与‘1’之间发生翻转,使存储的关键数据出错,控制程序跑飞等。这对于AMS实验系统来说,是一个不容忽视的问题。因此,我们采用二元BCH(31,16)码,能纠正三位随机错误,这种纠错码信息不需要储存,不需要反馈,实时性好。

2、编译码原理

对于空间电子系统可能出现的问题,我们进行检错与纠错,其基本思想是在信息码组中以一定规则加入不同方式的冗余码,以便在信息读出的时候依靠多余的监督码或校验码来发现或自动纠正错误。

2.1 编码

编码比较简单,二元BCH(31,16)是GF(25)域上的线性分组码,其中二进制最高位m=5,总信息长n=2m-1=31,校验位数k=15,可纠错位数t=3,生成多项式g(x)为:

2.2 译码

译码过程比较复杂,包括1)求伴随多项式,2)系数计算电路,3)错误位置计算电路,其中最关键的是第三步,如图1。这里假设接收到的数据错了三位,第28、20、17位发生了0/1偏转,即

(1)求伴随多项式

根据生成多项式与ai的最小多项式之间的关系,用φi(x)去除接收多项式R(x)而得到伴随式分量,即,

(2)系数计算电路

令错误位置多项式

(3)错误位置计算

由上一步我们得出错误图样为:

因此原码多项式为:

![]()

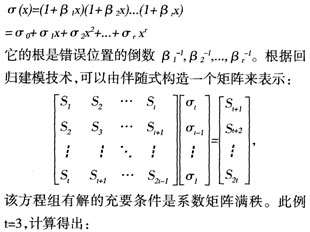

3、仿真与下载

对于上述编译码算法,采用Verilog HDL可综合语言来描述,整个程序分为顶层模块和底层模块,顶层模块很简单,主要完成底层模块的调用和数据的复位,编码算法主要由底层模块完成。其中包括编译码算法主程序,拨码开关控制程序,液晶显示程序,系统函数PLL(锁相环)程序。系统利用两个拨码开关sw1,sw2来控制编码结果或译码结果的下载与显示。

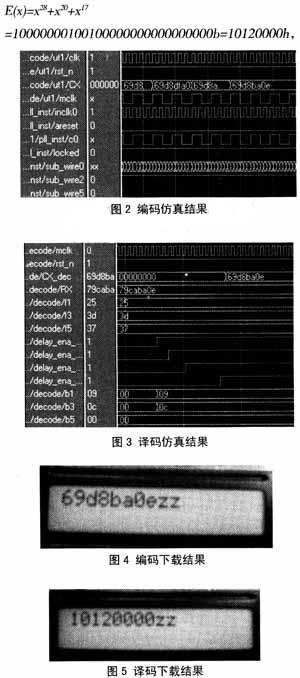

图2和图3是编码和译码的仿真图,仿真工具用的是Modelsim 6.0,编码结果CX=0x69d8ba0e,译码过程中,根据接收多项式RX=0x79caba0e以及最小多项式f1=0x25,f3=0x3d,f5=0x37,译码后得出错误多项式EX=0x10120000,最后RX与EX相与得出CX_dec=0x69d8ba0e,与原码一致。图4和图5是下载后显示到液晶屏的结果CX=0x69d8ba0e,EX=0x10120000,所用编译工具是QuartusⅡ5.0,FPGA芯片采用的是Altera Cyclone EP1C6,用到1个PLL,引脚数15个,芯片资源耗用不超过5万门。

4、结束语

BcH(31,16)编译码算法,可以纠正3位错误,用VerilogHDL可综合语言描述以上的编码纠错过程,软件仿真和硬件下载都证明了算法的正确性和可行性。整套试验系统是模拟空间存储器受到高能粒子的干扰而发生错误,这对于我们AMS实验也是很关键的一步,现阶段我们用到的防护措施是三倍冗余编码纠错,但它占用的硬件资源比较多,而本文中所研究的循环BCH码能够节省资源,纠错效果也很明显,所以它将会在AMS项目中得到实际的应用。