文献标识码: A

DOI:10.16157/j.issn.0258-7998.2015.11.006

中文引用格式: 彭昊,黄骏雄,江先阳,等. 多通道高保真音频信号IIR滤波器设计[J].电子技术应用,2015,41(11):24-26,30.

英文引用格式: Peng Hao,Huang Junxiong,Jiang Xianyang,et al. Multi-Channel IIR filter design based on FPGA[J].Application of Electronic Technique,2015,41(11):24-26,30.

0 引言

数字滤波器是现代数字信号处理系统的重要组成部分,具有模拟滤波器所无法替代的优越特性,在语音处理领域更是有着很广泛的运用。数字滤波器根据单位脉冲响应的不同,可分为有限脉冲响应滤波器(FIR)和无限脉冲响应滤波器(IIR)。FIR滤波器的优点在于具有良好的相位特性,IIR滤波器的优点在于拥有良好的幅频特性。IIR和FIR滤波器相比,在低阶数时就可以达到很好的频率滤波性能,但其相位特性是非线性的[1]。

音频信号可以视为不同频率正弦波信号的叠加。通过对于音频信号系统的频谱分析,可以很清晰地分辨出需要保留的信号以及需要抑制的噪声信号。因为人耳对于声音的相位变化是不敏感的,所以在音频信号的滤波中,IIR滤波器的应用相比于FIR更有优势[2]。

另一方面,随着娱乐媒体的发展,高精度的多通道处理更是进行音频信号处理的重要而基本的需求之一。由于软件的串行特性,多通道的音频信号在处理上往往需要预先搭建特别的平台,这使得采用软件实现的方式既不经济又缺乏扩展性。目前的设计很多都是针对单通道进行实现,而音频信号往往又存在需要多个声道混合产生立体声的问题。一种传统的做法是通过DSP专用芯片来实现实时性的音频信号处理[3-5],但这种方式中实现并行多通道传输往往需要消耗额外的器件资源;而另外一种通过FPGA实现的滤波器方案采用以FPGA内部的SOPC实现的一种软件方式,并没有涉及到使用FPGA良好的硬件器件特性实现多路复用的方法[6]。针对这一问题,本文基于FPGA设计了一款可扩展的时分复用多通道IIR滤波器。

1 IIR滤波器的设计

1.1 系统的稳定性判断

稳定性是一个滤波器的重要指标。IIR滤波器的系统传递函数是复变量z的有理函数,其分子和分母都是z-1的多项式,因此H(z)可以表示为:

其中ci(i∈[1,M])是零点di(i∈[1,N])的极点。一个线性时不变系统当且仅当它的系统传递函数H(z)的极点都处于单位圆内时(包括单位圆)是稳定的。由于实际的PCB板内部的电磁干扰输出端会出现一个幅度极小频率极低的干扰噪声,在后级放大后使得噪声不能忍受,所以滤波器希望能滤掉采样率为48 kHz的音频信号中因PCB中噪声干扰产生的一个极低的噪声信号,目标滤波器的滤波器斜率为12 dB/OCT,中心频率为6 Hz。

1.2 系数量化转换

由理论设计出的理想数字滤波器传输函数的系数ai、bi如果用二进制表示是无限精度的。在实现时硬件只有限位宽,所以必须对数字滤波器传递函数的系数进行量化转换。具体来说在FPGA中实现差分方程时,一般是把这些非整数系数乘以2L然后取整[7-8]。当L值足够大的时候,就可以保证IIR滤波器的精度。而当滤波器的系数乘以2L,从硬件上可以相应转化为左移L位操作,左移操作无需消耗乘法逻辑单元从而节约了逻辑资源。系数量化转换完成后可以通过Matlab验证滤波器系数是否满足稳定条件。

1.3 系数的简化问题

高保真的音频信号一般是24位的有效数据,为了保证滤波后音频信号的精度,滤波器系数也设为24位。通过使用巴特沃斯型IIR滤波器可以将零点全部调整到单位圆与X轴Y轴的交点处,从而将ai系数全部调整为整数。在此基础上将系数乘以2L(L为整数)后可以将乘法操作转化为移位操作节省逻辑资源。

依据应用需要,目标滤波器的中心频率为6 Hz,所需要的滤波器衰减斜率为12 dB/OCT,即一个二阶滤波器。采用Matlab的fdatool工具设置对应参数并选择滤波器为巴特沃斯逼近,生成满足条件的滤波器系数[9-10],如表1所示。

基于1.1节的稳定性分析可知,这一滤波器是一个稳定的二阶IIR滤波器,其差分方程可以描述为:

y(n)=a1x(n)+a2x(n-1)+a3x(n-2)+b2y(n-1)+b3y(n-2)

=x(n)-2x(n-1)+x(n-2)-1.998 89y(n-1)

+0.998 89y(n-2)(2)

依据式(2)和上述分析,这一滤波器在硬件实现上可简化为两个24位乘法器以及数据的移位、求和操作。

1.4 多路时分复用分析

提供多通道可扩展支持有两种方式:(1)在资源限制小的情况下,综合考虑所需要的滤波器的最大工作频率以及所需要的通道数,利用FPGA资源的丰富性对单一滤波器结构进行逻辑复用从而实现并行方式的多路扩展;(2)在所需要的滤波器的工作能力要求不高的情况下,根据所需要的通道数,通过时分复用的方式使用单一的逻辑资源实现多路通道的扩展方案减少资源消耗。由于音频信号传输的速率往往不高,使用时分复用单一逻辑的方式会比使用逻辑复用的方式更为经济,本文基于这一目标设计实现一个4通道的二阶IIR滤波器,更多通道的情况将采取类似的思路进行扩展。

常用的音频数据格式中一次采样的音频信号占32位,如I2S数据格式中一次采样中有24位有效数据而另外8位恒定为0,相当于一次采样保有32个时钟周期的可利用时间。在4路数据并行情况下,每一路数据计算及缓存值的更新共同所需的时钟周期数为Tqt≤32/4=8,也即设计的滤波器操作周期最大不能大于8。从式(2)发现每一路信号都需要保存4个中间结果:x(n-1),x(n-2),y(n-1),y(n-2)。由于这些中间结果之间有强烈的数据延迟依赖关系,即x(n-1)、x(n-2)分别为在第n次计算时第n-1次及第n-2次的数据输入值,y(n-1)、y(n-2)分别为第n-1次的数据输出值以及第n-2次的数据输出值,在时分复用操作过程中可以利用这一延迟关系节省时间。

2 IIR滤波器硬件电路实现

2.1 滤波计算控制状态机

前面已经给出滤波器每一次的计算周期数不能高于8,在这不多于8个周期内要能够稳定处理中间数据的保存和刷新工作采用状态机实现。观察式(2)在采用的设计方法情况下,其计算过程的第n次输入的数据x(n)仅需要进行移位和加减操作;y(n-1)和y(n-2)需要使用乘法单元。这一部分的计算利用延迟特性可以从上一路计算结束时开始,进而形成流水线提升整个计算效率。

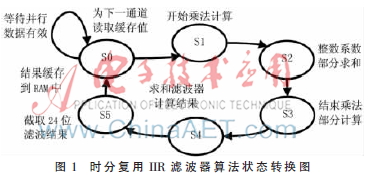

设计中采用的算法状态转换图如图1。其中所示的每一个状态均占用一个周期,正好能满足只要有数据输入整个计算过程为8个周期。为了合理地利用延迟,从S0状态时即可对RAM中的数据进行预读,这样在读入数据后的下一个周期,乘法器单元能自动地进行乘法计算,同时在S3状态时得到乘法的输出结果;乘法器采用3级流水线结构刚好和这一计算过程匹配,充分利用数据的延迟特性,并且能极大地提高该设计的计算能力,对于后续的扩展有着关键意义。对于系数部分的移位和求和过程,则在S1和S2状态分别执行以节省时间。

2.2 多路复用滤波器结构

设计采用的滤波器结构如图2所示。宽度为24的4路待处理数据从外部输入后,首先将24位的待计算值送入常系数运算处理单元[11],这一运算中,首先对于a1、a2、a3系数左移L位,然后求和a1、a2所对应部分的结果sum1,再将sum1与a3移位后所对应的部分求和得到常系数运算处理单元计算结果。在进行移位操作的同时从RAM表中取出参与该次计算的y(n-1)、y(n-2),并分别在相应乘法单元中进行运算,得到乘法计算的部分和,随后将各乘法单元以及常系数运算处理单元的运算结果输入求和单元进行运算,并根据参数的扩展量2L截取求和单元输出的[L+23:L]作为最终输出,这一部分的值还将作为下次计算的y(n-1)存入RAM数据保存区中。为了实现更多的多路扩展,在采用类似机制的同时,需要对于RAM数据保存区的存储单元大小进行适当调整,以使得容量足够处理相应多路条件下的中间数据。

2.3 目标滤波器资源占用情况

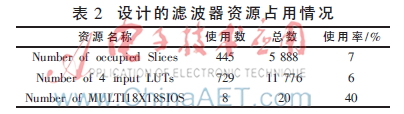

目标滤波器选用的器件为Xilinx公司的Spartan 3AN XC3S700A一款非DSP强化型FPGA。目标滤波器对应的主要资源消耗情况如表2所示,可见所消耗的资源数非常低。乘法器的消耗主要是采用24位乘24位的乘法器IP核来处理音频信号。目标滤波器在该器件上可达到的最大工作频率为129.121 MHz,远远高于实际使用的时钟频率,说明这一逻辑可以适用于时钟频率更高或同时满足更多通路的时分复用操作的环境中。

3 仿真测试与讨论

本文采用Matlab SE 10.1a与ISE Design Suite 14.7联合仿真来测试所设计的IIR滤波器。在测试流程中将比对Matlab软件计算结果和硬件计算结果,从而判断硬件实现的成效。仿真测试中,采用一个1.5 kHz幅值为1的正弦波信号叠加上一个3 Hz幅值为3的正弦波信号作为低频噪声。先使用Matlab产生这一激励信号形成文件然后在测试中读取这一文件。为了验证该硬件滤波器的性能,将Xilinx与Matlab数据联合仿真的输出结果通过Matlab绘制成频谱图如图3所示,同时利用modelsim将测试的多路滤波的结果显示如图4所示。

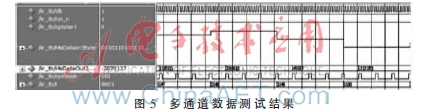

图3所示为信号处理前的频谱图,由于仿真中使用的噪声信号频率很低,中频部分几乎没有信号,所以将处理前的频谱分为0~15 Hz,1 000 Hz~2 000 Hz显示;图4为处理后的频谱。对比图3与图4可见对于3 Hz的噪声信号通过设计的滤波器后,幅值减为原来的一半,实现了-3 dB的衰减。图5显示每一个数据均能保持4次计算结束信号周期的时长说明了该滤波器具有多通道时分复用的功能。

4 小结

本文根据实际的音频信号处理工程需求,设计了一款基于时分复用方式实现4通道语音信号滤波的二阶IIR滤波器。通过Matlab和modelsim的联合仿真,读取输出数据导入Matlab并通过绘制出对应频谱,验证了该滤波器的幅度频率特性满足设计目标要求。

在设计中将传输函数的系数转换为整数,从而将乘法计算转化为简单的移位操作节约FPGA专有乘法器单元,这一优化形式可以方便地拓展到其他应用中。

文章提出了两种通道扩展的方式。本设计目标滤波器依据所处理的音频信号特点采用了其中的时分复用方式。此外,因为二阶滤波器是高阶滤波器的基本单元,高阶滤波器可以通过二阶滤波器以级联方式来实现[12],所以本文所设计的IIR滤波器对于实现更复杂语音信号处理所需的高阶IIR滤波器有一定的参考意义。

参考文献

[1] 周利清,苏菲.数字信号处理基础(第二版)[M].北京:北京邮电大学出版社,2007.

[2] 赵力.语音信号处理(第二版)[M].北京:机械工业出版社,2011.

[3] 谢海霞,孙志雄.IIR滤波器的DSP实现[J].电子器件,2013,36(2):194-196.

[4] 崔景安,徐宁.实时音频信号采集系统中的数字滤波器的设计及实现[J].内蒙古大学学报(自然科学版),2014,41(3):336-339.

[5] 栾军山,陈华.实时音频处理系统中的IIR滤波器设计及Lattice结构实现[J].制造业自动化,2011,33(5):97-100.

[6] 邸丽霞,张彦军,刘怡文.基于SOPC的高速IIR滤波算法的实现[J].科学技术与工程,2013,13(33):9978-9982.

[7] 秦宏伍,史浩,崔·尤里·谢尔盖维奇.基于FPGA的IIR滤波器整数设计[J].微计算机信息,2007,23(122).

[8] MEYER-BEASE.Digital signal processing with field programmable gate arrays[M].Springer,2007.

[9] 刘彬.MATLAB环境下IIR滤波器设计,仿真与验证[J].电子测量技术,2011,34(4):7-10.

[10] 薛定宇,张晓华.控制系统与计算机辅助设计——MATLAB语言与应用(第二版)[M].北京:清华大学出版社,2000.

[11] 张大为,姜静,刘迪.基于FPGA的IIR低通数字滤波器的设计[J].船电技术,2012(2).

[12] 王卫兵.高阶IIR数字滤波器的FPGA描述[J].现代电子技术,2005,207(16):3-4.