420亿美元蛋糕将至 先进IC封装如何撬动

2020-12-02

来源: 与非网

先进封装在新型系统级芯片的开发中正在扮演着越来越重要的角色,并日益成为一种更加可行的解决方案。但是,对于芯片制造商来说,它提供的一系列选择有时令人困惑,有时价格太高。

汽车、服务器、智能手机和一些其它高端系统已经采用了某种形式的先进封装,而对于其它应用来说,简单的封装技术就足够了。尽管如此,先进封装正迅速成为吸引许多人的选择。业界正在开发新形式的先进级封装技术或者对现有技术进行升级,以用于 5G 和 AI 等一系列新兴应用。

几十年来,以一个基本形式的封装把裸片组装起来是可行的,但是,随着芯片工艺尺寸的缩减走到了尽头,封装技术打开了另一个视角,它提供了一套全新的架构选择,既可以提高性能,又能降低功耗并为设计增加灵活性,从而既可以针对特定市场进行定制,又可以缩短上市时间。

但是,没有任何一种封装类型可以满足所有需求。每个应用对封装的要求都是不同的。在某些情况下,先进包装甚至可能不是正确的解决方案。

Semiconductor Engineering 研究了先进封装技术在四个主要市场中的优势和挑战:服务器、网络设备、智能眼镜和军事 / 航空航天。尽管这里给出的只是先进封装技术可能应用领域的若干示例,但是,这里的分析依然突显了芯片制造商未来将在封装方面面临的一些主要问题和挑战。

根据 YoleDéveloppement 的数据,2019 年整个 IC 封装市场的价值为 680 亿美元。其中,先进封装的规模为 290 亿美元,预计它将以增长 6.6%的速度增长,到 2025 年达到 420 亿美元。

服务器领域

通常情况下,设备制造商依靠芯片工艺尺寸的缩减实现设计的升级,其目标是在每一代新工艺节点的单片芯片上封装更多功能,新节点大约每 18 到 24 个月推出一次。但是现在,工艺尺寸的缩减变得越来越困难和昂贵,并且价格 / 性能优势正在减少。因此,尽管工艺尺寸依然将继续缩减,但是,并非系统中的所有组件都按同样的比例进行缩减。

联华电子业务发展副总裁 Walter Ng 说:“客户需要更优化的、提供更具成本效益的技术解决方案和业务解决方案。从上市时间的角度来看,在先进节点上设计和验证大型片上系统(SoC)所花费的时间也是一个不得不考虑的问题。”

图源 | The Motley Fool

在服务器领域,它采取的方式是将不需要或者不能从中受益的功能从最先进数字逻辑工艺上卸载下来,同时使用高速管芯对管芯互连的异构集成,目前流行的方案是“小芯片”。

在小芯片中,芯片制造商可能有一个库,库中有一系列模块化管芯或小芯片,这些模块不需要都在同一工艺节点上开发。通常来说,包含小芯片的设计类似于单片 SoC,但是开发成本较低。

当然,听起来这种方法很好,但是它仍然存在一些挑战。“这是一个新兴的环境,是一种新模式。接口方面的标准不足。最早采用小芯片集成的公司往往是可以控制所有设计元素,特别是接口的垂直集成公司,” ASE 的业务开发高级总监 Eelco Bergman 在最近的 IMAPS2020 会议上的演讲中说。“如今,小芯片设计将主要由芯片开发者推动,无论是 IDM 还是无晶圆厂供应商。随着行业的发展和生态系统的开放,您会看到这种变化。”

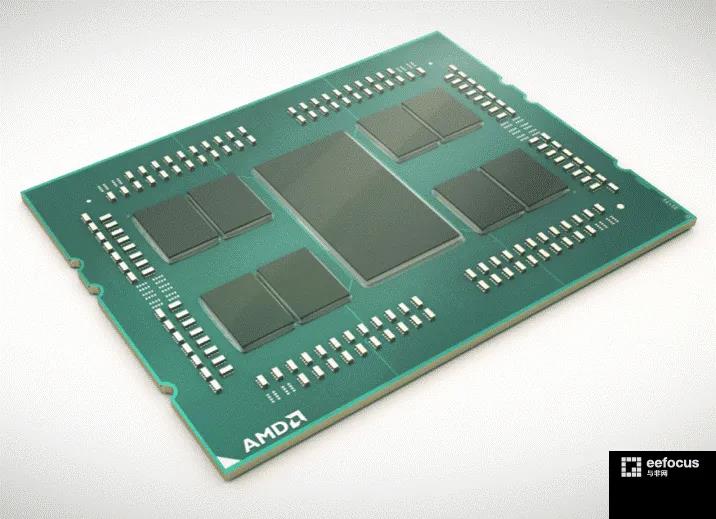

AMD、英特尔和其他一些公司已经引入了类似小芯片的架构。例如,AMD 最新的服务器处理器系列取代了大型的单芯片,它将较小的芯片集成到了一个模块中,该模块有时称为多芯片模块(MCM)。使用管芯到管芯互连来连接芯片。

AMD 的 MCM 被称为 2D 小芯片设计,它集成了基于 14nm 工艺的集成 I / O 和内存控制器芯片,这个 14nm 的芯片在整个模块的中间。MCM 中还集成了八个 7nm 处理器管芯。四个处理器管芯位于 I / O 管芯的每一侧。

具有 8 个内核芯片和 1 个 I / O 芯片的 AMD EPYC 服务器

图源 | AMD

AMD 的服务器处理器产品线转向了类似小芯片的方案有几个原因。“为了维持每两年性能提升 2 倍的趋势,我们需要使用小芯片技术,不仅要以更高的良率集成更多的晶体管,还需要减少先进工艺节点上的硅容量。”AMD 的高级研究员 Bryan Black 在一次演讲表示。

展望未来,AMD 计划在服务器处理器方面扩大 MCM 的战果。它还计划使用 3D 堆叠技术开发小芯片。Black 说:“随着我们进入 3D 堆叠的世界,我们在 2D 世界面临的所有挑战都将加剧。”

最重要的是,封装需要裸片具有适当的良率,也被称为良品白片。封装中有一个坏晶粒就可能导致产品或系统故障。“所有裸片都有参数变化。因此,我们会遇到多管芯解决方案的基本测试和特征化问题。有些管芯速度很慢,有些很快,有些消耗的电量更多,有些消耗的电量更少。”Black 说。

热量、功率分配和可靠性也是基于小芯片设计的挑战。然后,如果封装失败了,那么最大的问题就是谁来负责。是芯片供应商、IP 供应商还是封装厂?

在这方面,封装行业可以借鉴过去的经验,尤其是 2.5D 早期阶段。使用 2.5D 时,管芯堆叠或并排放置在中介层的顶部。中介层结合了硅通孔(TSV),充当芯片和电路板之间的桥梁。

在 2.5D 的早期阶段,设备制造商一直在努力应对不同的管芯、集成问题和成品率挑战。但是,随着时间的流逝,供应商解决了这些问题。

如果管芯不符合规格,供应商将对器件进行广泛的根本原因分析。这需要一个完善的测试策略。

网络设备领域

网络设备供应商也面临许多相同的挑战。网络是一个复杂的系统,覆盖从家庭办公室到云的广泛范围。为了应对这些市场,通信设备供应商针对网络的各个子市场出售不同的系统。

例如,在网络的一部分中,思科为大型服务提供商出售路由器。路由器使用 IP 数据包进行网络定向。思科最新的路由器基于其自研的 ASIC。思科的单片 ASIC 围绕 7 纳米工艺构建,可在同一芯片上实现 12.8 Tbps 的带宽。

图源 | chainbulletin.com

思科还为其它网络产品开发 ASIC,其他通信设备供应商也开发自家的 ASIC。

出于多种原因,供应商也在探索或实施替代方法。在每个节点上,ASIC 变得越来越大,越来越昂贵。它还集成了 SerDes(串行器 / 解串器),可提供高速的芯片到芯片通信。

Juniper 的资深工程师 Valery Kugel 在演讲中说:“网络带宽扩展的要求导致每一代技术的联网 ASIC 裸片尺寸都会增加。(SerDes)占据了 ASIC 的很大一部分。”

还有一些其它的问题。ASIC 由数字和模拟模块组成。数字部分可以得益于工艺的升级,可在更高带宽下实现更多功能。但是,并非所有事情都能从工艺缩减中受益。

“SerDes 功能不能受益于工艺缩减,它是一个模拟结构,无法很好地扩展。” TE Connectivity 的技术专家兼行业标准经理内森·特雷西(Nathan Tracy)说。Tracy 还是行业标准组织光学互联网络论坛(OIF)的主席。

这里有包括小芯片在内的几种解决方案。为了将芯片连接到封装中,OIF 正在开发一种称为 CEI-112G-XSR 的芯片对芯片接口标准。XSR 连接 MCM 中的小芯片和光学引擎。它可通过短距离链路实现高达 112Gbps 的数据速率,目前该 XSR 标准仍处于草稿阶段。

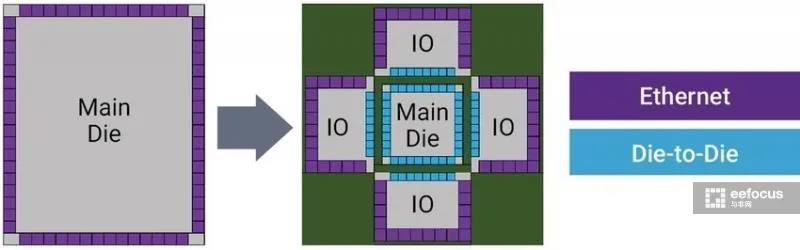

有几种方法可以在网络设备中实现小芯片和 XSR。例如,大型 ASIC 分为两个较小的管芯,这些管芯使用 XSR 链接进行连接。

在另一个示例中,大型 SerDes 模块被分解为四个较小的 I / O 芯片。然后,在 MCM 中,ASIC 位于中间,中间被四个较小的 I / O 小芯片包围。

需要管芯到管芯连接的以太网交换机 SoC 的示例

图源 | Synopsys

另外,设备制造商可以将光学引擎与 MCM 中的交换芯片 ASIC 集成在一起。

特雷西说:“业界对于和光学器件共同封装的讨论很多。我在这里说的是,从交换机面板上的可插拔光收发器转移到直接将光学引擎安装在交换机 SoC 上的可能性。您需要一个低功耗的高速互连。讨论的重点是 OIF 的 XSR 开发。”

小芯片的采用将取决于具体应用。在某些情况下,ASIC 仍然是有意义的。这里有几个因素,例如成本和产量。特雷西说:“这一切都是为了减少功耗。”

智能眼镜领域

图源 | www.ebay.com

这些解决方案可能适用于网络设备,但是消费市场有不同的要求,尤其是对于新兴产品而言。

例如,在研发方面,多家公司正在开发下一代智能眼镜或 AR / VR 眼镜。虚拟现实(VR)使用户可以体验 3D 虚拟环境。增强现实(AR)能够获取计算机生成的图像,并将其覆盖在系统上。

如果这项技术可行,AR / VR 眼镜可以用于数据检索、面部识别、游戏和语言翻译。他们还可以将演示文稿或键盘投影在表面上。

Facebook Reality Labs 的主任兼研究科学家 Liu Chiao 在去年 IEDM 上的一篇论文中表示:“ [AR / VR]及其变体设备只是下一代计算平台之旅的开始。”

开发一副有用且便宜的智能眼镜并不是一件简单的任务。这些产品需要新的低功耗芯片、显示器和接口。在这些眼镜中,使用语音、视线和头部 / 身体移动来激活程序。所有这些技术都必须是安全的。

“我们将需要全面的大幅度改进,” Facebook 的硅工程主管 Ron Ho 在 IMAPS2020 的演讲中说。“相对于功率,我需要的性能要比当今系统的性能高得多。通常,我需要以较低的延迟更快地运行事情。”

为了以合适的尺寸实现智能眼镜,IC 封装是关键。Ho 说:“我必须管理能够提高性能和降低延迟的封装。您不能强迫芯片在 PCIe 上经过多英寸的走线并消耗大量功率。但是,您可以将它们共同封装在一起,然后放在彼此旁边。通过 TSV,它们具有更高的带宽和更高的性能连接。”

在 IEDM 上,Facebook 披露了有关其 AR / VR 眼镜的一些线索,这些眼镜正在研发中。Facebook 在一篇论文中概述了用于 AR / VR 眼镜的计算机视觉接口技术的发展。其底层技术是一种先进的 CMOS 图像传感器。

CMOS 图像传感器在智能手机和其他产品中提供相机功能。但是标准的图像传感器不足以用于 AR / VR 眼镜。这里需要的是具有先进封装的机器感知优化图像传感器。Facebook 在论文中描述了一种三层图像传感器。第一层是具有处理单元的图像传感器,其后是聚合处理器,然后是云计算平台。

Facebook 还提到了铜混合键合技术。使用铜 - 铜扩散键合技术将管芯堆叠并连接。目前尚不清楚 Facebook 是否会走这条路,但是混合键合是图像传感器领域的一项已知技术。

军事 / 航空领域

同时,几十年来,美国国防部(DoD)认识到芯片技术对于保持美国的军事优势至关重要。国防界在各种系统中使用各种高级节点和成熟节点上的芯片。封装也是很关键的一部分。

军事 / 航空航天涉及众多具有不同要求的客户,当然这里有一些共同的主题。Quik-Pak 的 Molitor 说:“我们为许多不同领域提供服务。我们也为军用 / 航空业服务。军事 / 航空计划往往是长期存在的。它们习惯于处理必须工作 20 到 30 年的组件。”

军用 / 航空客户面临其他挑战。与商业领域一样,开发先进芯片的成本昂贵,但每次节点升级带来的收益却在减小。另外,对于国防界而言,对芯片产量的需求相对较少。

有时,国防界使用非美国本土的代工厂获得先进工艺的芯片,但出于安全目的,它更倾向于使用本土供应商。军用 / 航空业客户希望获得可信赖且有保证的芯片和封装供应链。

尽管如此,国防部仍在寻找芯片工艺升级以外的替代方法,即异构集成和小芯片。

图源 | theburnin.com

例如,英特尔最近获得了国防部小芯片的新合同,称为先进异构集成原型(SHIP)项目。根据该计划,英特尔围绕小芯片建立了一个新的美国商业实体。该计划使国防部和国防行业的客户可以使用英特尔的封装技术。

SHIP 计划包含多个部分。英特尔赢得了该计划的数字组件合同,Qorvo 则拿下了 SHIP 计划的 RF 组件合同。在该项目下,Qorvo 将在德克萨斯州建立一个射频异构封装设计、生产和原型制作中心。该中心将主要为国防行业服务。

Qorvo 对军事 / 航空行业并不陌生。多年来,这家 RF 器件和其他产品的供应商一直为军事 / 航空和商业领域提供芯片制造和封装服务。该公司开发了基于氮化镓(GaN)、砷化镓(GaAs)和其他工艺的器件。

根据 SHIP 计划,Qorvo 将使用基于氮化镓、砷化镓和硅器件提供异构封装服务。目的是满足国防部所称的 SWAP-C(这是一个首字母缩写,表示相控阵雷达系统、无人驾驶车辆、电子战平台和卫星等各种应用)中的尺寸、重量、功率和成本要求。

尽管 Qorvo 将提供一站式服务,但 SHIP 计划主要是针对封装的。它将继续为军事 / 航空客户提供芯片制造和封装服务。“我们使用自己的代工模型为之建模。我们使用的是同一种开放获取型的模型。这将是一项服务,您可以在我们的代工厂中进行设计,然后再考虑使用我们的封装技术来封装这些零部件,因此,SHIP 计划是对我们现有能力的补充或扩展。”White 说。

同时,军事 / 航空行业涉及到定制化的工作。每个客户可能有不同的封装要求,并面临各种挑战。

以 RF 为例。White 说:“ RF 行业面临的挑战之一是,一旦将器件放入封装中,就会改变 RF 性能。您必须设计芯片和 MMIC 使其适合这些封装,并使其性能尽可能接近其最初的预期性能。”

写在最后

预计还有许多其它市场将推动更加异构的集成。苹果公司的低端 Mac 计算机正在转向内部开发的 M1 处理器,该处理器将 CPU 核心、图形和机器学习引擎集成在“定制封装”中。

现在,一切才刚刚开始。在其它市场(例如 5G、人工智能、移动设备)中,存在许多新的封装机会,并且伴随着许多挑战。但是,在市场发生新的重大变化的情况下,似乎从来都不缺少使行业从业者忙碌起来的机会。