英特尔官网披露Intel 3 工艺节点技术细节

应用更多EUV光刻,同功耗频率提升至多18%

2024-06-20

来源:IT之家

6 月 19 日消息,作为 2024 IEEE VLSI 研讨会活动的一部分,英特尔近日在官网介绍了 Intel 3 工艺节点的技术细节。

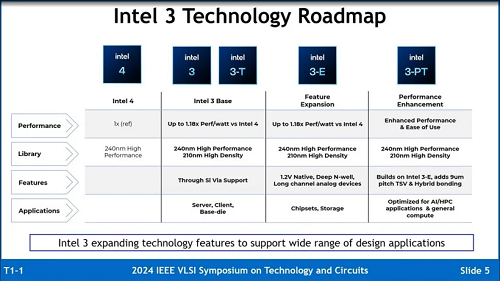

Intel 3 是英特尔最后一代 FinFET 晶体管工艺,相较 Intel 4 增加了使用 EUV 的步骤,也将是一个长期提供代工服务的节点家族,包含基础 Intel 3 和三个变体节点。

其中 Intel 3-E 原生支持 1.2V 高电压,适合模拟模块的制造;而未来的 Intel 3-PT 进一步提升了整体性能,并支持更精细的 9μm 间距 TSV 和混合键合。

英特尔宣称,作为其“终极 FinFET 工艺”,Intel 3-PT 将在未来多年成为主流选择,与埃米级工艺节点一同被内外部代工客户使用。

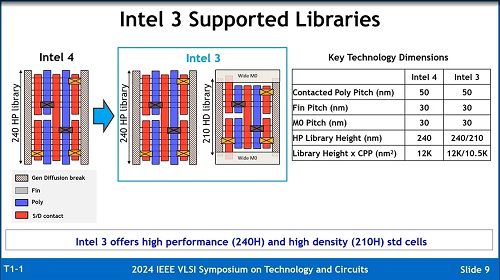

相较于仅包含 240nm 高性能库(注:HP 库)的 Intel 4 工艺,Intel 3 引入了 210nm 的高密度(HD)库,在晶体管性能取向上提供更多可能。

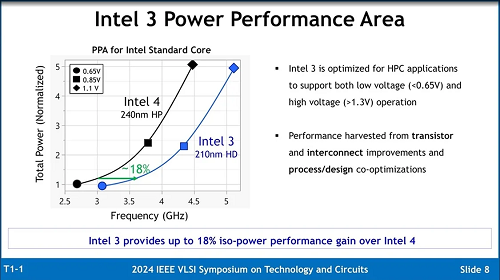

英特尔表示,其基础 Intel 3 工艺在采用高密度库的情况下,可相较 Intel 4 工艺至多可提升 18% 频率。

此外英特尔还宣称基础版 Intel 3 工艺密度也增加了 10%,实现了“全节点”级别的提升。

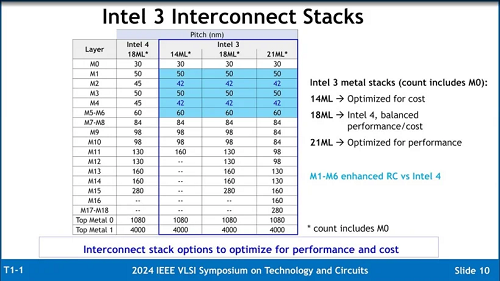

而在晶体管上的金属布线层部分,Intel 3 在 Intel 4 的 14+2 层外还提供了 12+2 和 19+2 两种新选项,分别面向低成本和高性能用途。

具体到每个金属层而言,英特尔在 Intel 3 的 M0 和 M1 等关键层上保持了与 Intel 4 相同的间距,主要是将 M2 和 M4 的间距从 45nm 降低至 42nm。

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306118;邮箱:aet@chinaaet.com。