SK海力士将转向4F2结构的3D DRAM

以降低EUV光刻成本

2024-08-14

来源:芯智讯

8月13日消息,据Thelec报道,SK 海力士研究员Seo Jae Wook 周一在韩国首尔举办的产业会议中指出,自从1c纳米制程DRAM 商业化之后,极紫外光(EUV)光刻制程成本将快速攀升,SK海力士计划开发3D DRAM以进一步控制成本。

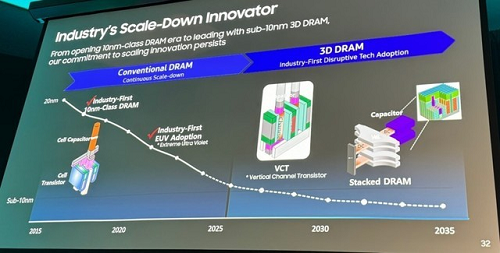

Seo Jae Wook 认为,现在是确认使用EUV制造DRAM 是否有利可图的时刻,目前公司考虑未来DRAM 制造采用垂直栅极(VG)技术,即所谓的“3D DRAM”。

所谓的垂直栅极技术是DRAM制造商内部所称的“4F2”结构,这是一种经过大量研究的单元阵列结构,其中晶体管以垂直方式堆叠,也就是3D DRAM。三星将这种3D DRAM 称为“垂直通道晶体管”(vertical channel transistor,简称VCT)。

4F2结构从下而上依序为源极(source)、闸极(gate)、汲极(drain)和电容器(capacitor)。字元线(Word Line)连接到闸极,位元线(Bit Line)则连接到源极。与6F2 DRAM 相比,采用这种单元阵列可将芯片表面面积减少30%。

知情人士表示,三星和SK 海力士目标是10nm制程以下的DRAM 应用4F2 技术。 SK 海力士的Seo Jae Wook 认为,采用VG 或3D DRAM 制程设计,可将EUV 制程成本降一半。

三星此前宣布成功将3D DRAM 堆叠到16 层,但表示现在不是量产阶段,而是可行性验证阶段。

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306118;邮箱:aet@chinaaet.com。