博通向富士通交付3.5D F2F封装的2nm芯片

2026-02-28

来源:芯智讯

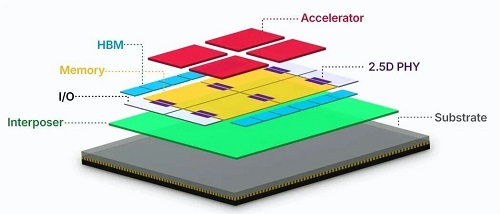

当地时间2026年2月26日,美国芯片大厂博通公司宣布,已开始向富士通交付业界首款基于其3.5D超大尺寸系统级封装(XDSiP)平台打造的2纳米定制计算SoC。3.5D XDSiP是一个成熟的模块化多维堆叠芯片平台,它结合了2.5D技术和采用面对面(F2F)技术的3D集成电路集成。

3.5D XDSiP 是下一代 XPU 的基础。借助 3.5D XDSiP,消费级 AI 客户能够交付最先进的 XPU,其信号密度无与伦比,能效卓越,延迟极低,足以满足千兆瓦级 AI 集群的海量计算需求。博通的 XDSiP 平台支持计算、内存和网络 I/O 在紧凑的外形尺寸内独立扩展,从而实现大规模的高效低功耗计算。

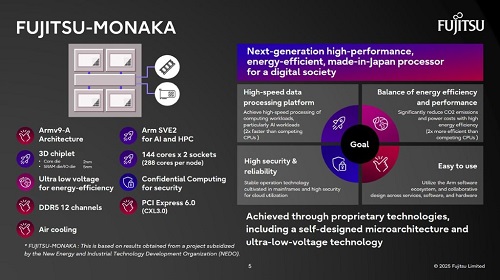

据了解,富士通即将推出的一款面向数据中心的处理器Monaka,正是采用了基于台积电的CoWoS-L封装技术的博通3.5D XDSiP技术平台,其拥有4个计算模块,每个模块拥有36个基于Armv9指令集的CPU核心,共144个CPU内核,均基于台积电2nm制程,并使用混合铜键合 (HCB) 以面对面 (F2F) 方式堆叠在 SRAM tiles 上(本质上是巨大的缓存)。SRAM tiles是基于台积电的5nm工艺制造的。计算和缓存堆栈伴随着一个相对巨大的 I/O 芯片,该芯片集成了内存控制器、顶部带有 CXL 3.0 的 PCIe 6.0 通道以连接加速器和扩展器,以及人们期望从数据中心级 CPU 获得的其他接口。

博通ASIC产品部高级副总裁兼总经理Frank Ostojic表示:“我们很自豪能为富士通提供首款3.5D定制计算SoC,这证明了博通团队的出色执行和创新。自2024年推出我们的3.5D XDSiP平台技术以来,博通扩大了其3.5D平台功能,以支持我们将于2026年下半年发货的更广泛客户群的XPU。这些发展突显了博通在提供高复杂性XPU方面无与伦比的技术领先地位,以实现人工智能的变革性突破。”

富士通高级副总裁兼高级技术开发部负责人Naoki Shinjo表示:“博通3.5D XDSiP技术的推出标志着先进半导体集成的一个变革性里程碑。通过将2nm工艺创新与面对面3D集成相结合,它释放了下一代人工智能和高性能计算所必需的前所未有的计算密度和能效。这一突破是富士通富士通推出尖端、高性能和低功耗处理器的关键推动因素。我们高度重视与博通的战略合作伙伴关系,相信这项技术将有助于推动一个更具可扩展性和可持续性的人工智能驱动社会。”