1. 引言

1.1 用 CPLD 实现 GPIB 控制芯片的意义

综观现今市场上的测试仪器,不难发现 GPIB 总线有重要的作用,在研制台式测试仪器 的时候,客户几乎均要求具备 GPIB 接口。可是在实际研发过程中,却发现 GPIB 控制芯片很难购买,而且价格昂贵。而且作为测试仪器具备 GPIB 的接口,一般只需要具有听、讲、串查功能,而不需要控、并查功能,这样又会造成资源与功能的浪费。所以我们尝试用 CPLD来实现 GPIB 接口的听、讲、串查功能,不仅可拥有自主知识产权,节省了产品的成本,而 且具有很大的灵活性。

1.2 GPIB 控制芯片简介:

GPIB 也叫 HPIB,是一个数字化的 24 脚并行总线,由 16 条信号线和 8 条地线组成。这16 条信号线分为 8 条数据线、5 条控制线和 3 条握手线。8 条数据线:从 DIO1 到 DIO8,用 来传送命令、地址和数据;5 条控制线:分别为 ATN 线、IFC 线、REN 线、SRQ 线和 EOI 线,用来管理通过接口的有序信息流;3 条握手线:DAV 线、NRFD 线和 NDAC 线,用于控制设备之间消息字节的传送。发送消息方(源方)和接收消息方(受方)利用这 3 条握手线进行三线挂钩,以保证数据线上的消息(命令或数据)能准确无误地传送。

在 GPIB 系统中,把器件与 GPIB 总线的一种交互作用定义成一种接口功能。GPIB 标准 接口共定义了 10 种接口功能。

1.3 设计软件及设计芯片的选择

开发工具采用 ALTERA 公司的 MAXplusⅡ10.0。MAXplusⅡ开发工具是美国 Altera 公司 自行设计的一种 EDA 软件工具,它具有原理图输入和文本输入(采用硬件描述语言)两种输入手段,配备有编辑、编译、仿真、综合、芯片编程等功能。

Altera 公司是世界上从事可编程逻辑芯片生产的几家主要厂商之一,其 MAX3000A 系列可编程逻辑芯片速度快,容量大,性价比高。我们选用的 EPM3256ATC144-10,拥有 256个宏单元,144 个管脚,可自定义使用的管脚达 116 个,4.5ns 的传输延时完全能满足要求。

2. GPIB 控制器各个模块的设计

我们可以把整个系统划分为几个子系统。其中包括和微处理器接口的读写电路,与 GPIB母线通信的接口功能,以及内部寄存器。对每个子系统的设计也可以采用向下分解为模块级设计,这样在调试和组件系统时,不仅具有很强的灵活性,而且方便代码的调试以及利于代码的重利用。与微处理器接口的读写电路设计可以利用组合逻辑电路设计方法实现,其基本模块,如:译码电路,读写电路,相对比较成熟,在设计的时候只要对其基本功能深刻理解的基础上容易实现。与 GPIB 母线通信的子系统设计是本课题设计的重点也是难点,它不仅 需要对 IEEE488 协议有深刻的认识,而且在接口功能子集的选择上也有一定的要求。

2.1 微处理器(MCU)接口电路

微处理器(MCU)接口包括提供正确的寄存器访问地址的译码电路,以及连同 WE 和DBIN 一起构成的访问 GPIB 控制器的读写电路,NCS 用来选通地址译码。地址译码电路以及数据读写电路在数字电路设计中是最为成熟的电路,在此不作更多深入的阐述。值得注意的是 GPIB 控制器的读写信号并不是通常意义上的 RD 和 WR 信号,而是由 DBIN 和 WE 信 号完成。而且,对 13 个寄存器的译码也用的仅仅是 RS[0:2],这就需要和 DBIN 信号的配合来完成译码功能。

2.2 内部寄存器

GPIB 控制器(参考 NAT9914)的内部体系结构有 13 个寄存器,其中 7 个可写寄存器,6 个只读寄存器。它们都是八位的,其中可读寄存器有中断状态寄存器 0(ISR0)、中断状态 寄存器 1(ISR1)、地址状态寄存器(ASR)、总线状态寄存器(BSR)、命令通过寄存器(CPR)、数据输入寄存器(DIR);可写寄存器有中断屏蔽寄存器 0(IMR0)、中断屏蔽寄存器 1(IMR1)、地址寄存器(ADR)、辅助命令寄存器(AUXCR)、串行查询寄存器(SPR)、并行查找寄存器(PPR)、数据输出寄存器(CDOR)。在 GPIB 控制芯片的设计中对这十三个寄存器进行 详细的描述。本模块的设计采用图形方式,利用参数化模块库实现各个寄存器。

2.3 接口功能

GPIB 标准接口共定义了 10 种接口功能。每一个接口功能由一组或多组相互联系而又相互排斥的状态来定义。在一个时刻,一组互联又互斥的状态中必须有一个而且也仅又一个状态在起作用。在 IEEE488 协议中对接口功能的每一个状态还做了两方面的规定:

1.当某个状态在起作用时,在接口上可以或必须发送的消息;

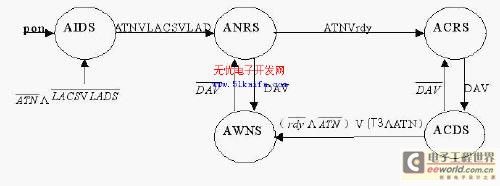

2.在什么条件下接口功能必须脱离某一状态而进入同一组状态的另一个状态;这些因素决定了状态的处理能力。接口功能状态图给出了全部状态以及从一个状态变迁到另一个状态一切可能的途径。由于篇幅的限制,下面以受方挂钩接口功能 AH 功能为例,来介绍功能模块的实现过程及原理。受方挂钩功能赋予器件保证正确地接收远地多线消息地能力。一个源方挂钩功能与一个或多个受方挂钩功能(分别含于各个器件中)的链锁挂钩序

列保证每个消息拜特的异步传递。受方挂钩功能可以延迟多线消息传递的开始或结束,直到 器件准备好继续参与传递过程为止。状态图如图 1:

图 1 AH 功能状态图

其状态转换的 VHDL 语言描述如下:

process(c_state,n_state)

begin AIDS<='0';ANRS<='0';AWNS<='0';ACDS<='0';ACRS<='0'; case c_state is

when s1=>AIDS<='1';NRFD<='1';NDAC<='1';

IF (ATN OR LACS OR LADS)='1' then n_state<=s2;

else n_state<=s1; end if;

when s2=>ANRS<='1';NRFD<='0';NDAC<='0';

IF ((ATN OR rdy) and not tcs)= '1' then n_state<=s3;

elsif DAV='1' then n_state<=s5;

else n_state<=s2; end if;

when s3=>ACRS<='1';NRFD<='1';NDAC<='0'; IF DAV='1' then n_state<=s4;

ELSIF (NOT ATN AND NOT rdy)='1' THEN n_state<=s2;

else n_state<=s3; end if;

when s4=>ACDS<='1';NRFD<='0';NDAC<='0';

IF ((ATN AND T3) OR (NOT ATN AND NOT rdy))='1' THEN n_state<=s5;

else n_state<=s4; end if;

when s5=>AWNS<='1';NRFD<='0';NDAC<='1'; IF DAV='0' then n_state<=s2;

else n_state<=s5; end if;

end case;

end process; 根据仪器的具体要求,由于大多数测试系统只要求被远控,并不要求控功能,而并查功

能在系统组建中属于可选项,很少用到,为了简化系统,设计中彻底去掉此两项功能。其他

功能模块包括:讲者功能(T)、听者功能(L)、源方挂钩功能(SH)、受方挂钩功能(AH)、服务请求功能(SR)、、远控本控功能(RL)、设备触发功能(DT)和设备清除功能(DC)。

其设计原理与 AH 相同,在这里就不做详细论述。

2.4 辅助命令译码器与多线消息译码器

1.辅助命令译码器通过对辅助命令寄存器 F0 到 F4 位的译码来生成辅助命令。 辅助命令共有 stactic 和 pulse 两种,即静态和脉冲两种信号,静态命令用电平的高低来表示。而动态命令则通过一个周期的方波脉冲信号来产生,要求脉冲命令至少在写完辅助命令寄存器后保持一个周期。我们通过 VHDL 语言来完成本模块的设计。

2.多线消息是处于相互排斥的编码集中但又公用一组信号线来传递的消息。在母线上,

每一时刻只能传递一条多线消息(一个消息拜特)。多线消息在远地消息译码单元内进行译码。 在这个译码单元,通过消息传递单元(DIO 线)来接收母线上的消息。消息译码单元仅在命令工作方式下(ATN=真)期间起作用。这样的接口消息可能是地址、通令、专令或副令之一。

在数据工作方式(ATN=假)中,数据线上携带器件消息,这时译码单元不起作用。在本 GPIB

控制器设计中,此模块还包含了地址比较器,这样可以得到内部状态机所需的与地址相关的 信号。用 VHDL 语言完成其设计,并例化成模块。

2.5 三态 I/O 通道

需要注意的是芯片数据通道中八条数据线与控制数据流向的八条控制线都是双向的,所以必须对 I/O 通道进行设置。实现双向总线,就需要使用可编程逻辑器件的双向口构造双向

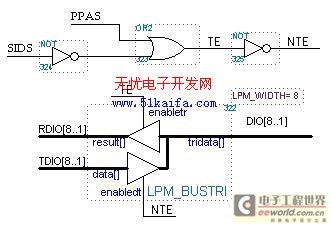

三态总线。三态总线的实现,需要使用三态缓冲器,实现高、低电平和高阻三个状态。基于ALTERA 公司的 CPLD 系列器件的特点,我们在设计的时候,内部避免使用双向的三态总线,将双向的信号分别直接引到外部。在外部设计双向三态总线。设计中采用图形方式输入,利用参数化模块库(LPM)实现。这种方法尤为清晰简便。如图所示:

图 2 三态总线的实现

在这里用 TE 信号来作为三态总线的方向控制信号。不考虑控功能,当本设备处于并行点 名状态,或者作为非命令数据的源接受方时,TE 信号为真,即 TE=PPAS+~SIDS。

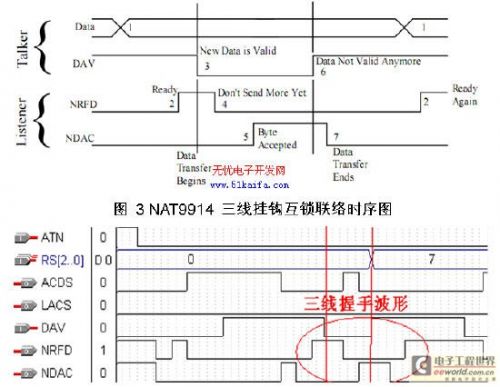

2.6 GPIB 总线中的三线挂钩技术的实现

三线挂钩技术是本设计的关键,因为在总线传输中,所有的命令和数据的传送都要通过三线挂钩来实现。

GPIB 总线中的三线挂钩技术(DAV、NRFD、NDAC)可以自动适应测试系统中各种不同器件的传输速率。源方作为讲者或者控者的器件,发 DAV 消息。受方作为听者的器件,发NRFD、NDAC 消息。三条握手线,DAV 线、NRFD 线和 NDAC 线,用于控制设备之间消息 字节的传送。发送消息方(源方)和接收消息方(受方)利用这 3 条握手线进行三线挂钩,以保证数据线上的消息(命令或数据)能准确无误地传送。

图 4 本设计三线挂钩仿真图

通过对系统的仿真,对比 NI 公司的 GPIB 控制器 NAT9914 数据手册上的三线挂钩的时序图可以看出,本设计成功地实现了三线挂钩的要求。

2.7 系统调试

调试是软硬件设计过程中必不可少的一环。最终程序通过 ByteBlaster 专用下载电缆下载EPM3256ATC144-10 芯片中,将下载好程序地 CPLD 取代原来系统中的 NAT9914 进行在线 调试。通过反复的试验,成功地实现了 CPLD 替代 GPIB 控制器的大部分功能。

3. 结 论

本文的创新点:采用低成本的 CPLD 器件替代了价格昂贵,且难以购买的 GPIB 控制芯片, 成功的实现了具有自主知识产权的 IP CORE,并且所有核心模块完全采用 VHDL 语言实现,能够在不同的开发环境上移植,可以根据不同的应用环境,对其进行进行剪裁和优化,不仅大大节省了成本,而且具有很大的灵活性。