文献标识码: A

文章编号: 0258-7998(2014)08-0034-04

中文引用格式:杨大伟,李健.基于FPGA的实时视频缩放算法设计实现[J].电子技术应用,2014,40(08):34-37.

目前视频缩放系统大多采用视频缩放的专业芯片设计,应用单一,灵活性差且成本较高[1]。视频图像是将丰富海量信息有效展示给大家的一种重要途径。图像的缩放是数字图像处理中的基本操作,在视频图像传输、电影制作等有非常广泛的应用。这项技术经常应用于匹配显示器的分辨率,完整地显示视频图像。本设计是在FPGA的平台上以RAM_FIFO架构应用双线性差值算法实现视频图像的任意比例的缩放,具有实行性好、处理速度快等特点。

1 双线性算法的硬件的可行性

1.1 缩放算法的选取

典型的线性缩放算法有最近邻域插值法、双性插值缩放算法和双三次插值缩放算法。最近领域插值法的计算复杂度较低,是以离待插值点最近的点的像素值作为待插值点的像素值。该算法计算量小,计算速度快,但是没有考虑周围像素点带来的影响,仅仅将距离最近的像素点的值赋给当前像素点,简单地将原图像放大到指定大小。同时该算法硬件可实现性好,但是容易产生锯齿状和马赛克现象,放大后的图像有较明显的失真。双线性插值算法中待插值像素点的像素值由该像素点相邻的4个像素点共同决定,由它们的像素值以及它们到插值点的距离加权求和得到。该插值算法能很好地解决最近邻域插值算法带来的锯齿现象和马赛克现象,显示效果较好,但该算法具有低通滤波效果,会使图像的边缘模糊[2]。双三次插值算法中待插值点的像素值是通过矩形网格中最近的16个采样点的加权平均得到,在这里需要使用两个多项式插值三次函数。该算法考虑了相邻16个像素点的直接作用以及各点像素值的变化率等因素,效果比前两种方式有大幅提升,改善了前两种方式的不足,但是该算法的计算复杂度也大幅提升。

综上所述,因为FPGA内部的逻辑资源有限,算法的复杂度越高,占用的逻辑资源就越多,硬件实现性差。因此综合考虑显示效果和硬件可实现性,实际工程中通常选用双线性插值缩放算法。

1.2 双线性差值算法原理

双线性插值的本质是在两个相互垂直的方向上分别进行线性插值,通过对两个变量的插值函数进行扩展得到[3]。如图1所示,设(u,v)是4个相邻点(i,j)、(i+1,j)、(i,j+1)和(i+1,j+1)所围成空间里的任意一点。在双线性插值中,(u,v)点的像素值是由周围4个相邻点的像素值加权求和得出,假设g(i,j)、g(i+1,j)、g(i,j+1)和g(i+1,j+1)分别为4个相邻像素点的像素值,则任意点(u,v)的像素值的求解过程如下所示:

g(i,j+u)=(g(i,j)-g(i,j+1))×u+g(i,j)(1)

g(i+1,j+u)=(g(i+1,j)-g(i+1,j+1))×u+g(i+1,j)(2)

g(i+v,j+u)=(g(i,j+u)-g(i+1,j+u))×v+g(i,j+u)(3)

2 双线性插值缩放算法的硬件实现

双线性插值缩放算法硬件实现总体框图如图1所示,该设计主要包括三大部分,分别为数据存储、系数产生以及整体控制。

图1 FPGA实现双线性插值算法的结构框图

2.1 数据存储

由于该算法最少需要两行数据才能进行运算,因此必须首先将输入的视频信号进行缓存,且至少缓存两行以上的数据,才能运用待插值点所在位置的相邻两行中4个像素点的像素值算出待插值点的像素值。本设计采用了RAM_FIFO架构的存储器进行数据缓存,该架构由多个双口RAM构成(本设计中设为N个),每个RAM至少能存储一行数据,将输入的第一行、第二行视频数据依次存入到第一个和第二个RAM中,依此类推。将接下来输入的数据存入到其余的RAM中,当N个RAM存满时,就停止往RAM中写数据[4]。当数据存满两行后,根据缩放比例计算出当前输出像素点映射到原图像中的坐标位置,取计算结果的整数部分和整数部分加1,然后从存储这两行的两个相邻RAM中,分别通过两个读端口同时读取相邻地址的4个像素点的像素值,通过这4个像素值计算待插值点的像素值。当RAM中的数据被读出以后,就可以往RAM中接着写新的数据。其操作过程与一般FIFO的先进先出相似。另外,不同分辨率的刷新率不尽相同,为了实现任意比例的缩放并保证缩放前与缩放后数据同步,需要使用外部存储器将输入数据进行帧存储,将输入/输出数据进行隔离,然后根据缩放算法的需要从外部存储器中读取数据进行缩放。

2.2 系数产生

在进行缩放算法时,首先得确定输入和输出的分辨率大小,通过输入和输出的分辨率确定缩放的比例,其计算如式(4)所示,式中xscale为水平方向缩放比例,yscale为垂直方向的缩放比例,inputxres、inputyres分别表示输入视频图像水平方向和垂直方向的像素点个数。outputxres和outputyres分别表示缩放后输出图像的水平方向和垂直方向的像素点个数。

双线性插值缩放算法的计算公式如下:

Dout=c1×x1+c2×x2+c3×x3+c4×x4(5)

式中,x1、x2、x3、x4分别为相邻4个像素点(左上、右上、左下、右下)的像素值,可从存储部分的RAM中读出。因此只需求得插值系数c1、c2、c3、c4即可算出插值点的像素值,其计算公式如下:

c1=u×v

c2=(1-u)×vc3=u×(1-v)c4=(1-u)×(1-v) (6)

式中,u、v分别表示待插值点与原图像中像素值为x1的像素点的水平距离和垂直距离。分别按照水平方向和垂直方向缩放比例计算出当前像素点在原图像中的位置,分别取其计算结果的小数部分即为u和v,假设待插值点在缩放后的图像中的坐标为(x,y),则u、v的计算公式如下:

u=x×xscale-[x×xscale]

v=y×yscale-[y×yscale] (7)

将式(4)带入式(7)可以得出u、v的值,再将u、v代入式(6)中即可求得插值系数。最后将插值系数代入式(5)即可算出待插值点的像素值。

2.3 整体控制

缩放算法设计实现的流程如图2所示,

图2 FPGA实现双线性插值算法的设计流程

整个缩放算法模块采用较高分辨率的像素时钟作为模块的主控时钟,采用输出分辨率的帧同步信号作为模块的复位信号。本模块带有裁剪功能,能够对局部图像进行放大,将数据存入RAM。本设计设定存满2行后开始进行缩放,缩放包括地址映射、插值系数计算、加权求和等过程,最后将数据取整输出,设计过程中需要保持插值系数计算和数据读取的节拍一致。

3 仿真与验证

本设计选用的主控芯片为Xilinx公司Spartan 6系列的xc6slx100-2fgg767[3],在ISE13.4开发平台上运用Verilog HDL对各逻辑模块进行设计,解码芯片型号为SIL1161,编码芯片的型号为CH7301,存储器DDR2型号为MT47H32M16-25E,测试显示器采用AOC 173P。

本设计输入为实时的DVI接口,输入分辨率为800×600,输出分辨率为1 280×1 024,相对应的缩放比例xscale=1.60,yscale=1.71,刷新率为60 Hz。此设计适合切屏,若输入的分辨率不同,则缩放比例、输入的横纵向点数均发生变化。当N=6时,适合全部输入,相应的参数不发生变化。

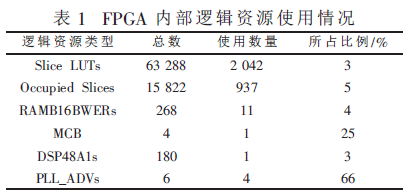

经验证得到本设计占用FPGA内部主要逻辑资源情况如表1所示,支持的像素时钟频率高达108 MHz,对应分辨率为1 280×1 024。

图3 缩放算法的仿真波形

图3为在设计过程中通过ISE自带仿真工具ISIM进行仿真得到的双线性插值缩放算法的仿真图。仿真图中,iSiI1161_one_odck_G为输入分辨率时钟,iSiI1161_one_

qe[23:0]为输入数据,calib_done 为DDR校准信号, clk_

scale为缩放核缩放时钟,c1[50:0]为加权系数,inputXRes[10:0]、inputYRes[10:0]为输入的横、纵向像素点数,xScale[17:0]、yScale[17:0]为横、纵向的缩放比例。

图4 图像切割放大拍摄效果图

图4为拍摄的实物效果图,图4(a)和4(b)将800×600的左半部份和右半部份分别放大到1 280×1 024。通过效果图可知,本设计方案测试效果良好,适合于大屏幕实时拼接使用。

本文首先对常用的视频图像缩放算法进行介绍,综合考虑硬件可实现性和缩放后显示效果,最终选择将双线性插值缩放算法在FPGA上进行实现。本设计采用RAM_FIFO架构作为该算法硬件实现的核心思想,设计主要包括数据存储、系数产生以及整体控制三大模块。硬件实现结果表明,该设计达到了预期效果,画面清晰稳定,无闪烁现象,能够实现任意比例缩放,并且具有剪切功能,能实现局部放大。双线性插值缩放算法处理会导致边缘稍有模糊,但满足人眼视觉需求,适合于工程应用。该设计能够为大屏拼接、视频的远程传输等高速视频信号处理提供必要的预处理装置。

参考文献

[1] 赵艳军,何其锐,施锡涛.基于DVI和FPGA的视频叠加器设计[J].电子技术应用,2011,37(6):31-34.

[2] 许录平.数字图像处理[M].北京:科学出版社,2007.

[3] Xilinx Inc.Spartan-6 family overview[EB/OL].(2010-03) [2014-04].http://www.xilinx.com.

[4] 徐文超,于意仲,柴耀龙,等.基于spartan-6 FPGA的DDR2控制器接口设计[J].数据采集与处理2012(27):167-171.

(收稿日期:2014-04-21)