文献标识码: A

文章编号: 0258-7998(2014)08-0038-03

随着半导体工艺技术的不断革新,功耗、存储、频率等技术瓶颈问题越来越突出,单核处理器已经很难继续通过提高时钟频率的方式来提高自身的性能。单核处理器在提高主频的同时也带来了功耗和发热量的问题。在这样的背景下多核并行处理器应运而生并且得到了快速发展。在这个过程中,设计的复杂度和核间通信的线延迟[1]成为了当前多核并行处理器设计的核心问题。多核并行处理器的各个核独立执行各自的程序,但各个核之间需要进行数据传递,路由器作为片上通信结构的核心部件,其设计性能直接影响整个片上网络的处理效率。本文基于多态并行处理器功耗和结构复杂度要求设计了近邻通信和远程通信两种通信机制,并对所设计的路由器进行了功能仿真和FPGA综合。

1 多态并行处理机结构

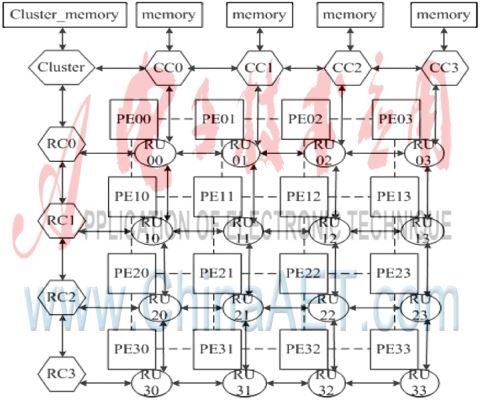

本文提出的多态并行处理器的处理单元具有单指令多数据(SIMD)和多指令多数据(MIMD)两种运行模式[2-3]。该结构兼有硬件的多线程管理和高效的数据通信机制。多态并行处理机结构如图1所示。

图1 多态并行处理机结构框图

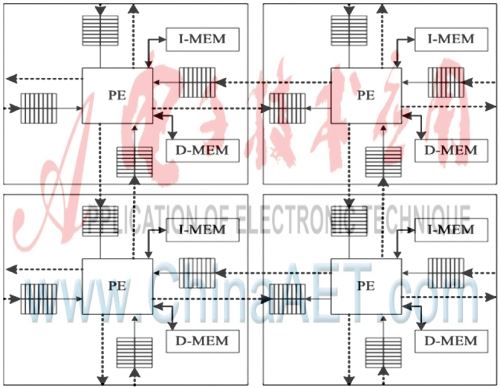

每个处理器核[4]由算术逻辑运算器ALU、线程管理器控制器TM、路由器RU(Router Unit)、邻接共享存储(Mn、Ms、Mw、Me)、数据存储D-men(Data Memory)和指令存储I-men(Instruction Memory)组成,每个基本处理单元如图2所示。

图2 基本处理器单元结构

2 设计与实现

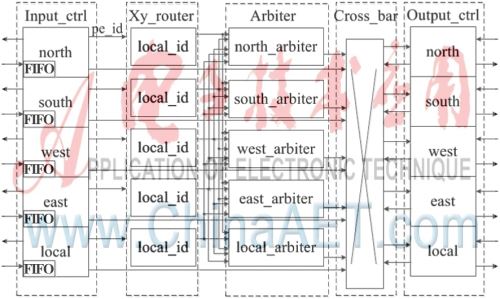

路由器的整体结构如图3所示。路由器可连接东、西、南、北4个方向的路由器和本地PE。

图3 路由器整体结构框图

(1)Input_ctrl模块:分别接收来自北、南、西、东、本地5个方向的数据请求,该模块将5个方向的数据打包成固定的格式存储在FIFO中。

(2)Xy_router模块:该模块采用XY路由算法实现,根据目标号和本地号判断数据包的传输方向。

(3)Arbiter模块:该模块采用简单的先来先到仲裁和设定固定优先级的仲裁机制实现。

(4)Cross_bar模块:通过选择完成数据和输出的交叉对应,并根据输出响应情况发送读数据包使能信号。

(5)Output_ctrl模块:该模块完成东、西、南、北4个方向的输出控制,以及本地输出的数据包解包功能。

多态并行处理器的数据通信机制包括近邻通信和远程通信。

(1)近邻通信机制

近邻通信机制采用共享存储的设计思想,每个处理单元(PE)都有北、南、西、东4个方向的共享存储,每个方向有两组存储,每组存储容量为8个字。近邻通信机制结构框图如图4所示。

图4 近邻通信机制结构框图

(2)远程通信机制

远程通信机制的结构如图5所示。远程通信完成远程数据传递和函数调用两种功能,远程数据传递包括PE之间点对点传送、PE与列控制器之间的数据传递两种方式;远程函数调用包括PE之间的远程函数调用、PE与行(簇)控制器之间的远程函数调用两种方式。

图5 远程通信机制结构框图

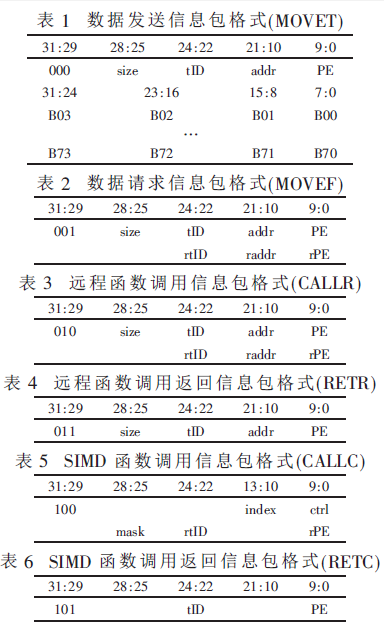

路由器处理的远程数据传输请求包括:

①远程处理器发送数据,来自远程处理器的MOVET信息包;

②远程处理器请求发送数据,来自远程处理器的MOVEF信息包;

③列控制器发送数据请求,来自列控制器MVT信息包;

④远程处理器发送多播请求,来自远程处理器MVT信息包。

路由器处理的远程函数调用请求包括:

①远程处理器发送函数调用请求,来自远程处理器CALLR信息包;

②远程处理器返回函数调用,来自远程处理器RETR信息包;

③行控制器和簇控制器返回函数调用,来自行控制器RETC信息包。

路由器相关数据包格式如表1~表6所示。

3 仿真验证及结果分析

为了测试路由器数据通信机制,采用System Verilog搭建包含行控制器RC、列控制器CC、簇控制器CLC、处理单元PE、线程管理器TM、路由器RU的整体仿真平台,使用ModelSim SE 10.1c进行仿真验证。

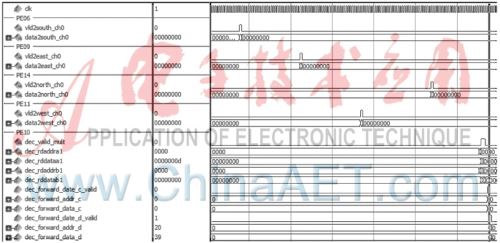

(1)近邻通信测试方案:选用PE10作为本地,PE06、PE09、PE14、PE11作为邻接,测试近邻通信的数据通路,测试结果如图6所示。

图6 近邻通信仿真时序图

从图6可以看出,PE06的vld2south_ch0有效,PE09的vld2west_ch0有效,PE14的vld2north_ch0有效,PE11的vld2east_ch0有效,表明与PE10相邻的4个PE分别送了一个数据给PE10进行运算,PE10执行乘法运算,相乘的结果39和609分别写回至地址20和22,近邻通信的功能正确。

(2)远程通信测试方案:选用PE00作为本地,测试调用远程PE10函数执行的数据通路,测试结果如图7所示。

图7 远程通信仿真时序图

从图7可以看出,本地PE00发出CALLR远程函数调用数据包请求给PE10,当PE10执行完后返回给本地PE00一个RETR数据包。图中只给出了CALLR数据包通路,CALLR/RETR数据通路正常。

综上所述,路由器的近邻通信和远程通信的数据通路是正确的,达到了预期的功能要求。

4 路由器性能分析

在Xilinx ISE14.4中选用型号为Virtex7 XC7V2000T-

fht1761-2的芯片对路由器进行综合。FPGA综合结果表明,本文设计的5路32 bit数据宽度的路由器综合频率为314.287 MHz,高于参考文献[5]中提出的5路16 bit数据宽度的路由器频率128.8 MHz和参考文献[6]提出的4路16 bit数据宽度的路由器频率309.02 MHz。综合报告如下:

Timing Summary:

Speed Grade: -2

Minimum period:3.182ns(Maximum Frequency: 314.287 MHz)

Minimum input arrival time before clock: 2.409 ns

Maximum output required time after clock: 1.126 ns

Maximum combinational path delay: 0.816 ns

图8所示给出了路由器在FPGA上的具体资源消耗状况以及资源利用率。综上所述,本文所设计的路由器具有速度和面积上的优势。

图8 FPGA资源利用率

本文提出了一种适用于多态并行处理机的数据通信和路由器结构的设计,完成了ModelSim软件功能仿真、Xilinx ISE14.4的综合,并在Virtex7 XC7V2000Tfht1761-2开发板中实现了验证。该设计结合并行处理机的需求设计了近邻通信和远程通信两种通信机制,提高了整个并行处理机的性能和资源利用率。

参考文献

[1] GRATZ P,SANKARALINGAM K,HANSON H,et al.Imple- mentation and evaluation of adynamically routed processor operand network[J].Proceedings of First International Sym posium on Networks-on-chip,IEEE Computer Society,2007,23(10):7-17.

[2] 李涛,肖灵芝.面向图形和图像处理的轻核阵列机结构[J].西安邮电学院学报,2012,17(3):43-46.

[3] 蒲林.多态并行处理器中的SIMD控制器设计与实现[J]. 电子技术应用,2013,33(11):53-59.

[4] 李涛,杨婷,易学渊.萤火虫2:一种多态并行机的硬件体系结构[J].计算机工程与科学,2014(2):191-200.

[5] 周东红.基于3x3NoC的路由器设计与网络性能分析[D].西安:西安电子科技大学,2011.

[6] 林世俊,张凡,金德鹏.分布式同步的GALS片上网络及 其接口设计[J].清华大学学报,2008,48(1):32-38.

(收稿日期:2014-05-10)

作者简介:

海虎,男,1988年生,硕士,主要研究方向:专用集成电路设计与系统集成。

李涛,男,1954年生,博士,教授,主要研究方向:计算机体系结构、计算机图形学。

杨婷,女,1989年生,硕士,主要研究方向:计算机系统结构与VLSI。