文献标识码: A

文章编号: 0258-7998(2014)11-0098-04

0 引言

MIMO-OFDM系统接收端检测算法中,最大似然检测(Maximum Likelihood,ML)算法具有最优检测性能,但其复杂度会随着天线数量和调制阶数增加呈指数增长。K-Best算法[1]克服了ML算法复杂度较高的缺点,并且能够取得与ML算法相似的误比特率(Bit Error Rate,BER)性能,因而受到广泛关注。

目前已实现的K-Best检测器主要分为专用集成电路(Application Specific Integrated Circuit,ASIC)[2-3]和现场可编程门阵列(Field Programmable Gate Array,FPGA)[4]两类。其中:参考文献[2]设计并实现吞吐率达到424 Mb/s的K-Best检测器。参考文献[3]中的半径自适应K-Best算法结合了深度球形解码和宽度球形解码的特点,以较低的功耗和硬件资源消耗达到了252 Mb/s的数据吞吐率。而后参考文献[4]改进了K-Best算法对路径度量的排序方法,并基于FPGA实现了K+-Best检测器,其数据吞吐率达到455 Mb/s。上述K-Best检测器均用于4×4天线系统中,并需设置较大的K值以获得较高的BER性能。

本文首先介绍了K-Best算法基本原理,然后在构建的2×4(2根发送天线、4根接收天线)MIMO-OFDM系统中仿真确定了K-Best算法中的K值,之后对K-Best检测器进行了硬件架构设计,最后采用FPGA对所设计检测器进行编程实现,给出检测器资源消耗和时钟频率等性能指标,并通过仿真验证了检测器的正确性。

1 K-Best算法分析

1.1 算法原理

假设在一个MIMO-OFDM系统中配置M根发送天线和N根接收天线(N≥M),则该系统的信号模型可以表示为:

y=Hs+n(1)

其中,s为M维发送信号,y为N维接收信号,n为N维加性高斯白噪声。信道矩阵H是复数域的N×M维矩阵。为避免复数运算带来额外硬件开销,可将信号模型(1)实数化分解:

R(y)I(y)=R(H) I(H)I(H) R(H)R(s)I(s)+R(n)I(n)(2)

其中,R(?驻)和I(?驻)分别表示复数?驻的实部与虚部。实数化后的信号模型由式(3)表示:

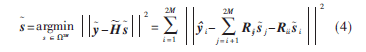

然后对信道矩阵实施QR分解,即H=QR,采用最大似然准则求解(3)可得:

其中,Q为2N×2N维正交矩阵;R为2N×2M维矩阵;y=QTy为2N维向量;为实数化后的星座点集合,例如采用4QAM调制时,星座集合为{-1,1}。

根据式(4)可得,K-Best算法的检测过程可以近似为图1所示的树形结构。定义参数K为每层保留节点个数,检测过程从第2M层开始,各层需计算欧式距离增量(INC),并与上一层累积欧式距离(PED)相加得到当前层的PED,然后将PED进行排序判决,保留其中较小的K条PED和其对应的K个节点,删除废弃节点的所有信息。当检测到最后一层时,从保留的K条PED再次选出最小累积欧式距离,并将其对应的节点作为检测结果。可以看出,K-Best算法中的K值对算法最终的BER性能和复杂度起着关键性作用。

1.2 K-Best算法K值的确定

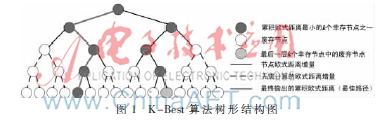

贝尔实验室提出的垂直分层空时结构(Vertical-BLAST,V-BLAST)是MIMO空间复用的典型代表[5],具有时延小、处理简单等特点。本文基于V-BLAST构建的2×4 MIMO-OFDM系统模型如图2所示。

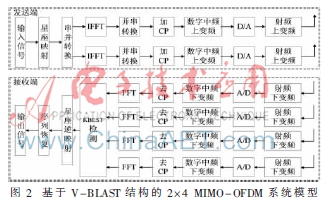

图3为在上述系统中对K-Best算法的BER性能仿真结果。从图中可以看出,当收发天线为4×4且分别设置K=1、2时,算法BER性能较差;只有当K=16时,算法BER性能才与ML算法性能一致(此时已遍历整个树形结构中的所有节点),故该复用方案下K值大小对算法BER性能影响很大。而当收发天线数为2×4,则只有K=1时算法BER性能较差,K=2时获得的BER性能与K=10和ML算法性能基本一致,故在后续的K-Best检测器FPGA实现中将K值设为2。

2 K-Best算法的硬件实现

2.1 QR分解模块

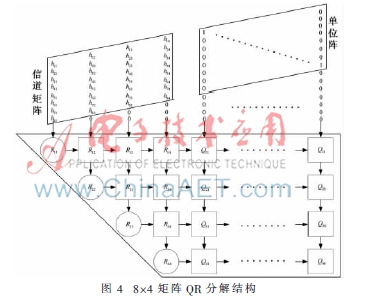

QR分解是K-Best检测算法的基础,采用CORDIC运算的脉动阵列是实现QR分解的常用结构[6]。图4是8×4信道矩阵QR分解结构,其中圆形是边界单元,正方形是内部单元,边界单元工作于CORDIC运算向量模式,将信道元素组成的向量旋转至x轴,实现元素消零并向右输出旋转角度,内部单元工作于CORDIC运算旋转模式,根据输入角度对向量进行旋转,并向下输出旋转后向量虚部和向右传递输入角度。左边4×4维上三角阵列用于计算R矩阵,其输入是列延时后的信道矩阵;右边的4×8维阵列用于计算Q矩阵,其输入是列延时后的单位阵,输出的4×8维矩阵经转置后得到Q矩阵。

2.2 乘加阵列模块

乘加阵列结构如图5所示,由2.1中QR分解得到的QT矩阵作为乘加阵列上端输入,在T1~T4时刻分别输入QT矩阵的1~4行(x=1,2,3,4),接收信号作为乘加阵列左端输入,在T1~T4时刻始终输入1~8。经过乘加阵列,在T1~T4分别输出1~4。

2.3 K-Best树形检测模块

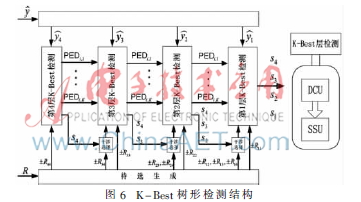

K-Best树形检测模块如图6所示,其中PEDi,1~PEDi,K表示第i层K条最小PED,s4~s1表示第4层到第1层的检测结果。由于在收发端配置2×4的天线,故K-Best检测的层数总共为4层。当调制阶数为M时,每个父节点有个子节点,故当K-Best中K≥时第4层只需进行INC计算,无需进行排序判决。其他3层均由干涉选择单元、累积欧氏距离增量计算单元(Distance Calculation Unit,DCU)与排序选择单元(Sorting and Select Unit,SSU)构成。

待选生成:由式(4)可知K-Best算法在每层均需计算多次![TI7L2O)R}_]61D4N0ERY0%O.jpg TI7L2O)R}_]61D4N0ERY0%O.jpg](http://files.chinaaet.com/images/2015/10/12/6358027454078500002419354.jpg) ,重复计算将导致过大的硬件资源消耗。因此在设计中采用待选生成结构将避免

,重复计算将导致过大的硬件资源消耗。因此在设计中采用待选生成结构将避免![TI7L2O)R}_]61D4N0ERY0%O.jpg TI7L2O)R}_]61D4N0ERY0%O.jpg](http://files.chinaaet.com/images/2015/10/12/6358027455266200005021211.jpg) 和Ri的反复计算,节省了硬件资源。待选集合在每层计算INC之前生成,由上层确定的j作为选择器输出各Rij,并与本层i扩展后得到的±Rii共同送入该层INC计算中。

和Ri的反复计算,节省了硬件资源。待选集合在每层计算INC之前生成,由上层确定的j作为选择器输出各Rij,并与本层i扩展后得到的±Rii共同送入该层INC计算中。

干涉选择:经上层PED排序判决确定的j送入干涉选择单元,对已生成的Rij待选集合进行选择,经加法器后的输出结果与i共同确定式(4)中![TI7L2O)R}_]61D4N0ERY0%O.jpg TI7L2O)R}_]61D4N0ERY0%O.jpg](http://files.chinaaet.com/images/2015/10/12/6358027458168700004555718.jpg) 。当调制阶数为M时,

。当调制阶数为M时,![TI7L2O)R}_]61D4N0ERY0%O.jpg TI7L2O)R}_]61D4N0ERY0%O.jpg](http://files.chinaaet.com/images/2015/10/12/6358027459425100008001857.jpg) 的计算次数达到

的计算次数达到![[A{K{W8GT_Z$`4]R54SZTBY.png [A{K{W8GT_Z$`4]R54SZTBY.png](http://files.chinaaet.com/images/2015/10/12/6358027460784300003037917.png) ,引入待选集合和干涉选择模块后,每层

,引入待选集合和干涉选择模块后,每层![TI7L2O)R}_]61D4N0ERY0%O.jpg TI7L2O)R}_]61D4N0ERY0%O.jpg](http://files.chinaaet.com/images/2015/10/12/6358027462650100008334308.jpg) 的计算次数减少到K次[7],调制阶数越高时计算次数减少得越明显。

的计算次数减少到K次[7],调制阶数越高时计算次数减少得越明显。

DCU单元:在式(4)中,每层![[A{K{W8GT_Z$`4]R54SZTBY.png [A{K{W8GT_Z$`4]R54SZTBY.png](http://files.chinaaet.com/images/2015/10/12/6358027464007000005127030.png) 条INC是由

条INC是由![TI7L2O)R}_]61D4N0ERY0%O.jpg TI7L2O)R}_]61D4N0ERY0%O.jpg](http://files.chinaaet.com/images/2015/10/12/6358027465072700001151526.jpg) 和±Rii进行减法操作后模平方得到的。然后与上层保留的K条PED对应相加得到本层的PED,之后将本层的PED送入SSU单元进行排序选择。

和±Rii进行减法操作后模平方得到的。然后与上层保留的K条PED对应相加得到本层的PED,之后将本层的PED送入SSU单元进行排序选择。

SSU单元:DCU单元中输出的![[A{K{W8GT_Z$`4]R54SZTBY.png [A{K{W8GT_Z$`4]R54SZTBY.png](http://files.chinaaet.com/images/2015/10/12/6358027466225400009778500.png) 条PED送入SSU单元进行排序选择操作,选出欧氏距离较小PED对应的K个节点作为本层的输出结果。排序选择采用“冒泡排序法”,对于

条PED送入SSU单元进行排序选择操作,选出欧氏距离较小PED对应的K个节点作为本层的输出结果。排序选择采用“冒泡排序法”,对于![[A{K{W8GT_Z$`4]R54SZTBY.png [A{K{W8GT_Z$`4]R54SZTBY.png](http://files.chinaaet.com/images/2015/10/12/6358027467061100008323450.png) 条PED,需要K路2K级的排序选择电路来进行判决。

条PED,需要K路2K级的排序选择电路来进行判决。

3 FPGA实现结果

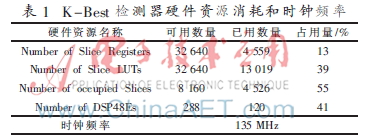

本设计利用Xilinx Virtex-5(XC5VSX50T)芯片对K-Best检测器进行FPGA实现。调制方式为4QAM,设置K=2。表1给出了检测器硬件资源消耗和时钟频率的性能指标。

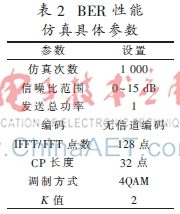

为了验证所设计K-Best信号检测器是否能够实现对信号正确的检测,将使用MATLAB、ISE和Modelsim软件对检测器进行行为仿真(Behavior Simulation)和BER性能仿真验证。具体仿真参数如表2所示。

首先将MATLAB中实数化后的星座点集合?赘、信道矩阵和接收信号存为Modelsim可读取的文件(由于输入数据需为定点数。考虑到溢出情况,将位宽设置为16位,首位为符号位,这里将MATLAB中的数据放大212倍,放大倍数越大,最终的精度越高,但占用的资源也就越多)。经ISE调用Modelsim读取所存文件,然后运行Modelsim对检测器进行行为仿真。整个过程完成了8×4信道矩阵的QR分解、矩阵Q与接收信号的乘累加、EDI和CED的计算以及CED的排序选择。数据输入端口分别为dr、dq、dq2、rec、s41和s42。其中dr用于存放8×4信道矩阵,dq和dq2存放8×8的单位阵,rec存放接收信号,s41和s42分别存放4QAM调制实数化后的星座点-1和1,计算完成后最终的输出结果为s4~s1(输出结果位宽为2 bit,首位为符号位)。

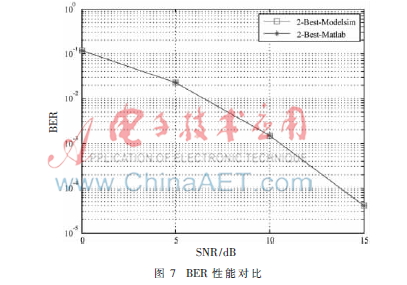

接下来将s4~s1存为MATLAB可读取文件(由于前面将数据放大212倍,故这里需要缩小相应的倍数),与直接用MATLAB进行K-Best信号检测的结果共同转换为复数,然后进行星座逆映射,并与发送数据进行序列比较,最终得到如图7所示的BER性能比较图。通过对比可以看出,二者的BER性能基本一致,这也反映了所设计检测器的正确性。

4 结束语

本文基于V-BLAST结构构建了2×4 MIMO-OFDM系统模型,并在该系统下对K-Best算法进行仿真,确定了算法的主要参数;而后根据确定的参数设计了K-Best检测器,介绍了检测器的各个模块硬件架构,并采用Xilinx Virtex-5芯片对检测器加以实现,给出检测器的RTL结构图、资源消耗和时钟频率等性能指标;最后文章通过MATLAB、ISE和Modelsim联合仿真验证了K-Best检测器的BER性能。

参考文献

[1] WANG K W,TSUI C Y.A VLSI architecture of a K-Best lattice decoding algorithm for MIMO channels[C].Proceedingsof IEEE International Symposium on Circuits and Systems,2002:273-276.

[2] WENK M,ZELLWEGER M,BURG A,et al.K-Best MIMOdetecting VLSI architectures achieving up to 424 Mb/s[C].Proceedings of IEEE International Symposium on Circuits and Systems,2006(4):1154.

[3] SHEN C A,ELTAWIL A M.A radius adaptive K-Best de-coder with early termination:algorithm and VLSI architec-ture[J].IEEE Transactions on Circuits and Systems I:regularpapers,2010,57(9):2476-2486.

[4] HEIDMANN N,WIEGAND T,PAUL S.Architecture and FPGA-implementation of a high throughput K+-Best detec-tor[C].Proceedings of Design, Automation & Test in EuropeConference & Exhibition,2011:1-6.

[5] 于全.战术通信理论与技术[M].北京:电子工业出版社,2009.

[6] HAENE S,PERELS D,BURG A.A real-time 4-stream MIMO-OFDM transceiver: system design, FPGA implemen-tation, and characterization[J].IEEE Journal on Selected Areas in Communications, 2008, 26(6): 877-889.

[7] 马小晶.MIMO-OFDM系统信号检测技术研究及VLSI实现[D].上海:复旦大学,2009.