梁茂,戴世通

(西安理工大学 工程训练中心,陕西 西安 710054)

摘要:研究了模拟、数字和射频混合电路便携式设备中PCB板电源传输系统(PDS)的设计方法,以及由电源传输系统引起的信号完整性问题。对PDS去耦网络中电容容量和数量做了定量和定性分析及研究,从电容提供电流速度这一角度给出了电容在PCB设计中布局的方法,以及电源传输系统引起的信号完整性问题的解决方法。该方法是经过大量智能便携式产品设计和测试总结与归纳后得出的,解决了设计和测试过程中出现的很多问题,也为新产品的开发在电源设计方面提供了新思路。

关键词:电源噪声;PDS;电源完整性

中图分类号:TN402文献标识码:ADOI: 10.19358/j.issn.1674-7720.2017.09.011

引用格式:梁茂,戴世通.便携式系统PDS分析与设计[J].微型机与应用,2017,36(9):34-37.

0引言

随着智能便携式设备的高速发展,当前智能便携式设备系统集成了数字、模拟、射频、存储器、传感器等各种功能模块,同时超薄智能便携式设备日益风行,使智能便携式设备的PCB板越来越小,集成度越来越高。系统向更高速度和更大功率发展的进程中,电源完整性(Power Integrity,PI)分析与设计已成为高速设计中的重中之重,PI直接影响着系统的各个方面。

当前智能便携式设备PCB普遍采用多层高速的平面电源总线结构,使电源分配网络的组成非常复杂,互联结构异常庞大。存在由封装引脚和印制线过长形成的寄生电感,焊盘到地、焊盘到电源平面和焊盘到印制线之间形成的寄生电容,通孔之间的相互影响,以及许多其他可能的寄生效应[1]等问题。图1是典型的运算放大器电路,图2是考虑寄生效应后的运算放大器电路。由于寄生效应的影响,到达实际器件的电源与地引脚的电压可能产生很大的波动。这种电源波动会导致两种问题:信号路径中的同时开关噪声(Simultaneous Switching Noise,SSN)和电源供电轨道坍塌[2]。SSN大多发生在并行总线中,由于共地造成相邻信号线之间的耦合增强,各信号线之间的耦合电感可能会导致非常严重的串扰。

这类噪声是由耦合电感(即互感)产生的。对于电源来说,当通过电源/地路径的电流变化时,特别是有大电流输出时,在电源路径和地路径的阻抗上将产生一个压降。当这个压降变得严重时,就会形成电源供电轨道坍塌。导致这一问题的原因之一就是电源系统功率得不到及时可靠的传输,也就是系统的PDS设计不当。因此,设计优良的PDS是智能便携式设备电源PI的关键所在,它决定整个智能便携式设备系统的可靠性和稳定性。优良的PDS应该满足以下两个要求:(1)在噪声可以接受的条件下,电流能得到及时可靠的传输;(2)保证智能便携式设备板上的其他模拟信号和射频信号的完整性,同时将智能便携式设备的电磁辐射控制在合理的范围内。

1PDS去耦网络设计

在解决电流不能及时传输这个问题前,首先要了解是什么原因导致电流不能及时传输。其实电流不能及时传输主要是由于智能便携式设备的PDS中存在多种阻抗不连续造成的。常见的阻抗不连续有电池PCB、PCB封装和封装裸芯片等。这些不连续使得PDS电流通路上的扩散电感增加,在PDS通路上就会产生很大的电源弹和地弹。在脉冲电流发生的过程中,这些电感感受到通过自身电流的变化,就会产生一个感应电压以阻止或减小电流的变化,这种反作用导致了电流的及时传输被延时。解决这个问题的最好办法就是在PDS上设计去耦网络,在电流不能及时传输给IC时,让去耦网络起到输送电流的作用。因此,必须有一个替代性的去耦网络在脉冲电流发生时为IC提供及时的电荷以确保电流的及时传输,否则IC将会工作失常。设计去耦网络最重要的参数就是去耦网络所应该提供的目标去耦时间,而这个时间就是PDS通路上由串联电感所引起的延时。去耦网络的目标延时TL[2]表达式为:

这个目标延时TL即为电感引入的电流延时。式中L为回路中的串联电感,I为平均电流,△V是电感引起电源的电压降。为了保持及时连续的功率传输,必须增加一个电容器网络提供瞬时电流以减小经过电感的电流。此时,要求电容器网络的最小去耦时间TC必须等于或大于功率传输延时:

TC≥TL(2)

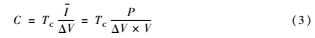

如果已知电容网络的去耦时间TC,就可以估算出去耦网络的总电容量[2]:

去耦网络电容值已可以准确估算,以此选择去耦电容的数量、种类和位置,使功率能够及时连续地传输。

首先分析如何确定电容的数量,即如何确定大电容和小电容的组合。假设充满电容器两端被短接时两端的电压降△V(△V是IC电源的噪声容限)的时间间隔是T△。对于给定的△V ,T△与电容的串联电感、串联电阻和电容值相关,随着容值的增加这三个参数都是单调递增[3]。从电容器的数据手册中可以查到,电容的容值越大封装越大,封装越大寄生电感就越大。因此,对于给定的电容量和噪声容限,使用多个小封装的电容器比一个大容量的电容器更能有效提高电容器的供电速度[4]。而在T△之后,去耦电容器就不能继续提供电荷,必须再次充电。否则,IC就会由于供电电压下降太多而不能正常工作。这时就需要下一级电容器为IC提供电流。依据工程实践中的2倍原则,去耦电容器最大的T△必须小于功率传输延时或者总去耦时间的一半:

![ZE8Y07XU%DWI__~E}]A@OSK.png ZE8Y07XU%DWI__~E}]A@OSK.png](http://files.chinaaet.com/images/2017/06/08/6363251404382805476624368.png)

同时下一级电容的T△小于当前级电容的T△,如下式:

TΔ(i)<TΔ(i+1)≤2TΔ(i)(5)

对于上述约束条件,通过示例可以很容易理解。假设最快的电容器(即第一级电容器)选为22 nF,那么第二级电容器就应该选为47 nF,第三级电容器为0.1 μF。这时应为47 nF电容的T△小于22 nF电容器T△的两倍。如果总的去耦时间为1 μs,那么最高级别电容器的T△应小于0.5 μs[5]。在上述分析的基础上可以得出如下结论:当一个电容器的频率响应开始下降时,另一个电容器的频率响应开始起作用,所以能在多个十倍频程范围内保持很低的AC阻抗。图3是电容器阻抗与频率的关系,给出了采用多个并联电容器的优点,在低频段大的电容器提供低阻抗的接地通路;在高频段小的电容器提供低阻抗的接地通路。图4是依据以上规则设计的某智能便携式设备在通话状态下实测核电源纹波波形,纹波完全满足该电源的噪声容限。

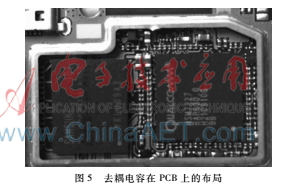

另一方面,去耦网络在PCB中相对于IC的位置也非常重要,这在大量的工程实践中已被证明。电容应按照其容量和封装依次由小到大靠近电源IC管脚放置。如图5所示。靠近IC一圈是封装最小的0201电容,然后是封装为0402的电容。

2防串扰的PDS返回路径设计

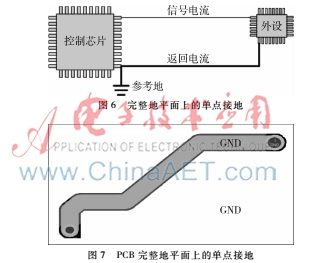

在智能便携式设备的PCB设计过程中,设计人员更多关注的是射频信号、时钟信号和音频模拟信号等,把所有精力都放在这些信号的设计上,想尽一切办法对这些信号实施保护隔离等措施,很少去关注信号实际的返回路径。这样的设计使同步开关噪声(SSN)通过PDS传播成为可能。尤其是电源/地平面常常作为其他信号的参考平面和返回路径,使设计不合理的电源/地平面就成为噪声传播的主要途径[6]。以GSM制式的手机为例,音频信号的返回路径必须重点关注,在一些极端情况下,甚至需要将音频信号的返回路径单独设计,以粗线的形式返回基带IC的音频GND引脚,再通过单点的方式接到整层的地平面上。如图6、图7所示为某智能便携式设备PCB上的单点设计中第四层完整地平面上的单点接地。

因此,避免SSN通过PDS传播,需要从以下三个方面设计PDS。

2.1设计完整的地平面以减少返回路径的不连续

对于理想的传输线而言,返回电流分布在信号电流正上方或正下方的参考平面上,信号电流和返回电流接近布线可减小整个回路的阻抗,从而使信号能高质量地传输,简言之,即电流总是以阻抗最小的回路流动[4]。对于便携式设备系统而言,高频率导致的高感抗使得回路电感变得更为重要,应该保证尽量低的回路电感,使返回路径连续。如图8所示,返回路径出现不必要的分割,使电源适配器的返回路径不连续,造成回路面积增大,形成返回路径的阻抗突变,返回电流在阻抗不连续的地方激起较大的电压波动。这在智能便携式设备系统上表现出的问题就是设备在做插适配器ESD测试时出现重启。解决类似不连续问题的最好方法是:尽最大努力减少PCB的表层布线,使表层GND平面完整、连续。大量的实践表明,完整的平面是最理想的返回路径,但在实际的设计中一些非理想的互连是很难避免的,这需要在设计中根据实际情况进行权衡。

2.2特殊电源返回路径避免与敏感信号回路重叠

在智能便携式设备PCB这种高密度的互连系统中,避免各个信号走线之间的串扰也是系统噪声控制的一项主要内容。在这种多走线互联结构中,走线之间的容性串扰和感性串扰可能导致信号的不完整[9]。当多条走线共用返回路径时,感性串扰将表现得非常突出,特别是当多条信号同时切换时,将导致严重的返回路径噪声,这种噪声严重时可导致系统间断性故障[8]。因此,像DCDC一类干扰非常大的电源,返回路径必须严格控制[7]。在智能便携式设备的研发过程中,开关频率串扰到射频载波上的情况非常普遍。这类问题主要从以下几个方面来解决:(1)DCDC电源在PCB的位置远离射频模块、音频模块和模拟器件等,可以将开关电源模块单独放在一个屏蔽腔内。(2)缩短返回路径,针对开关频率添加去耦电容旁路噪声,使开关噪声通过最短路径返回电源。(3)返回路径单点接地,避免与其他信号共用返回路径,最大程度地减小串扰的发生。

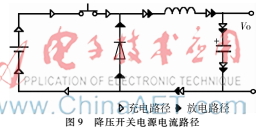

以图9的BUCK电路为例,分析开关电路中di/dt在电流传输路径中的危害及解决方法。开关闭合充电的过程中,通过开关、电感,然后是输出电容,最后又通过地流回输入电容。在放电过程中,电感迫使电流通过输出电容、地、续流二极管,然后流回电感。充放电的过程中会出现续流二极管路径电流不连续的情况,出现陡峭的边缘[8]。因此,理想的解决办法是将二极管的阳极直接联到输入电容的接地端,强制地电流连续流通,使GND回流电流等同于电感电流,显著降低充放电过程中通过续流二极管的di/dt变化。

2.3平面PDS设计

PCB电路向高密度发展的总趋势是采用平面电源总线,参考平面是PCB中完整的薄铜片,其在智能便携式设备PCB设计中作用极为重要。如果没有设计良好的参

考平面,就不可能获得高性能而又符合EMI要求的智能便携式设备产品。好的电源/地平面的设计能使便携式设备系统得到很好的功率传输[10],同时还起到提高信号完整性和控制EMI的作用。良好的平面PDS设计有以下优点:(1)为PCB上所有器件提供一个在很高频率范围内干净稳定的参考电压。(2)为高速信号提供一条低阻抗的返回路径,从而使高速信号传输成为可能,保证高速载波在PCB上传输。射频信号一般以微带线或带状线完成在PCB上的走线,返回电流位于信号线的正下方以获得最小回路阻抗。(3)为高速信号提供最小的返回路径,减小了回路面积和阻抗,从而减小回路的辐射。

总之,平面PDS设计为电流提供了一条低阻抗电流通路,这种低阻抗通路提高了功率传输的效率、高速信号传输的质量并减小了高速信号的EMI问题。

3结论

笔者以多年从事智能便携式设备PCB设计工作的基础上,从多个角度深入分析和研究了智能便携式设备PCB电源传输系统(PDS)的设计方法,提出了由PDS设计不当导致的电流不能及时传输和其他信号不完整问题的解决方法。同时本文所述的方法经过了大量实践检验,解决了大量工程实践中遇到的问题,如文中提到的感性不连续问题、PDS串扰耳机信号和开关电源供电不足等问题。该方法为智能便携式设备PCB板PDS设计和研究提供了一个新的方向。设计规则简单易懂。在设计之初,再结合Cadence仿真工具能得到更好的设计效果。该方法可以有效地运用于PDS的综合设计。

参考文献

[1] SWAMINATHAN M, EGEENGIN A.芯片及系统中的电源完整性建模与设计[M].李玉山,张木水,等译.北京:电子工业出版社,2009.

[2] 张木水,李玉山.信号完整性分析与设计[M].北京:电子工业出版社,2010.

[3] HOWARD J, GRAMAM M.高速数字设计[M].沈立,朱来文,陈宏伟,等译.北京:电子工业出版社,2004.

[4] Li Mike Peng.高速系统设计:抖动、噪声与信号完整性[M].李玉山,潘健,等译.北京:电子工业出版社,2009.

[5] LAI Q T, MAO J F, ZHANG M S. Compensation design for DC blocking Multilayer Ceramic Capacitor (MLCC) in highspeed applications[J]. IEEE Transactions on Components Packaging and Manufacturing Technology, 2011,1(5):742-751.

[6] ZHANG M S, MAO J F. Power noise suppression using powerandground via pairs in multilayered printed circuit boards[J]. IEEE Transactions on Components, Packaging and Manufacturing Technology, 2011,1(4):374-385.

[7] ZHANG M S, MAO J F. A new systematic method for the modeling, analysis, and design of highspeed power delivery networks by using distributed port[J]. IEEE Transactions on Microwave Theory Techmques, 2010,58(11):2940-2951.

[8] ZHANG M S, LI Y S, LI L P. Analyze and design highspeed power delivery networks using new multiinput impedances in printed circuit boards[J]. Microware Theory Techniquces.IEEE Transactions on, 2009,57(7):1818-1831.

[9] 刘婷婷,邓豹,韩嫚莉.电源完整性测试[J].微型机及应用,2015,34(8):29-31.

[10] 刘天翔,邹晓渔,戴钱坤.基于UCC29002的电源均流电路设计[J].电子技术应用,2012,38(1):48-50.