两大巨头,七篇论文,二维材料的新进展

2023-02-21

作者: semiwiki

来源: 半导体行业观察

逻辑缩放

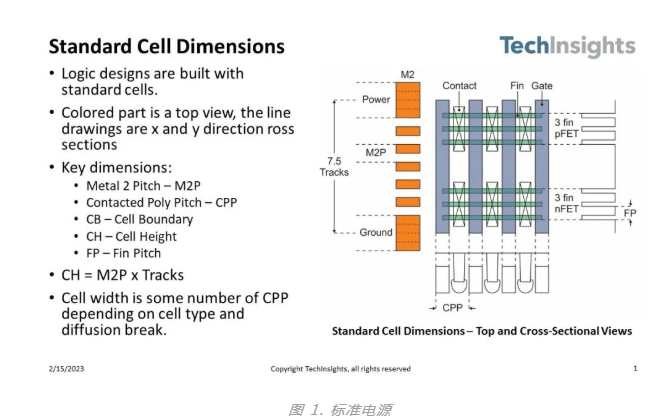

逻辑设计由标准单元(standard cells)组成,如果您要扩展逻辑以增加密度,则标准单元必须缩小。

标准单元的高度通常表征为M2P (Metal-2 Pitch) 乘以轨道(tracks)数。虽然这是一个有用的指标,但它掩盖了单元高度还必须包含构成单元的设备这一事实。图说明了一个 7.5 轨道标准单元,并在单元左侧显示了 M2P 和轨道,并且在单元右侧是相应器件结构的横截面图。

标准单元的宽度由一定数量的CPP(Contacted Poly Pitches ) 组成,其数量取决于单元类型以及如何处理单元边缘的扩散中断(diffusion breaks )。再一次说明,CPP 是由一个器件结构组成的,当 CPP 微缩时,它必须微缩。图 1 说明了 CPP,底部是器件结构的横截面图。

图 1. 标准电源

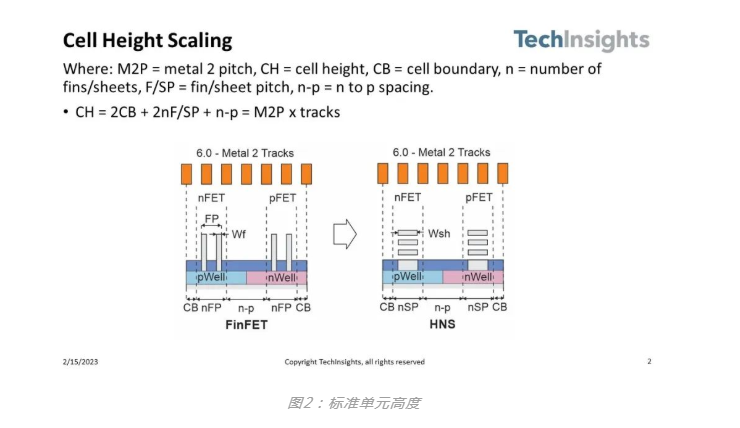

英特尔、三星和台积电都已从平面器件转向 FinFET,目前正处于向水平纳米片 (HNS) 过渡的初期阶段。目前三星正在量产HNS,英特尔和台积电分别公布了2024年和2025年的HNS量产目标。

图 2 说明了构成单元高度的器件结构和尺寸。

向 HNS 的转变提供了多种缩小单元高度的机会。HNS 可以用单个纳米片堆叠替代多鳍(multiple fin) nFET 和 pFET 器件,从而缩小器件的高度影响。Forksheet 和 CFET 对 HNS 的增强可以减少甚至消除 np 间距。

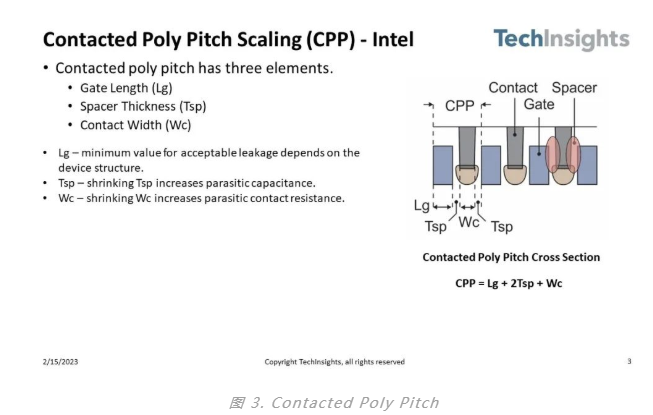

CPP 由栅极长度 (Lg:Gate Length)、间隔层厚度 (Tsp:Spacer Thickness ) 和接触宽度 (Wc:Contact Width) 组成,见图 3。

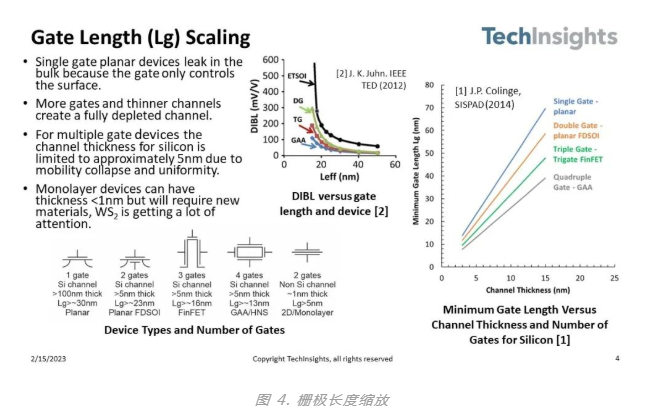

可以通过降低 Lg、Tsp 或 Wc 或三者的任意组合来缩小 CPP。Lg 受设备提供可接受泄漏能力的限制。图 4 说明了各种器件的 Lg 长度。

从图 4 可以看出,限制沟道厚度和/或增加栅极数量可以缩短 Lg。

所谓的 2D 材料由厚度小于 1nm 的单层材料组成,改善了对沟道的栅极控制并使 Lg 降至约 5nm。在这些尺寸下,硅的迁移率很低,使用具有更高迁移率和更高带隙的其他材料可以进一步减少泄漏。将 Lg 缩小到 ~5nm 的能力可以显著缩小 CPP,从而缩小标准单元。

二维材料挑战

过渡金属二硫族化物 (TMD:Transition Metal Dichalcogenides),例如 MoS2、WS2或 WSe2,已被确定为在单层厚度下具有高迁移率的感兴趣材料(硅在这些维度上具有较差的迁移率)。要实际使用这些材料,需要解决几个挑战/问题,这也是文章谈到的7篇论文中探讨的挑战/问题:

器件性能——用这些材料制造的器件是否真的能在短 Lg 下提供良好的驱动电流和低泄漏。

触点——2D TMD films是原子级别的光滑且难以形成良好的低电阻接触。

成膜——目前在蓝宝石衬底上使用高温 MOCVD 形成 2D films,然后将生成的薄膜转移到 300mm 硅晶圆上进行进一步处理。这不是一个实际的生产过程。

呈现的结果

在由英特尔CJ Dorow 等人撰写的论文 7.5 “Gate length scaling beyond Si: Mono-layer 2D Channel FETs Robust to Short Channel Effects”中,他们基于AI对材料性能进行了探索。

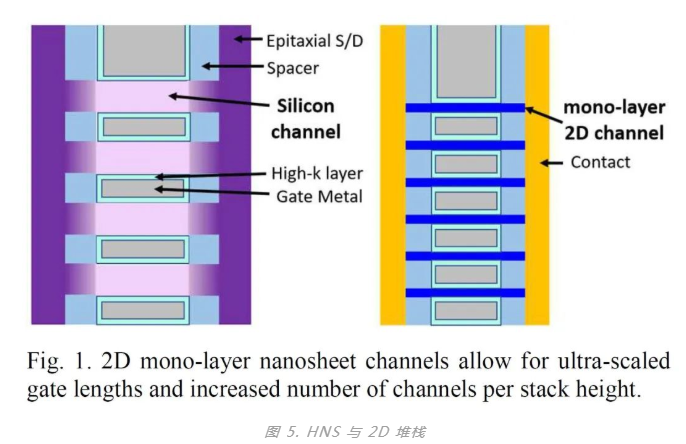

根据该文章介绍,基于 2D 材料的设备的最终目标是堆叠类似于 HNS 堆叠的 2D 层,但每个沟道更薄,从而实现更短的 Lg 和堆叠中的更多层。图 5 说明了差异。

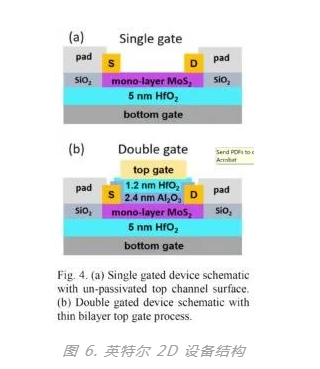

英特尔在背栅(back gate)上湿法转移了 MBE 生长的 MoS2薄膜,然后评估了带有背栅和附加前栅(front gate)的器件,并得出了源极-漏极距离为 25nm。图 6 说明了器件结构。

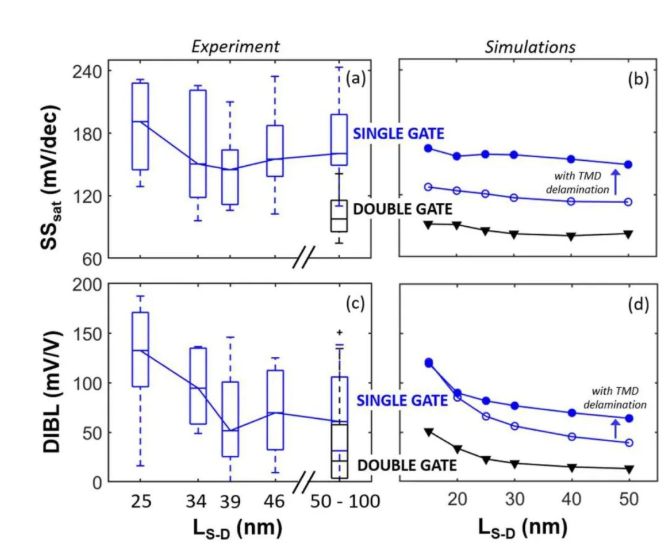

英特尔在他们的实验中遇到了一些分层问题,但能够通过实验确认他们的建模结果,并得出结论,双栅极设备应该能够缩小到至少 10 纳米,并具有低泄漏,见图 7。

图 7. 实验结果(左侧)和仿真结果(右侧)

在台积电Mahaveer Sathaiya等人撰写的论文 28.4 “Comprehensive Physics Based TCAD Model for 2D MX2 Channel Transistors”中, 他们讨论了 2D 设备的综合仿真模型,并针对 3 个数据集校准了该模型。能够准确地对 2D 设备建模将是该技术进一步发展的关键。

在台积电Ning Yang 等人撰写的论文 28.1 “Computational Screening and Multiscale Simulation of Barrier-Free Contacts for 2D Semiconductor pFETs”中, 。他们使用从头计算的方法来筛选 2D 设备的接触材料。

按照他们的计算,WSe2接触电阻的最佳报告实验结果为950 Ω·μm,在这项工作中,Co3Sn2S2预计能够达到接近量子极限的20 Ω·μm。此外,模拟设备预计会产生约 2 mA/μm 的状态电流。在蓝宝石衬底上进行溅射,然后进行高温退火工艺 (800 °C),结果表明可以生成具有预期化学成分和晶体结构的Co3Sn2S2。

在台积电的Ang-Sheng Chou等人撰写的论文 7.2,“High-Performance Monolayer WSe2 p/n FETs via Antimony-Platinum Modulated Contact Technology towards 2D CMOS Electronics”中,他们介绍了 Sb-Pt 调制触点(modulated contacts)的实验结果,该触点在 WSe2上实现了创纪录的接触电阻——pFET 为 750 Ω·μm,nFET 为 1,800 Ω· μm,并实现了约 150 μA/μm 的导通电流。这些结果不如论文 28.1 中的预测好,但代表了实验结果与模拟结果。

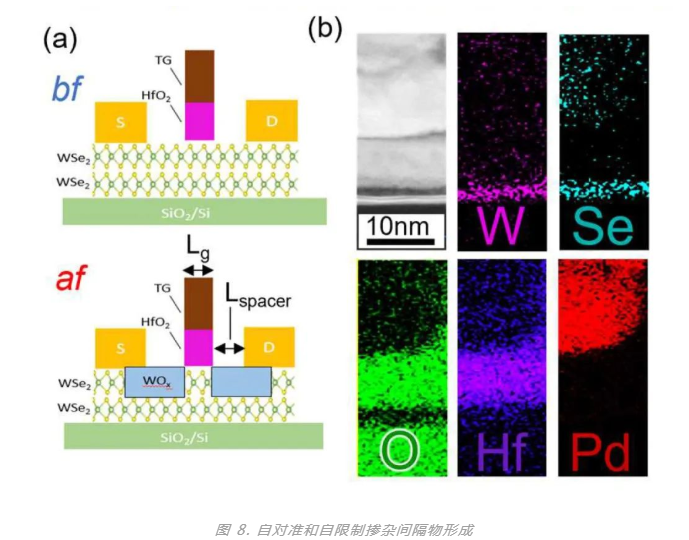

在台积电公司Terry YT Hung 等人的论文 7.3 “pMOSFET with CVD-grown 2D semiconductor channel enabled by ultra-thin and fab-compatible spacer doping”中,他们介绍了致力于生产类型的 pFET。许多 2D 材料工作是在肖特基二极管上完成的,但 MOSFET 具有较低的接入电阻。为了创建实用的 MOSFET,需要一个带有掺杂间隔物的 CVD 生长沟道。在本文中,通过用O2等离子体处理WSe2以产生 WOx作为掺杂剂来产生断带隙掺杂间隔物。该过程是自对准和自限制的,如图 8 所示。

CVD 生长的 2D 层仍然单独生长然后转移,但该过程的其他部分与生产兼容。该器件实现了最低的 Rc——约为1,000 Ω·μm 。

具有WSe2沟道和相对较高的 Ion > 10-5 A/μm 的晶体管,以获得良好的 SS < 80mV/dec。

在台积电Tsung-En Lee 等人撰写的论文 7.4 “Nearly Ideal Subthreshold Swing in Monolayer MoS2 Top-Gate nFETs with Scaled EOT of 1 nm”中,他们展示了在具有顶栅(top gate)的CVD 生长的MoS2上的 ALD 生长的~1nm EOT 的基于 Hf 的栅极氧化物,并实现了低泄漏和 68 MV/dec 的近乎理想的亚阈值摆幅。TMD 材料上的无针孔氧化物很难实现,这项工作显示出优异的结果。

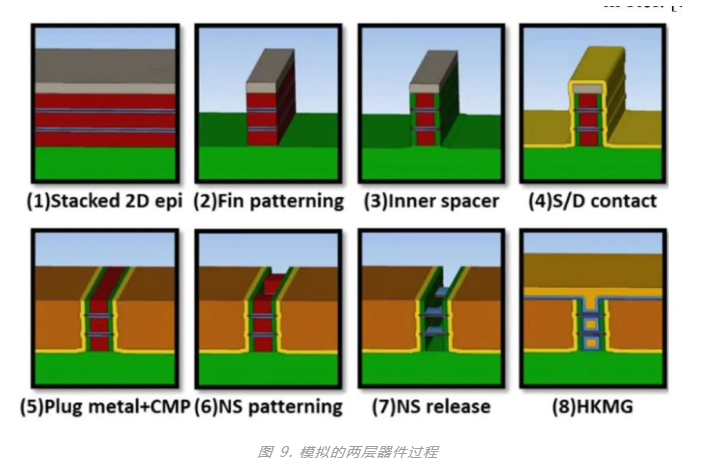

最后一篇论文34.5是台积电Yun-Yan Chung 等撰写的“First Demonstration of GAA Monolayer-MoS2 Nanosheet nFET with 410 μA/μm ID at 1V VD at 40nm gate length”,在文中,台积电公司的人展示了采用集成工艺流程制造的具有良好性能的MoS2器件。

图 9. 说明了两层设备堆栈的工艺流程模拟。

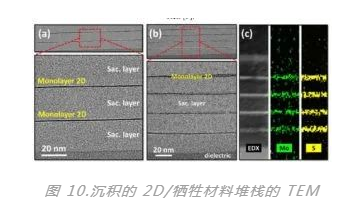

尽管本文仍需要进一步研究,但顺序沉积(equentially deposited)了2和 4 堆 TMD 和牺牲材料(sacrificial material )。

图 10. 显示了所得叠层的 TEM 图像。

二维材料和牺牲层的顺序沉积与薄膜转移相比是一种生产类型更多的工艺,而且成本也可能更低。

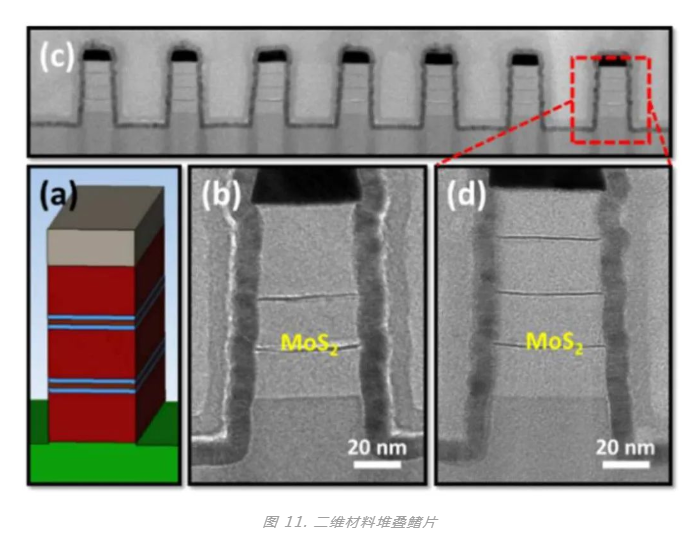

然后使用金属硬掩模将所得堆叠蚀刻成鳍状物。图 11. 说明了“fin”形成的结果。

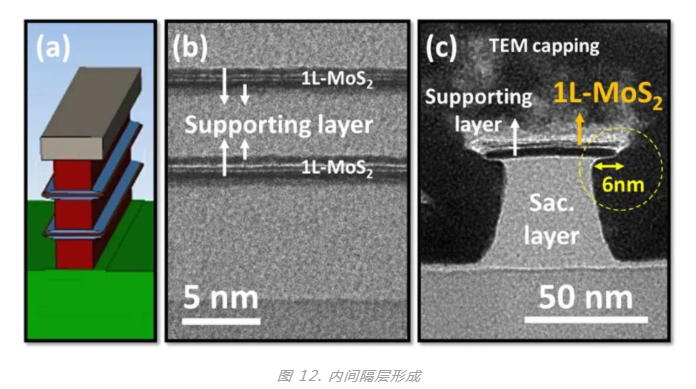

与水平纳米片堆叠的情况一样,需要内部间隔物来减少电容。为了形成内部间隔,需要额外的牺牲材料来防止 2D 层坍塌。图 12. 说明了内部间隔过程。

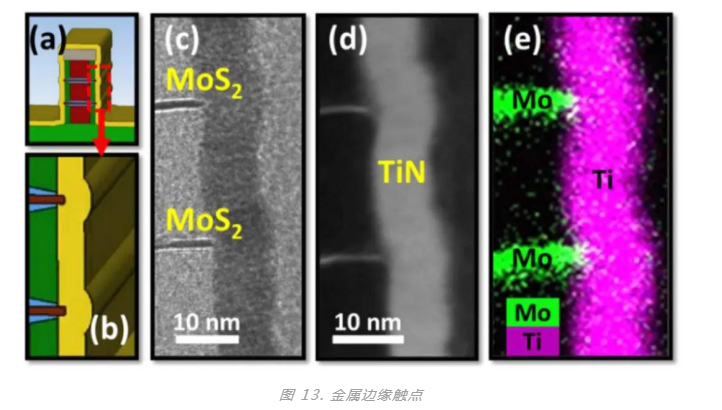

最后,形成金属边缘触点,并释放沟道。图 13. 说明了金属边缘触点。

由于在接触区和延伸区中没有掺杂,所得器件具有高接触电阻。如图演示了具有 40nm Lg 的 1 层器件,Vth 约为 0.8 伏,SS 约为 250 mV/dec,驱动电流为 410 μA/μm。

通过这 7 篇论文,说明了在 2D 设备方面取得的巨大进步以及两家领先设备生产商的兴趣水平。我最近完成的一些预测表明,二维 CFET 的逻辑密度可以达到目前最密集的生产标准单元的 5 倍。二维 CFET 可能是 2030 年代的技术,而不是 2020 年代的技术,这表明逻辑扩展远未结束。

参考资料

https://semiwiki.com/semiconductor-services/ic-knowledge/324910-iedm-2023-2d-materials-intel-and-tsmc/

https://semiwiki.com/semiconductor-services/ic-knowledge/324910-iedm-2023-2d-materials-intel-and-tsmc/