详解AMD Zen5锐龙AI 300内核布局图

2024-07-30

来源:快科技

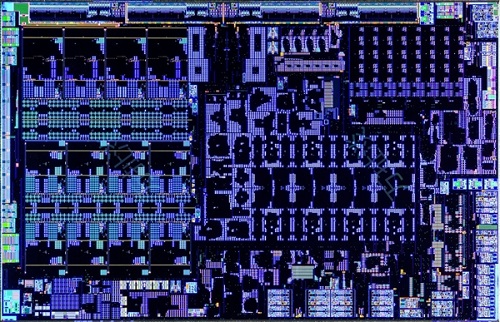

7月30日消息,AMD新一代锐龙AI 300笔记本已经陆续发布上市,有神通广大的网友公布了一张新U的内核布局图,更有大神逐一做了标注,CPU、GPU、NPU等各个单元模块清晰可见。

首先,Strix Point的核心面积约为18.71x12.06=225.64平方毫米,相比于上一代首次采用“同构大小核”设计的Pheonix2 15.01×9.06=135.99平方毫米,骤然增大了约66%,毕竟CPU、GPU、NPU的规模都大大扩充了。

图中左侧是CPU区域,可以看到上方四个Zen5核心、每核心1MB二级缓存、共享16MB三级缓存,下方分为两排的八个Zen5c核心、每核心1MB二级缓存、共享8MB三级缓存。

甚至每个核心内部的不同模块,也做了大致的猜测,包括分支预测、指令预取、整数执行、浮点单元、载入与存储、缓存等。

虽然也是“大小核”,但是Zen4/Zen4c、Zen5/Zen5c都是完全相同的架构、IPC性能、ISA指令集,只是做了一些三级缓存、性能的精简,系统和软件调度无需考虑其差异,这也Intel的异构大小核完全不同。

另外,Zen5、Zen5c各自的三级缓存理论上可以彼此共享,但会增加延迟,因此AMD通过Windows系统调度,尽可能地让每一部分核心只访问自己的三级缓存。

靠右侧是GPU区域,可以看到八组WGP,每组有两个CU单元,一共16个(1024个流处理器),还能看到512KB一级缓存、2MB二级缓存、原语单元与光栅化单元、四个渲染后端(RB+),以及右方的多媒体引擎、上方的显示引擎。

右上角是NPU区域,包括8×4布局的AI核心模块、8个内存模块,以及NPU控制逻辑单元与缓存,占了相当一部分面积。

在芯片的边缘部分,排列着DDR5-5600/LPDDR5X-7500内存控制器与PHY物理层、显示物理层、USB4/3/2物理层、PCIe 4.0 x4物理层,等等。