基于UVM的时间敏感网络交换芯片的验证架构设计

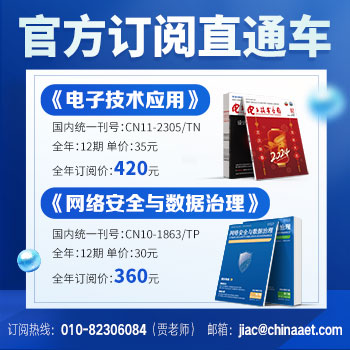

电子技术应用

赵伟,陈三伟,方震,何泉初,王雨亭

中国电子科技集团公司第五十八研究所

摘要: 基于UVM验证方法学、自动化比对和覆盖率驱动的验证思想,构建了一个用于时间敏感网络(TSN)交换芯片的系统验证架构。该架构采用分类和流水处理数据报文方法,结合流量检测、时间槽检测和数据报文自动化比对方案,成功支撑TSN业务系统验证方法落地,保证了系统验证完备性。芯片回片经测试满足商用需求,再次论证了验证架构的完备性。

中图分类号:TN402 文献标志码:A DOI: 10.16157/j.issn.0258-7998.245682

中文引用格式: 赵伟,陈三伟,方震,等. 基于UVM的时间敏感网络交换芯片的验证架构设计[J]. 电子技术应用,2024,50(12):36-40.

英文引用格式: Zhao Wei,Chen Sanwei,Fang Zhen,et al. UVM-based verification architecture design for TSN time-sensitive network switch chip[J]. Application of Electronic Technique,2024,50(12):36-40.

中文引用格式: 赵伟,陈三伟,方震,等. 基于UVM的时间敏感网络交换芯片的验证架构设计[J]. 电子技术应用,2024,50(12):36-40.

英文引用格式: Zhao Wei,Chen Sanwei,Fang Zhen,et al. UVM-based verification architecture design for TSN time-sensitive network switch chip[J]. Application of Electronic Technique,2024,50(12):36-40.

UVM-based verification architecture design for TSN time-sensitive network switch chip

Zhao Wei,Chen Sanwei,Fang Zhen,He Quanchu,Wang Yuting

No.58 Research Institute of China Electronics Technology Group Corporation

Abstract: In this paper, a system verification architecture for time-sensitive network (TSN) switch chip, which is based on UVM, automatic comparison and coverage-driven verification thinking, is designed. This architecture adopts the method of classifying and pipelining packets, combined with traffic detection, time slot detection and packets automatic comparison scheme, successfully satisfies the implementation of the TSN system verification method, finally ensures the system verification completion. Chip test results meet commercial requirements, once again demonstrates verification architecture completeness.

Key words : UVM;time-sensitive network;TSN;switch chip;system verification

引言

当今网络系统中,时间敏感网络(Time-Sensitive Networking, TSN)协议已成为满足实时通信需求的关键技术。TSN协议通过提供精准的时间同步、低延迟和高可靠性,被广泛应用于工业自动化、汽车电子和音视频传输等领域。作为TSN协议的核心设备,时间敏感网络交换芯片的功能和性能正确性尤为重要。

本文提出了一种基于UVM的时间敏感网络交换芯片的验证架构,旨在满足TSN交换芯片验证方法落地,确保TSN交换芯片功能和性能正确。该验证架构结合了分类和流水处理数据报文、记分板自动比对、流量检测、时间槽检测和覆盖率驱动的验证思想,确保了验证的全面性和准确性。通过验证架构的设计与实现,能够有效进行TSN业务的验证实施,最终确保验证目标圆满达成。

本文详细内容请下载:

https://www.chinaaet.com/resource/share/2000006245

作者信息:

赵伟,陈三伟,方震,何泉初,王雨亭

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

此内容为AET网站原创,未经授权禁止转载。