AMD 2nm Venice CPU细节曝光

2026-01-15

来源:芯智讯

1月14日消息,根据Wccftech报导,继AMD 在CES 2026 披露了采用台积电2nm制程的EPYC Venice 处理器部分信息之后,近日“X”平台用户@hms1193 曝光了更多官方尚未公开的Venice构架细节。

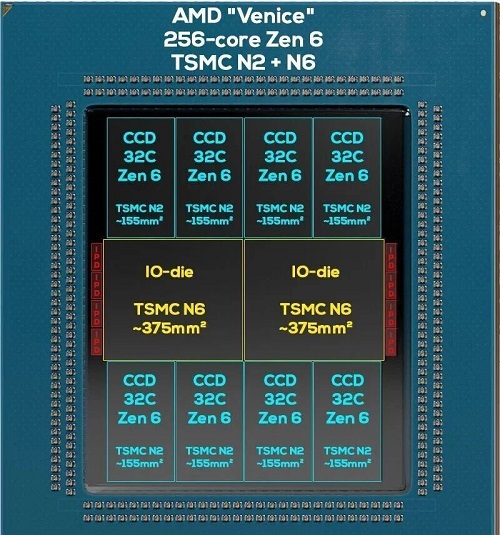

此前披露的信息显示,“Venice”CPU将基于2nm制程,拥有 8 个大型 Zen 6 核心控制单元 (CCD) 和两个 I/O Die,以及包含管理控制器的微型芯片。AMD承诺, EPYC Venice CPU 的性能和效率将提升 70% 以上,线程密度也将提高 30% 以上,内存带宽也将高达1.6TB/s。该芯片还将推出标准的 192 核“Zen 6”版本,包含 16 个 CCD,每个 CCD 包含 12 个 Zen 6 核心,以及 768 MB 的 L3 缓存。

而最新的爆料称,Venice还有基于Zen 6C核心的版本,最高也是256核心。在设计上,AMD通过更高密度的计算晶粒(CCD)与全新的双I/O Die 构架,试图同时应对高核心数与AI 服务器对I/O 带宽快速提升的需求。

其中,每颗Zen 6C CCD 可容纳32颗核心,较前一代Zen 5C 的16核心设计直接翻倍,N2制程下面积为155mm²,AMD 能在仅使用8颗CCD 的情况下,达成更高的256核心配置。

缓存配置同样是升级重点。每颗Zen 6C CCD 内置128MB L3 缓存,使整颗处理器的L3 缓存总容量高达1GB。这在多核心服务器负载中,这有助于降低对主内存的依赖与延迟。

在制程工艺方面,负责运算的CCD 采用台积电2nm(N2P)制程,以追求极致性能;而负责I/O 的I/O Die 则维持6nm制程。

值得注意的是,EPYC Venice 改采双I/O Die 构架,两颗I/O Die 总面积达750mm²,远超前代的单一I/O Die 设计。这意味着内存信道、PCIe 与CXL 扩充能力将大幅提升,更有利于支持AI 服务器中GPU 与高速网络设备的密集部署。