基于DSPBuilder的数字下变频器的FPGA设计

2008-05-07

作者:马 涛1,陈 娟2, 单 洪1

摘 要: 数字下变频是软件无线电" title="软件无线电">软件无线电的核心技术之一。阐述了多级抽取结构数字下变频器" title="下变频器">下变频器的原理,介绍了系统级设计的新方法,利用系统工具DSPBuilder给出了数字下变频器的FPGA设计方法,讨论了各个抽取滤波器的性能要求。用双边带调幅信号(DSB)作为激励信号" title="激励信号">激励信号,给出了具体的仿真验证" title="仿真验证">仿真验证。

关键词: 软件无线电 数字下变频 FPGA DSPBuilder

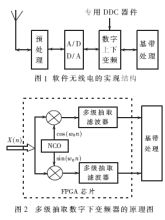

软件无线电是以具有开放性、通用性、可扩展性的最简单硬件为平台,通过加载各种应用软件来实现各种无线电功能,借以适应不同用户、不同应用环境的需求。但由于受A/D转换器和DSP器件硬件水平的制约,目前软件无线电大多采用数字上、下变频技术来实现,其结构如图1所示。在下变频的具体实现中,常见的是使用专门的DSP芯片(如Harris公司的HSP50214系列),但专用芯片串行执行指令的特点使得其在高速信号处理中无法满足设计需要。高性能大规模可编程逻辑器件的出现,使得在FPGA中用软件实现数字下变频成为可能,并且FPGA丰富的片内资源和并行的处理速度已经使其成为设计的首选。图2为多级抽取数字下变频器的原理框图。

本文利用系统工具DSPBuilder对多级抽取结构的数字下变频器的FPGA设计进行具体讨论和分析,并进行仿真验证。从仿真结果可以看出,本设计可以满足软件无线电中宽带数字解调的要求。

1 系统级设计新方法

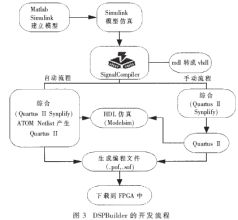

数字下变频器的传统设计方法是将系统设计和具体实现分隔开来进行,因此存在开发复杂、设计周期长和开发费用昂贵等缺点。本文采用DSPBuilder系统级工具进行设计,从系统设计到具体实现做出了很多革新。它架构在多个软件之上,把系统级和RTL级两个设计领域的设计工具结合起来,最大程度地发挥了两种工具的优势,并且提供了一个从MATLAB/Simulink直接到FPGA硬件实现的设计接口。DSPBuilder极大地简化了硬件实现流程,同时提供了系统仿真测试功能,使利用FPGA设计并实现数字下变频器更加灵活,更容易开发。其开发流程如图3所示。

2 数字下变频器的结构

数字下变频器的功能是从输入的宽带数字信号中提取所需要的窄带信号,并将其下变频为数字基带信号。在多速率信号处理中,数字下变频器的基本结构如图4所示。

在图4中,A/D输出的已调信号X(n)经过正交混频和D倍抽取后得到正交基带信号I(m)、Q(m)。正、余弦信号由数控振荡器(NCO)产生。抽取器的第一级抽取因子往往很大,在总的抽取因子中所占的比重也非常大。由于积分梳状滤波器(CIC)无需乘法运算,可以实现高速滤波,所以CIC滤波器一般用在第一级。CIC滤波器在选择抽取因子时,应注意避免通带衰减过大,同时也要避免抽取后通带混叠过大。一般情况下,抽取后通带的相对带宽小于1/8即可。

由于CIC滤波器的通带特性和抗混叠特性不是很好,在CIC滤波器和FIR滤波器之间有多级半带滤波器(2倍抽取器),但级数不宜过多,通常在1~5级之间。若FIR滤波器的通带相对带宽很小,则只需一级2倍抽取器即可;若FIR滤波器的通带相对带宽比较大,则2倍抽取器的级数也就要多一些,但不宜超过5级。

FIR滤波器作为整形滤波器放在最后一级,一般不作为抽取器。 总的抽取因子为D=D1·D2·D3。其中D1、D2、D3是可变的,以适应不同的信号要求。

3 数字下变频器的FPGA设计

3.1 数控振荡器的FPGA设计

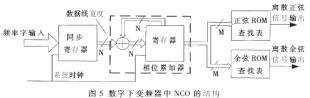

NCO采用直接数字频率合成(DDS)技术来实现。NCO主要由相位累加器和正、余弦ROM查找表构成(见图5)。相位累加器根据输入的频率控制字的不同,输出相位序列作为ROM的寻址地址,ROM里存放的是输出波形的一个周期的幅值编码。这样,寻址时就能从ROM中得到一系列离散的幅度码。

在数字下变频器中,需要一对正交的正、余弦信号进行正交解调。因此,NCO需要两个ROM查找表(正弦和余弦)。

为提高速度,相位累加器采用流水线技术,即把在一个时钟内要完成的逻辑操作分成几步较小的操作进行设计,并插入几个时钟周期来提高系统的数据吞吐率。而查找表正弦信号一个周期的离散值利用matlab命令来实现。整个设计是采用DSP Builder工具在Simulink中建模实现的。

3.2 积分梳妆滤波器的FPGA设计

积分梳状滤波器由积分器和梳状滤波器级联" title="级联">级联而成。为了加大阻带衰减,通常采用多个积分滤波器级联。若采用N个积分滤波器级联,其幅频响应为:

式中,D为抽取因子,N为级联数。具体实现结构如图6所示。

CIC滤波器有两个参数:D、N。通常情况下,根据要求首先确定抽取因子D,由于CIC滤波器的阻带衰减与带内容差跟N成正反比,设计时阻带衰减与带内容差应折中考虑,CIC滤波器的级联数不宜过多,一般以5级为限。

在进行硬件设计时,每一级必须保留足够的运算精度,否则可能引起溢出错误或运算精度的降低。因此,数据必须采用2的补码,寄存器中所存数据值的范围应大于、等于整个滤波器最后输出的最大数值范围。为了节省资源,可根据输出结果的误差,对各级数据进行截位或舍位,以减少寄存器的位数,但是数据位数的减少不能随意。

3.3 FIR滤波器的FPGA设计

本文的FIR滤波器采用直接型结构,主要由移位寄存器、乘法器和加法器组成。其设计思想是利用DSPBuilder模块直接实现乘法器和加法器。基于乘、加的设计比较简单,系统工作速度较高,但占用的资源很大,因此只适合于速度要求较高、阶数较小的滤波器设计。

利用DSPBuilder模块设计的FIR滤波器很容易进行功能扩展,输入数据的位宽可以根据实际的需要进行调整。要实现高阶的滤波器,只需要将滤波器级联,然后输出数据相加即可。

3.4 半带滤波器的FPGA设计

半带滤波器(HBF)特别适合于实现2的幂次方倍的抽取,且计算效率高、实时性强。半带滤波器是频率响应满足阻带宽度与通带宽度相等、通带波纹与阻带波纹相等的一类FIR滤波器。

半带滤波器的设计方法与FIR滤波器的设计方法相同,只是在设计半带滤波器时必须确保三点:①滤波器的阶数N为奇数;②滤波器的通带误差容限(δP)与阻带误差容限(δS)相等;③滤波器的通带宽度与阻带宽度相等。

4 仿真验证

4.1 激励信号的产生

激励信号采用双边带调幅信号(DSB)。DSB信号由待调制信号与余弦信号相乘来得到。利用正交解调,同相分量即为解调信号。

激励信号的采样速率为80MHz,信道带宽BS为100kHz,则所需的最大抽取因子为:

式中,r为数字滤波器的矩形系数,取r=2。

在这里,设整个数字滤波器的通带波纹为1dB,阻带衰减为60dB,输出端的采样速率为0.8MHz。

4.2 各级抽取滤波器的性能指标和幅频响应

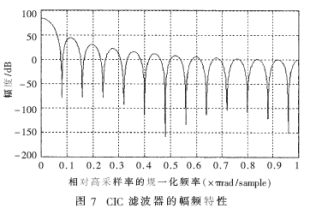

CIC抽取滤波器的通带上限频率为100kHz,抽取后的相对带宽取1/32,则抽取因子D应满足的条件是D≤80M/(100k×32)=25,通过对通带衰减和混叠特性的权衡,取N=3,D=25。通过MATLAB可画出它的幅频特性,如图7所示。

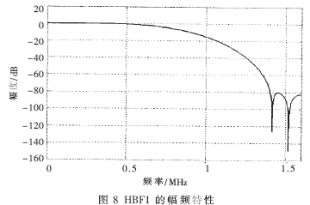

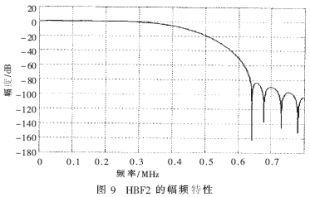

半带滤波器需要完成4倍的抽取,需要两级级联。由半带滤波器自身的特点可知,只要知道其阻带衰减和通带上限频率就可以将它设计出来,其参数如下:HBF1的通带相对带宽1/32,即通带上限频率为3.2MHz/32=100kHz;HBF2的通带相对带宽为1/16,即通带上限频率为1.6MHz/16=100kHz。阶数分别为15和19。根据这些参数可画出它们的幅频特性如图8和图9所示。

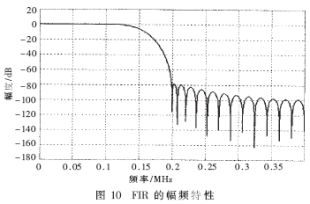

FIR滤波器在这里不作为抽取器,通带上限频率为100kHz,阻带下限频率为200kHz,阻带衰减为80dB。设计后阶数为53阶,其幅频特性图如图10所示。

4.3 多时钟设计

由于数字下变频器中存在多速率的转换,因此每个模块都需要不同的时钟作为驱动,所以要采用多时钟设计。设计中采用DSPBuilder和Quartus环境中自带的锁相环模块pll,它最多可以提供六个不同的时钟输出。由分析可知,系统中至少包含有80MHz、3.2MHz、1.6MHz、0.8MHz四个时钟。

4.4 具体的仿真验证

4.4.1 Simulink系统仿真

在Simulink建模后,便进行系统仿真,其中部分仿真波形如图11~图16所示。

4.4.2 RTL级功能仿真

在转化为VHDL语言后,便在ModelSim中进行功能仿真,波形图如图17和图18所示。

对比系统仿真与功能仿真可以看出,输出的结果是一致的。

利用FPGA实现数字下变频器,不仅在处理速度和带宽上比专用DDC优越,而且FPGA固有的硬件可重构特性更加适合软件无线电的开放平台。本文采用DSPBuilder系统工具,从系统建模到FPGA的具体设计都在一个环境中完成,方便了系统的更改和扩展,使得设计更加灵活、便捷。

参考文献

1 焦 庆,陶 然.宽带中频数字接收机的FPGA实现. 电子产品世界,2004;(5)

2 Wajih A, Abu-Al-Saud and Gordon L. Stüber:Modified CIC Filter for Sample Rate Conversion in Software Radio Systems. IEEE SIGNAL PROCESSING LETTERS, 2003

3 潘 松,黄继业,王国栋. 现代DSP技术.西安:西安电子科技大学出版社,2003

4 杨小牛,楼才义,徐建良.软件无线电原理与应用. 北京:电子工业出版社,2001

5 杨小牛,陆安南,金飚译.宽带数字接收机. 北京:电子工业出版社,2002