引言

数码管可显示简单的字符和数字,由于其价格低廉、性能稳定、显示清晰、亮度高、使用电压低、寿命长,在工业生产、交通运输、仪器仪表及家用电器等场合得到广泛应用。然而,开发基于NiosⅡ的嵌入式系统时,Builder开发工具中没有提供现成的数码管显示IP核,这使设计者工作量增加。这里把数码管控制器设计为一个共阴极(或共阳极)7段数码管动态显示IP核,并给出此核的一个参考驱动程序。在系统设计中,可根据实际需求,把此核直接例化成1~8个共阴极(或共阳极)数码管显示控制器,控制1~8个共阴极(或共阳极)数码管工作,实现IP核重用,减少电子设计者的工作量,从而提高设计效率。

2 LED数码管结构及驱动显示方式

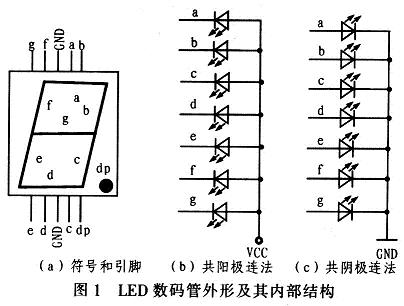

根据发光二极管的个数可将数码管分成7段数码管和8段数码管,8段数码管比7段数码管多一个用于显示小数点的发光二极管;根据内部连接形式可将数码管分成共阳数码管与共阴数码管,图1为数码管的外形及其内部结构图。

常用的数码管显示驱动方式有静态驱动与动态驱动两种,静态驱动方式的主要特点是,每个数码管都有相互独立的数据线,并且所有的数码管被同时点亮;而动态驱动方式则是所有数码管共用一组数据线,数码管依次被点亮,因此,动态驱动显示方式每个数码管都要有一个点亮控制输入端口。为节省I/O端口,此设计采用动态显示方式,所有数码管动态显示控制时序,全部由FPGA器件产生。

3 数码管动态显示IP核设计

根据数码管动态显示方式的工作原理,可把数码管动态显示控制器设计成IP核,包括任务逻辑设计、寄存器文件设计和Avalon接口设计3部分。

3.1 任务逻辑设计

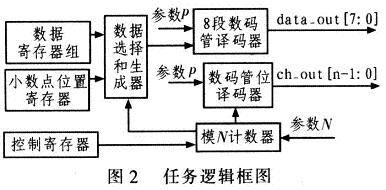

任务逻辑实现IP核的基本功能,是IP核设计的关键。任务逻辑产生数码管动态显示时的各种控制时序,并根据控制时序的先后顺序,读取寄存器文件中的数据,并送至数码管译码器进行译码,图2是任务逻辑框图。

由图2知,所设计的IP核主要由模N计数器、数据选择和生成器、8段数码译码器、数码管位译码器和寄存器文件组成。模N计数器可根据参数N,产生N个状态,其状态数与数码管个数相等,每个状态依次分给第一个数码管;数码管位译码器的作用是根据模N计数器的值(状态)产生数码管位选信号。按顺序依次点亮数码管,而参数P的值表示数码管的类型(共阳或共阴),当P为高电平时,控制共阴极数码管工作;P为低电平时,控制共阳极数码管工作。

数据选择和生成器用于根据计数器的状态选择数据寄存器组的数据,还可生成要显示的数据信号,包括数字与小数点两种,当小数点位置寄存器的值与计数器的值相等时,点亮小数点位;7段数码管译码器对输入的信号译码产生译码数据,该数据的最高位是小数点数据,低7位是字符显示数据。

3.2 寄存器文件设计

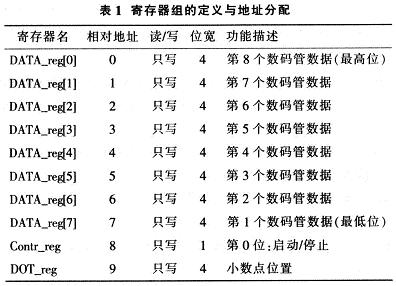

为实现任务逻辑单元与外界数据交换,要定义一组寄存器,称为寄存器文件,并为这些寄存器分配地址。根据图2,在此IP核中共定义10个寄存器,表1为其功能和地址偏移量。

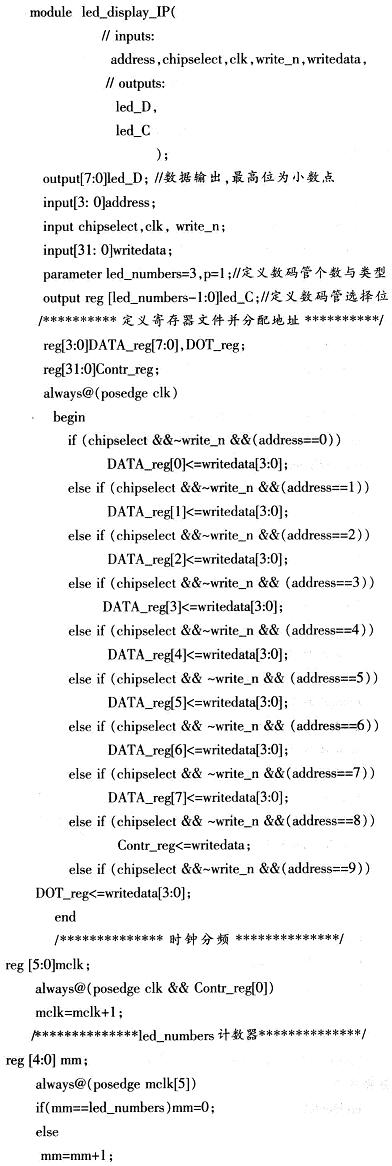

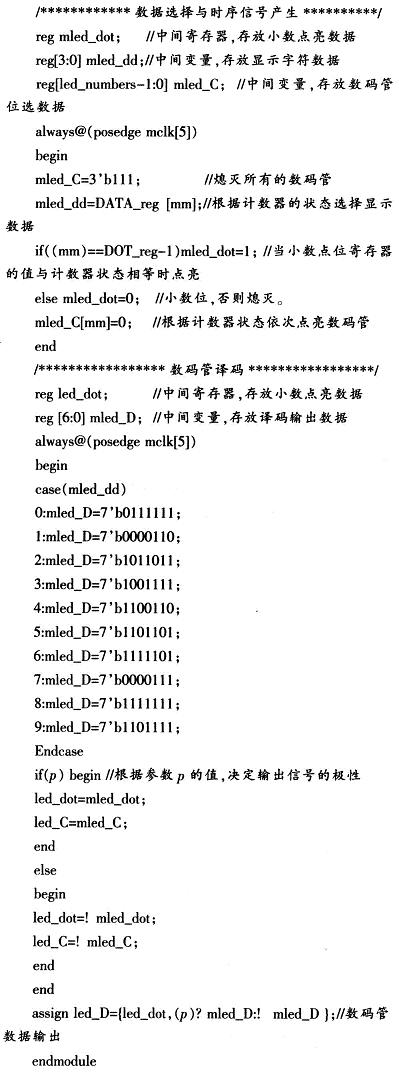

3.3 数码管动态显示IP核Verilog HDL程序编写

用硬件描述语言Verilog HDL编写程序完成设计。

4 基于Nios II的软件驱动程序设计

把所设计的IP核加载到嵌入式系统,打开Nios II EDS,在Ahera提供的集成开发环境(IDE)中,为IP核编写驱动程序。

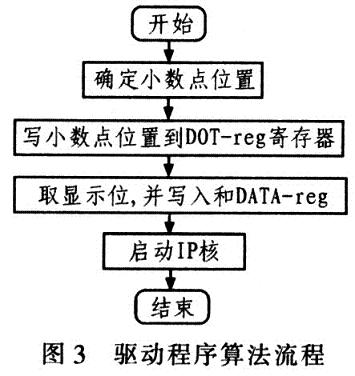

首先点击new菜单建立工程应用文件,然后选择一个空的工程模板(Blank Project),并在此工程模板中编写相应程序,其驱动程序的算法流程如图3所示。

5 结论

数码管是电子设计中应用较多的元器件。用于显示系统的运行状态和简单的字符,以便提升系统人机界面的效果。为减轻设计者的工作量,实现软核重用,设计8段数码管动态显示IP核,并给出此核的一个参考驱动显示程序。此核根据设计需要,可例化1~8个共阳极(或共阴极)数码管控制器,成功控制1~8个数码管工作,大大提高设计效率。测试结果表明,此核工作可靠、稳定,可直接应用于工程实践中。