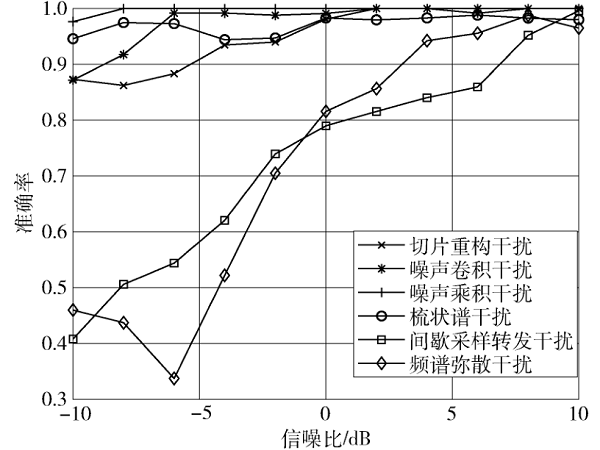

基于多域特征的雷达有源干扰信号智能识别[通信与网络][通信网络]

发表于:2025/11/14 下午3:59:22

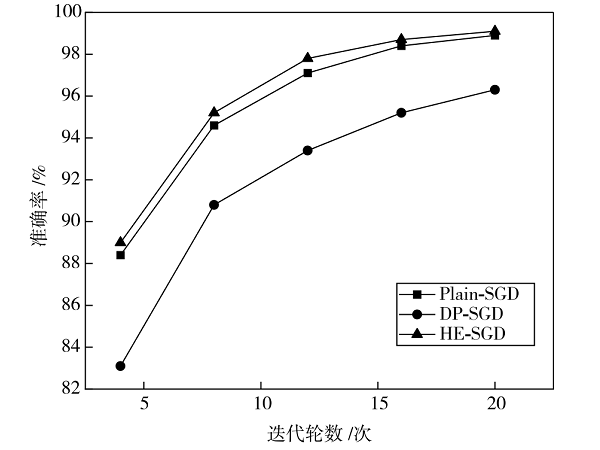

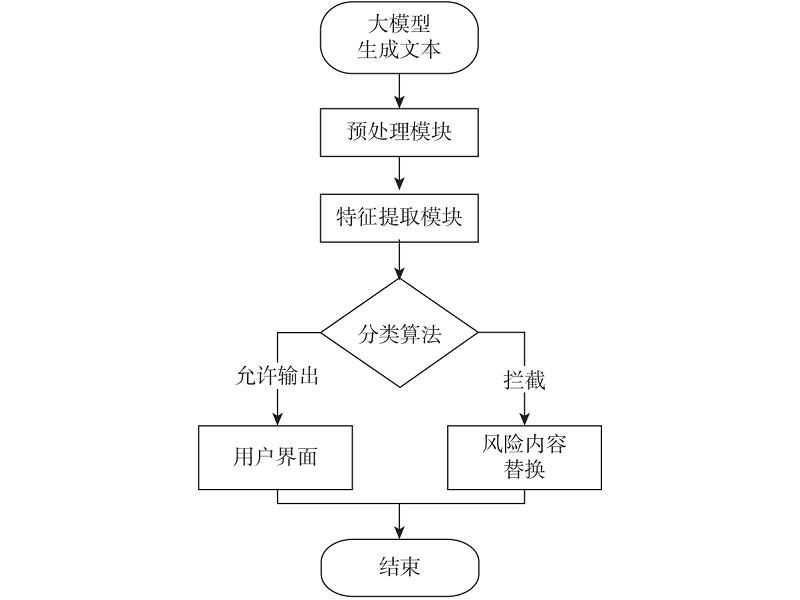

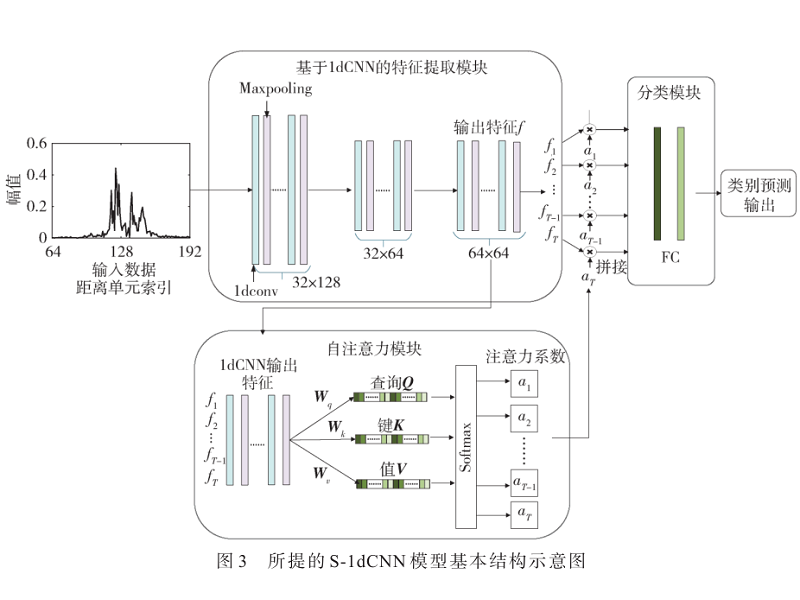

基于自注意力1dCNN的雷达目标识别方法及教研系统设计[人工智能][通信网络]

发表于:2025/11/14 下午3:52:05

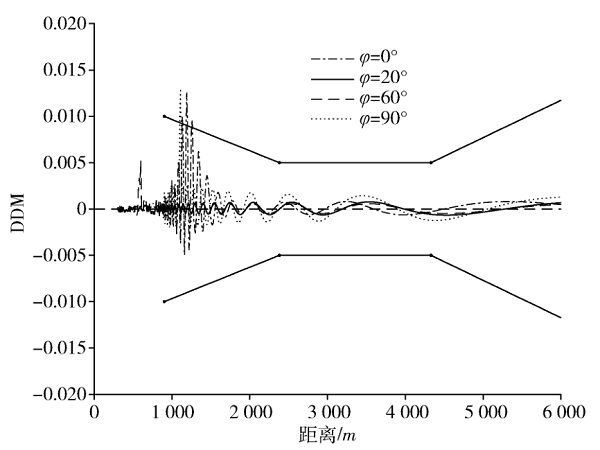

航向信标辐射场中障碍物影响分析与布局优化[模拟设计][航空航天]

发表于:2025/11/14 下午3:44:01

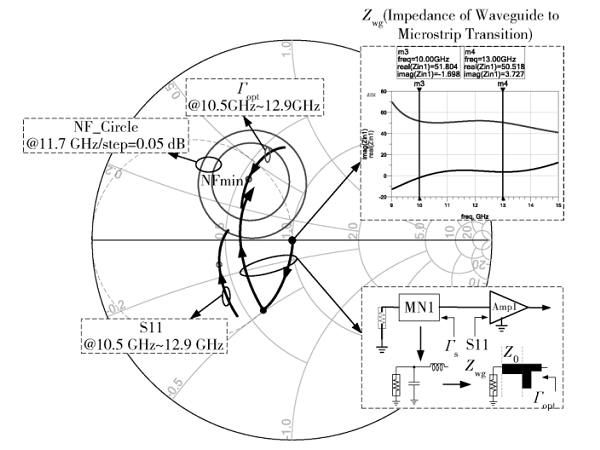

一种Ku频段高性能低成本低噪声放大器[微波|射频][通信网络]

发表于:2025/11/14 下午2:59:01

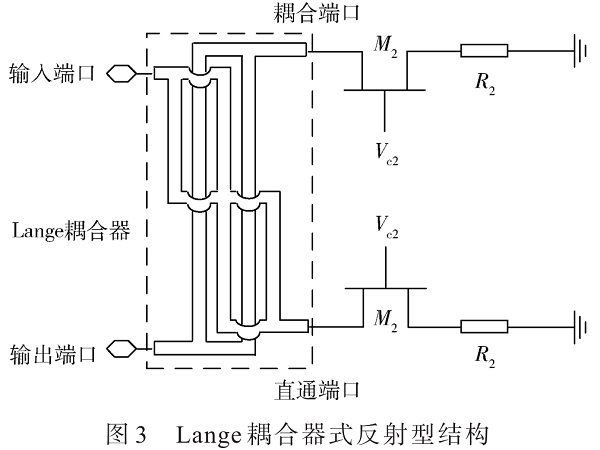

12~30 GHz高精度低附加相移数控衰减器设计[微波|射频][通信网络]

发表于:2025/11/14 下午2:50:01

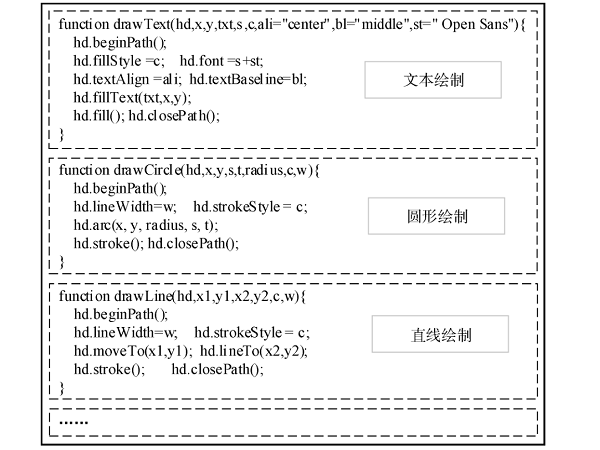

基于ESP32嵌入式Web服务器的手机化仪表设计[嵌入式技术][物联网]

发表于:2025/11/14 下午2:25:31

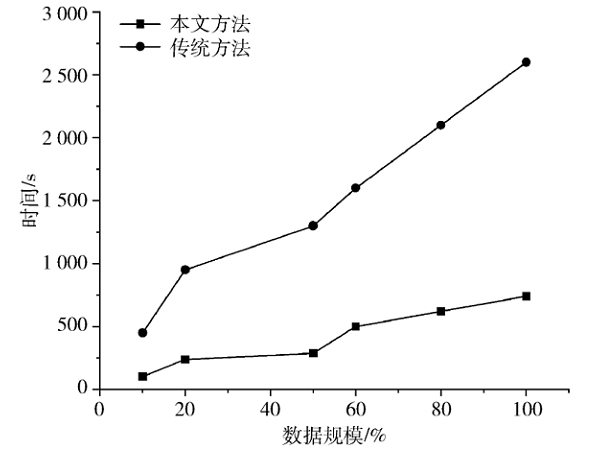

基于聚类的HTTP/HTTPS协议资产发现[通信与网络][其他]

发表于:2025/11/14 下午2:16:32

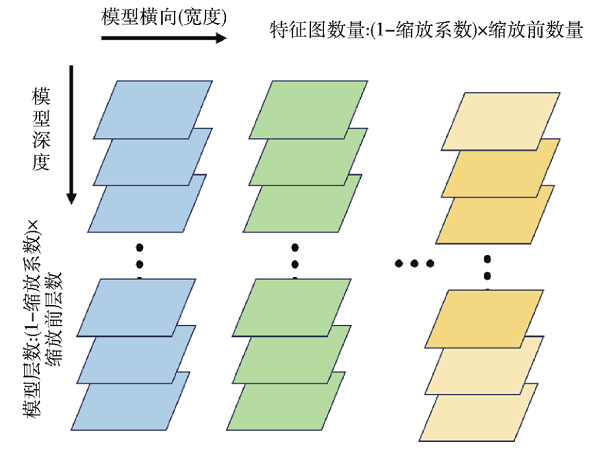

基于边缘算力和改进YOLOv10算法的智能垃圾分类系统[人工智能][其他]

发表于:2025/11/14 下午1:50:32