1 概述

LM12H458是高集成度的数据采集系统?DAS?芯片,它将采样保持、A/D转换集成在一块芯片内,从而大大减少了外围电路的设计。其8路模拟信号输入既可作为单端输入,又可两两组成差分输入。器件内部提供的一个2.5V参考电压、8×48bit指令RAM和32×16bit的FIFO大大减小了微处理器的负担。LM12H458的工作电压为3~5.5V,功耗小于34mW,待命模式下的功耗只有50μW。此外,LM12H458还有如下主要性能:

●有三种工作模式:分别为带符号的13位模式、带符号的9位模式和看门狗模式;

●有8个模拟信号输入通道,模拟信号可单端输入,也可差分输入;

●内置采样保持和2.5V参考电压;

●内含32×16bit的FIFO;

●采样时间和转换速率可编程;

●具有自校准和诊断模式;

●带有8位或16位数据总线。

2 引脚功能和功能说明

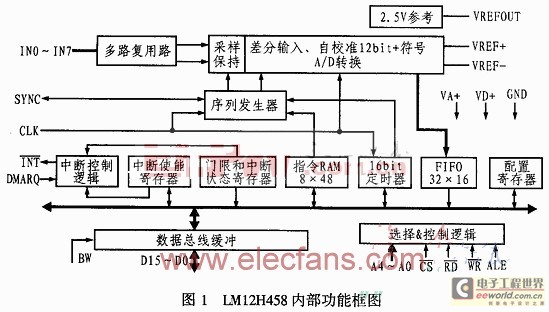

LM12H458的引脚功能如表1所列。图1为其内部功能框图。LM12H458是一个多功能数据采集系统,其内部的电荷重分配ADC采用电容梯形网络代替普通的电阻梯形网络,并使用逐步逼近寄存器的DAC使VREF-和VREF+之间产生一个中间电压,该电压与输入的采样电压相比较可产生数字输出的每一位,中间电压的个数和比较的次数对应于ADC的分辨率,通过校准ADC中的电容网络可校准数字输出的每一位精度。LM12H458有两种不同的校准模式:一种是补偿偏移电压或零误差,在该模式下只测量一次偏移误差,并依此建立修正系数;另一种为修正偏移误差和ADC线性误差,称为全校准。将该模式下的偏移误差测量八次,并取平均值即可建立修正系数。上述两种模式的修正系数被存贮在内部的偏移修正寄存器中。LM12H458的线性修正是通过修正内部DAC的失配电容获得的,在LM12H458内部ROM中存有校准算法,可对每一个电容校准8次并取平均值,从而产生线性修正系数。一旦校准后,内部算术逻辑单元(ALU)即可使用偏移误差修正系数和线性修正系数来修正每一次的转换结果。看门狗模式用于监控单端输入或差分输入信号的幅值。每个采样信号都有上下两个门限,输入信号高于或低于某一门限值都会产生中断。

表1 LM12H458的脚符号及功能

| 引脚号 | 符 号 | 功 能 |

| 1,12 | VA+,VD+ | 模拟电源和数字电源 |

| 2~11,13~18 | D0~D15 | 双向数据总线,总线宽度由BW决定。BW=1,总线宽度为8bit,BW=0,总线宽度16bit |

| 19 | RD | 读信号输入 |

| 20 | WR | 写信号输入 |

| 21 | CS | 片选输入 |

| 22 | WR | 地址锁存,用于总线复用的系统中 |

| 23 | ALE | 外部时钟输入,频率范围为0.05MHz~10MHz |

| 24~28 | A0~A4 | 地址线 |

| 29 | SYNC | 同步输入/输出,当配置寄存器的“I/O选择”位清零时,SYNC为输入;而当“I/O选择”位置为1时,SYNC为输出。 |

| 30 | BW | 总线宽度设定位,BW=1时,总线宽度为8bit,BW=0时,总线宽度为16bit |

| 31 | INT | 中断输出,低电平有效 |

| 32 | DMARQ | DMA请求输出,高电平有效 |

| 33 | GND | 接地 |

| 34~41 | IN0~IN7 | 模拟信号输入通道 |

| 42 | VREF- | 负参考电压输入,电压范围为0~VREF- |

| 43 | VREF+ | 正参考电压输入,电压范围0~VA+ |

| 44 | VREFOUT | 内部2.5V参考电压输出 |

LM12H458是一个多功能数据采集系统,内部有28个16bit的寄存器,各个寄存器的功能如下:

配置寄存器是DAS的控制中心,可用于控制序列器的启动和停止、复位RAM指针和标志、设置待命状态、校准偏移和线性误差、选择RAM区等。

指令RAM分为三个区:指令区、门限1区、门限2区。每一条指令(48bit=3X16bit)分散在三个16比特字宽的RAM区中,三个区的选择可由配置寄存器2bit的RAM指针来控制。指令区可设置通道的选择、工作模式、采样时间和循环位。其它两个区用于设置上下门限值。DAS可从指令0连续执行所有设置的指令,执行的最后一条指令的循环位为1时,再返回到指令0。指令执行期间,微处理器不能访问指令RAM,只有处理器终止指令循环后才可访问。

FIFO为只读寄存器,可用于存储转换结果。

中断使能寄存器可使用户激活8个中断源,该寄存器的高字节与中断1、2有关。

图2 LM12H458与80C51的接口电路 点击放大

中断状态寄存器和门限状态寄存器用于指示DAS中断源和输入信号是否超过上门限或下门限。

定时寄存器用于设置指令执行前的等待时间。而指令寄存器的bit9可使能或禁止插入等待时间。

LM12H458有8个中断源,各中断具有同等的优先级别,中断使能寄存器可使能或禁止相应的中断,当发生中断时,中断状态寄存器相应的位置1。各个中断对应的功能如下:

●INT0:模拟输入信号在规定的门限值以外产生中断。

●INT1:序列发生器执行到某条指令时,该指令地址等于中断使能寄存器中bit8~bit10设定的值时,产生中断。

●INT2:A/D转换的结果保存在FIFO,当FIFO中转换结果的个数等于中断使能寄存器比特11~15中设定的值时,产生中断。

●INT3:完成单次采样自动校准后产生中断。

●INT4:完成一次完整的自校准后产生中断。

●INT5:执行时,指令暂停位为1时产生中断。

●INT6:电源指示中断,当芯片供电电压小于4V时,产生中断。

●INT7:在从等待模式返回10ms后产生中断。

图3 编程流程图 点击放大

3 应用

3.1 硬件电路设计

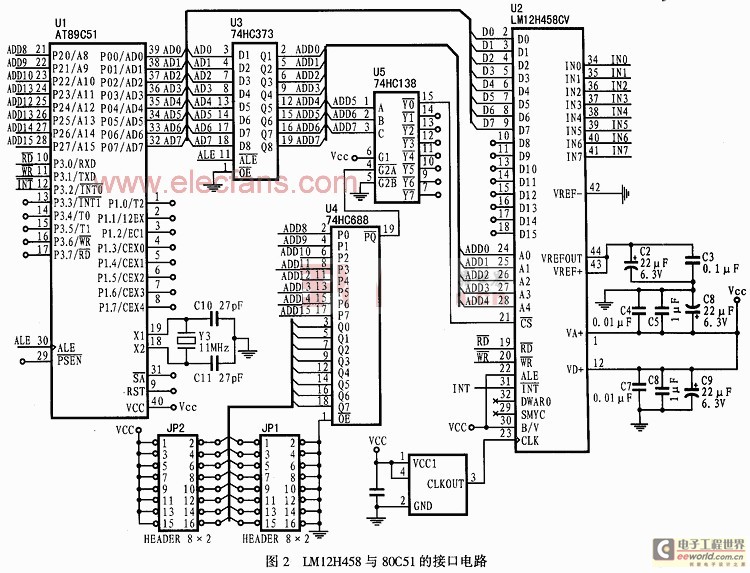

LM12H458灵活的总线接口简化了与多种微处理器的接口,它既可与8位处理器相连,又可方便地与16位微处理器相连。图2为AT89C51与DAS的接口电路图。该电路采用全地址译码方式来产生DAS的片选信号CS,其DAS映射的地址空间为0000-001F,数据总线宽度为8bit。图中的74HC373用于锁存低8位地址,而8bit幅度比较器则可用来对高8位地址进行译码,通过比较地址与地址范围所选择的输入逻辑可产生U5(74HC138)的选通信号,74HC138的Y0可作为DAS的片选信号。DAS的INT端口用于驱动AT80C51的中断INT0,同时它还允许DAS请求中断服务。

3.2 软件编程

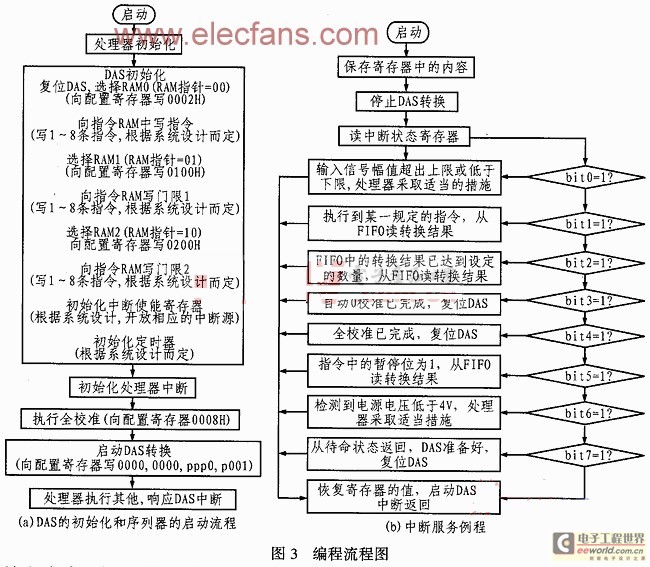

LM12H458虽然应用灵活、广泛,但基本的工作流程不变,图3为其典型的编程流程。在处理器初始化后,应向DAS写入合适的指令以初始化DAS,以便设置采样时间、工作模式、通道选择等。完成一次全校准需要4944个时钟周期,若设置中断使能,校准后应产生中断以通知微处理器。全校准会影响DAS的内部标志和指针,从而影响指令的执行。因此校准后必须复位。将配置寄存器的bit0设置为1可启动序列器。流程图中的p表示用户定义的不同工作模式。图3(a)为DAS的初始化和序列器的启动流程,图3(b)为中断服务例程。当进入中断服务后,配置寄存器的bit0应清零以停止A/D转换,然后处理中断事务。

4 结论

LM12H458数据采集系统芯片功能强大、应用灵活,可广泛用于数据记录、测量仪器、惯性制导、过程控制、能源消耗管理等方面。由于篇幅所限,本文仅作简单介绍,有关LM12H458的详细技术资料可在National Semiconductor的网站上获得。笔者已将LM12H458用于PI网络石英晶体元件的测试系统中。使用证明:LM12H458的转换精度很高,而且工作稳定可靠。