在电子工程、资源勘探、仪器仪表等相关应用中,频率测量是电子测量技术中最基本最常见的测量之一,频率计也是工程技术人员必不可少的测量工具。但是,传统的频率测量方法在实际应用中有较大的局限性,基于传统测频原理的频率计的测量精度将随被测信号频率的变化而变化,传统的直接测频法其测量精度将随被测信号频率的降低而降低,测周法的测量精度将随被测信号频率的升高而降低。本文中提出一种基于ARM与CPLD宽频带的数字频率计的设计,以微控器STM32作为核心控制芯片,利用CPLD可编程逻辑器件,实现闸门测量技术的等精度测频。

本设计的技术指标:

测频范围:1Hz~200MHz,分辨率为0.1Hz,测频相对误差百万分之一。

周期测量:信号测量范围与精度要求与测频功能相同。

占空比测量:准确度99%。

计数范围:0~1000000000,可手动暂停、复位。

功耗大小:5V×250mA= 1.25W。

等精度测频原理

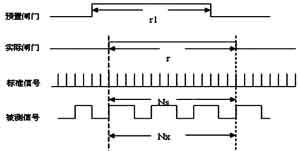

常用的直接测频方法主要有测频法和测周期法两种。测频法就是在确定的闸门时间Tw内,记录被测信号的变化周期数(或脉冲个数)Nx,则被测信号的频率为:fx=Nx/Tw。测周期法需要有标准信号的频率fs,在待测信号的一个周期Tx内,记录标准频率的周期数Ns,则被测信号的频率为:fx=fs/Ns。这两种方法的计数值会产生±1个字误差,并且测试精度与计数器中记录的数值Nx或Ns有关。为了保证测试精度,一般对于低频信号采用测周期法,对于高频信号采用测频法。但由于测试时很不方便,又提出了等精度测频方法。等精度测频方法是在直接测频方法的基础上发展起来的,它的闸门时间不是固定值,而是被测信号周期的整数倍,即与被测信号同步。 等精度测频系统的控制时序图如图1所示。

图1 等精度测频系统的控制时序图

在测量过程中,有两个计数器分别对标准信号和被测信号同时计数。首先给出闸门开启信号(预置闸门上升沿),此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才真正开始计数。然后,预置闸门关闭信号(下降沿)到来时,计数器并不立即停止计数,而是等到被测号的上升沿到来时才结束计数,完成一次测量过程。可以看出,实际闸门时间r与预置闸门时间r1并不严格相等,但差值不超过被测信号的一个周期。设在一次实际闸门时间r中,计数器对被测信号的计数值为Nx,对标准信号的计数值为Ns,标准信号的频率为fs,则被测信号的频率如式(1)所示。

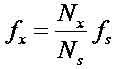

(1)

(1)

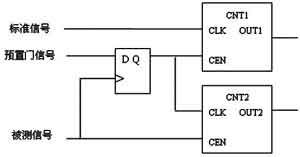

图2为等精度测频逻辑框图,CNT1和CNT2是两个可控计数器,标准频率信号fs信号从CNT1的时钟输入端CLK输入,经整形后的被测信号fx从CNT2的时钟输入端CLK输入。每个计数器中的CEN输入端为时钟使能端,控制时钟输入。当预置门信号为高电平(预置时间开始)时,被测信号的上升沿通过D触发器的输出端,同时启动两个计数器计数;同样,当预置门信号为低电平(预置时间结束)时,被测信号的上升沿通过D触发器的输出端,同时关闭计数器的计数。

图2 等精度测频逻辑框图

系统硬件设计

使用ST公司的32bit处理器STM32F103C8作为主控芯片与高可靠性的可编程逻辑器件EPM240T100C5结合设计成频率计。

STM32F103C8的功能特点如下:(1) 最高频率可达72MHz,自带128/64KB的FLASH,1.25DMIPS/MHz,可以访问0等待周期的存储器。(2)供电电压范围为2.0~3.6V了,内嵌8MHz高速晶体振荡器,也可外部时钟供给,本系统采用CPLD时钟分频供给。(3)下载模式可采用串行线调试(SWD)接口和JTAG接口,本系统采用JTAG下载接口。

EPM240T100C5的功能特点如下:(1)支持内部时钟频率300MHz,本系统使用有源晶振50MHz供给。(2)片内电压调整器支持3.3V、2.5V或1.8V电源输入,本系统使用3.3V电压供给。(3)下载模式使用10针JTAG接口。

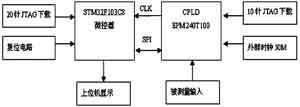

1 系统硬件结构框图

系统通过对STM32F103C8微控器的控制,经SPI总线向CPLD芯片EPM240T100发送数据和命令来控制内部逻辑单元。EPM240T100使用外部有源晶振50MHz供给,经4分频12.5MHz作为CPU的输入时钟。该系统的硬件结构如图3所示。其包括主控芯片模块、JTAG下载模块、复位电路模块、上位机显示模块、被测量输入模块。

图3 系统框图

2 系统的数字电路设计

微控器原理如图4所示。本系统处理器使用STM2F103C8,时钟由CPLD分频供给CPU,通过SPI方式将数据和命令传送给CPLD,而后用串口RS232发送到上位机显示。

图4 微控器原理图