尽管当前趋势全部集中一个方向——设计者需要使用A/D转换器时通常选定一个集成的A/D转换器(ADC)。大多数工程师并没有意识到还有降低ADC性价比的其它替代方案。而模拟比较器、D/A转换器(DAC)和信号处理一起恰好就是构成逐次逼近ADC的核心电路。

在某些特定领域,分立比较器/DAC的使用非常普遍。自动测试设备、核脉冲反应堆高度监测器以及自动化时域反射计等,通常都采用这种技术,DAC用于驱动比较器的一个输入,另一个输入由被监测信号驱动。接下来是通用测试问题以及特定方法的选择,事实上,此时采用比较器/DAC组合比采用现成的ADC更受欢迎。

瞬态电压分析

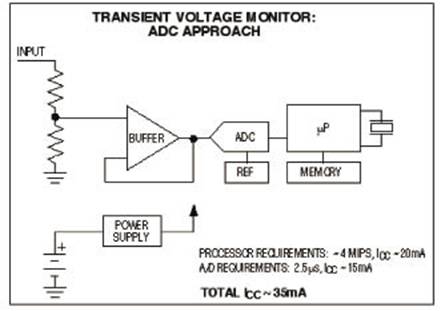

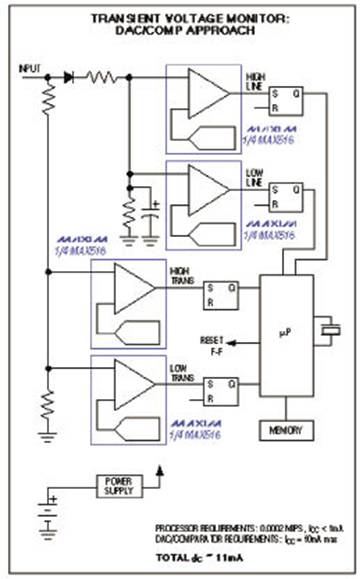

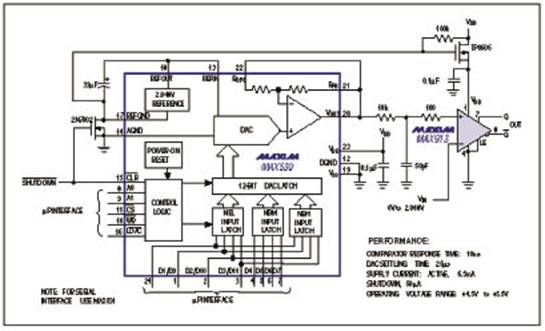

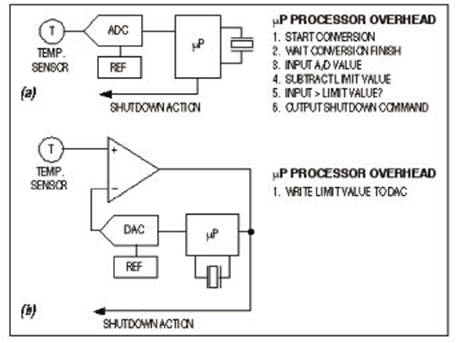

捕获快速幅度变化事件(瞬态)的“强力”技术就是采用处理器支持的高速ADC和RAM对其进行简单量化(图1)。单触发事件可能必须采用这种方法,因为需要获取瞬态细节。然而,如果瞬态是重复性的,则可采用DAC/比较器的方法测量它们的峰值幅度及其它特性(图2)。

比较器的一个输入引脚由DAC设置判定电平,瞬态信号施加到另一个输入。通过调整DAC输出可确定峰值瞬态幅度。超越门限时,采用数字锁存捕获比较器的输出响应。仅需要比较器输入支持瞬态带宽,任意长的DAC输出建立时间并不会影响测量精度。这样,在模拟域可用低成本DAC和比较器代替昂贵的ADC。

图1 采用“强力” 法进行瞬态分析,ADC电路耗电大且价格昂贵

图2 如果图1应用可接受对幅度进行重复测量,用DAC/比较器组合替代ADC可省电并降低成本。

需注意的是,在监视模拟电压时必须考虑容限。许多自诊断设备监视系统电压、温度以及其它模拟量,容限值在软件中设置。然而,如果这种比较由比较器实现,设置值由DAC提供,这样可减轻处理器负荷,因为只需要读取一位来表示超限状态。

这种技术(模拟域比较)与ADC技术(数字域比较)具有相同精度,对于一个设置点时,可通过简单比较实现,为什么还要对整个值进行量化?必须提及的一种情况是:如果与几个设置点进行比较时,例如报警上限/下限和关断的下限/上限电平,可选择ADC,否则需要4路DAC和4个比较器。

由DAC构建简单的ADC

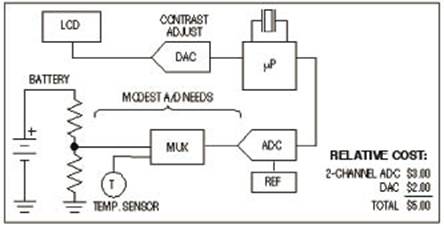

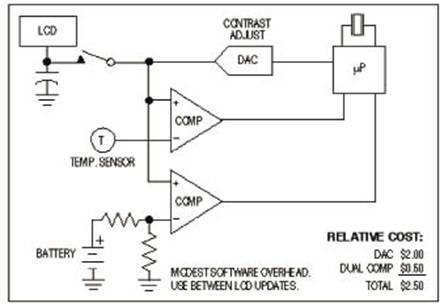

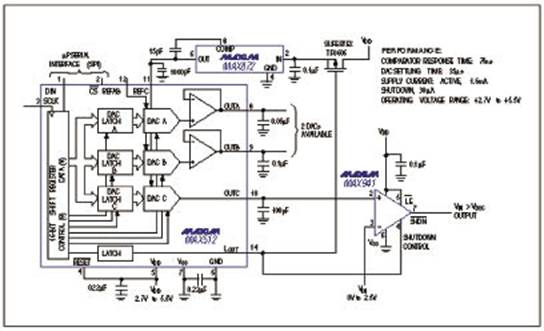

便携式仪器受成本和尺寸限制,有些情况下可以利用DAC实现A/D转换功能。例如,蜂窝电话和医疗电子通常采用DAC调整LCD对比度电压(图3)。有时可通过简单添加一个比较器和开关,监视温度或电池电压(如上所述)。那么现有DAC可执行两种任务,在DAC执行模拟至数字转换时关闭显示器。作为另一种替代方案,由模拟开关和电容构成的简单采样/保持电路(图4)可在A/D转换期间维持LCD的对比度电压。

图3 该电路常见于便携仪器

图4 对图3增加两个比较器,由DAC实现ADC功能,节省成本。

另外一种方法就是用一个低成本双路DAC替代现有单路DAC。双路DAC中的一路用于产生LCD对比度电压,另一路用于构成ADC。无论单路还是双路,都需要DAC和比较器支持快速、驱动DAC的简单程序,以及对比较器采样来实现逐次逼近。

设计考虑

DAC和比较器的结合非常简单。信号作用到比较器的同相输入端,DAC提供的数字可编程门限作用到反相输入端。只要信号比门限值大,比较器就会产生逻辑高电平输出。但在使用时必须注意几个方面:

为确保精确的门限电平,考虑到比较器的输入偏置电流以及比例网络,DAC的直流输出阻抗应很小。在超低功耗电路中更应注意,DAC的输出阻抗可能高达10kΩ。

DAC的另一个要求是低交流输出阻抗。否则,比较器输出的高速数字信号的压摆率经过布线寄生电容耦合,将产生输入瞬态变化,导致自激并降低精度。如果允许牺牲一定的建立时间,可在比较器输入端增加一个旁路电容来降低DAC的交流输出阻抗。DAC输出放大器的大电容负载可导致不稳定或振荡,但这个问题可在DAC输出串联一个电阻加以修正。

比较器的主要问题是滞回。大多数比较器电路带有滞回,以防止噪声和振荡,但使用滞回时必须谨慎——它会造成门限值随输出而改变。如果系统可对受输出状态影响的滞回进行补偿,可以接受这种配置;否则,应当避免滞回。

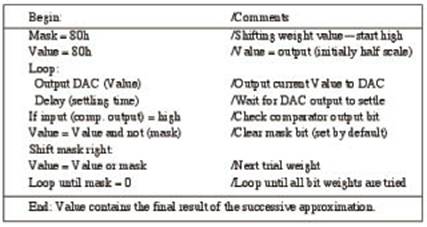

如果采用的比较器具有内部滞回并且不能禁止,可确保DAC输出总是在相同方向逼近比较器门限,这样可消除负面影响。通过在每位测试完成后将DAC设置为零,便于达到这一目的;例如,在本文最后列出的伪代码后增加一行。

另一选择是,通过增加一个小电容反馈也可消除滞回,这会加速比较器在线性工作区的转换。或者,增加一个输出触发器或锁存器,在给定时刻捕获比较器输出状态。

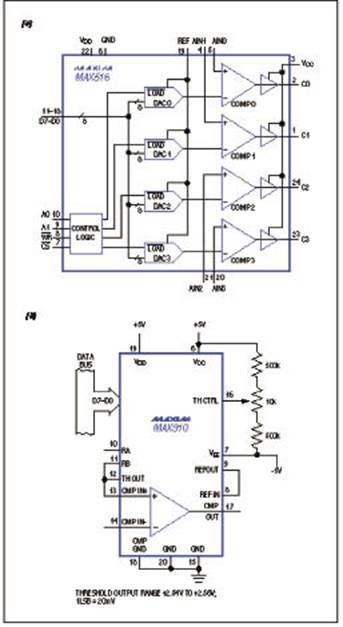

当前比较器都能够很好地处理摆率受限的输入信号。例如,Maxim公司的MAX913和MAX912在这方面尤其有效,因为它们在线性工作区能够确保稳定。图5列举了MAX913在高速、12位应用中的性能。图6电路(超低功耗8位转换器)在不使用时可将其关闭以节省能量。

图5 由于比较器在其线性工作区保持稳定,该高速、12位幅度采集器可处理低速输入电压。

图6 该低电压、8位数据采集器替代ADC具有几个优势:低成本、低功耗、以及采样间隔期间关断功能。

DAC/比较器组合IC

Maxim提供3款单芯片器件可大大简化设计,这些芯片组合了比较器和DAC。每款器件都非常适合本文应用及其它多种应用。

例如,MAX516是一款4通道器件,具有亚微秒速度,非常适合多种中等速度、多通道应用(图7a)。

MAX910是单通道、高速、TTL输出DAC/比较器,具有8ns传输延迟(图7b)。类似器件(MAX911)具有更高速度——ECL互补输出、4ns传输延迟。

图7 Maxim 8位DAC/比较器IC包括4通道MAX516(a)、高速、TTL兼容MAX910(b)、以及ECL兼容MAX911(未列出)

逐次逼近

逐次逼近采用天平和一系列用于确定物体重量的二进制权重(权重相对值为1、2、4、8、16等)的方式很容易说明。确定一个未知重量的最快方法(逐次逼近),首先,将未知重量与最大权重进行比较。根据天平指示,要么移除该重量,要么增加下一个最大重量,按这种方式一直到最小的权重。物体的重量就是天平盘上剩余权重的总和。

在逐次逼近ADC中,内部DAC的位模拟系列二进制重量,比较器输出模拟天平指示。驱动权位处理的逻辑保存在封装好的ADC的逐次逼近寄存器(SAR)或者控制DAC/比较器电路的处理器软件子程序,该子程序可由不到20行的代码来实现(表1)。

应用

本章节列举了DAC/比较器架构和集成ADC相比所具备的优势。所讨论的应用电路既常见又简单,也存在一些共性问题。

首先,考虑采用低成本方法实现电力线电压跌落、浪涌以及瞬态检测和故障记录。理想的设计是采用墙上设备监测电力线异常,并将每次异常发生的时间记录到RAM中(电压跌落和浪涌的持续时间可以从几毫秒到几小时;瞬态可能短至10微秒)。监视器必须记录电力线完全失效的持续时间,因此,监视器应当由电池供电。

传统解决方案是采用控制器和ADC。由于转换器连续对电力线电压采样,控制器需将每次采样值与软件中用户设定的限制进行比较,并将任何超出规定的状态记录到RAM。由于系统必须能够追踪到短至10µs的瞬态情况,ADC采样间隔必须相当短——保守估算时间可以长达2.5µs。因此,控制器必须以1/2.5µs = 400ksps的速率进行采样处理。

如果软件比较具有高效编码并且ADC无需处理器干预,系统每次采样可执行少于10条指令,这就要求处理器具有4MIPS的能力。这种执行能力并不适合采用电池供电(图1)。需要考虑用模拟方法对输入瞬态偏离进行响应,用以替代连续跟踪方案。

在这种情况下,DAC/比较器替代方案提供了几个明显优势。需要4个DAC和4个比较器(或一片MAX516),后面连接一个4路设置/复位触发器。一组DAC/比较器/FF监测高瞬态电压,一组监测低瞬态电压,一组用于监测电网跌落,一组用于监测浪涌(图2)。瞬态电压直接耦合到比较器,连接到电压跌落和浪涌监测比较器的输入首先要进行整流和滤波,以获得电网电压的平均值。可在软件中调整到合适的rms。

系统每T秒进行采样并对触发器复位,此处T为瞬态记录时间分辨率(也许为60s)。高、低瞬态电平DAC用于设置所要求的门限。电压跌落和浪涌DAC在每T秒间隔后进行调整,采用逐次逼近技术产生高、低门限,以跟踪目前平均值。

假设执行逐次逼近以及其它任务的子程序具有1000条指令(保守估计),对于T=60s,CPU平均每秒执行17条指令。执行速率是0.00002MIPS,非常适合低功耗系统,远远低于ADC方案的4MIPS。为进一步降低功耗,控制器可在大部分时间内处于“休眠”,仅在处理电力线异常时唤醒。将电压比较从软件方式转换为模拟硬件方式,该电路大大降低了功耗、设计复杂性以及成本。

较低的故障检测和诊断维护成本

打印头控制、车辆控制以及许多其它机电应用,需严格监视内部电压和温度以确定何时更换工作模式。极端情况下,这种反馈可使系统避免全部关断自毁。例如,在必要时步进电机控制器必须调整输出MOSFET的栅极驱动以避免线性工作时消耗过多功率。

监测这些问题的传统方法是采用ADC(图8a)。处理器控制ADC进行周期性测量,与控制处理保持时间常数一致。然后对结果的量化值进行缩放后与软件中的门限进行比较。如果超出范围,可触发纠正动作或者全部关断系统。

另外一种方法是采用DAC/比较器组合(图8b)。静态DAC输出建立关断门限或比较器触发值。当温度变化造成比较器触发,比较器会对处理器发出中断来启动纠正动作。必要时,处理器还可以通过启动基于软件的逐次逼近程序来确定极限温度值。

表1 逐次逼近伪代码

图8 在这种情况下,用DAC和比较器(b)替换ADC(a)可降低系统成本、响应时间以及软件开销

另一方面,为支持ADC,处理器在跳转到关断子程序之前必须轮询ADC、输入采样值并与先前设定值进行比较。这样,DAC/比较器不仅节约成本,而且提供了比采用ADC的更快响应;同时还减小了处理器开销。

时域反射计

最后,低成本、低功耗DAC/比较器组合(相对于ADC)在便携式时域反射计(TDR)中非常实用,后者是一种用于检测电缆的不连续性并可测量中间传输长度的仪器。廉价的便携式TDR随着网络电缆的增加变得非常普遍。

TDR工作原理类似于雷达,沿着线缆发送一个主脉冲并监测由开路、短路、或者其它电缆阻抗不连续产生的反射。发射脉冲及其反射波传输延时间隔大约为每英尺3.3ns,假设线传输速率为0.6c(光速的十分之六)。那么,在电子学上10ns时间分辨率可分辨出大约3英尺距离的不连续性。

接收到的脉冲幅度和发送脉冲幅度的比用于计算反射系数。知道反射系数和电缆阻抗就可以计算不连续阻抗,从这些信息可推断出不连续的原因。同轴电缆在反射回路上对脉冲的衰减使其变得复杂,因此,软件必须对此进行补偿,通常根据测量距离施加一个幅度修正。

本应用中的ADC必须每个5ns转换一次(200Msps)。尽管厂商可以提供这种ADC,但价格非常昂贵,而且功耗大,通常不适合便携式应用。

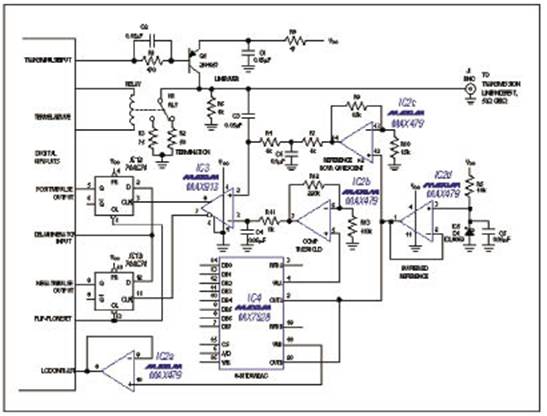

实际应用中的手持式TDR模拟前端(图9)能够说明上述观点。为了便于说明,这里没有包括数字电路。尽管简单并且没有特殊元件,该电路仍具有很好性能。能够可靠地测量端接阻抗并且对于500英尺长的电缆具有5%测量精度。可测量长达2000英尺的开路或短路故障。重要的是,系统(包括显示和数字电路)可在9V碱性电池下工作长达20小时。

图9 该时域反射计的模拟部分采用DAC/比较器代替ADC

图9中比较器(IC3)采用单电源供电、地电位检测以及仅10ns传输延迟。DAC(IC4)为双通道器件,一方面用于脉冲高度测量,另一方面驱动LCD对比度控制(如图3)。注意DAC为反向驱动;电流输出端连接在一起由经过缓冲的电压基准驱动,基准输入作为电压输出(每路带有一个外部放大器缓冲)。

利用简单的脉冲单稳态电路(没有列出)驱动Q1基极,利用正向、持续时间为10ns的脉冲依次驱动电缆。电缆的所有反射通过C3耦合到比较器。

IC5为1.2V输出带隙基准,由放大器IC2d缓冲,为IC4双路DAC提供基准电压。该基准电压被IC2c两倍增益放大器放大后,为比较器同相输入提供2.5V直流电平。DAC A在比较器反相输入端施加一个0至3.8V电压。高于2.5V的电平用来判断正向脉冲高度,低于2.5V的电平用来判断负向脉冲幅度。

每个输入到传输线的脉冲还经过了数字电路可变延迟线,该延迟线是由计数器控制的20ns延迟单元串接而成。来自数字部分经过延迟的脉冲驱动两个触发器(IC1a和IC1b)的D输入端,触发器由比较器互补TTL输出轮流触发。这样,时间测量取决于返回脉冲和通过延迟线脉冲的竞争:如果D输入比时钟变化到来得早,触发器输出为高;否则,输出为低。

测量时,将DAC输出设置为最低值并重复调整延迟,直到触发器输出保持为零,读取计数器。同样,测量返回脉冲高度时,重复调整DAC输出直到触发器输出保持为零,然后读取DAC。注意,两个触发器需要捕获正脉冲和负脉冲的前沿。前沿是指正脉冲的上升沿和负脉冲的下降沿;如果两个脉冲施加到一个触发器,脉冲宽度可能产生人们所不期望的延迟。